Параллельно-последовательный аналого-цифровой преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

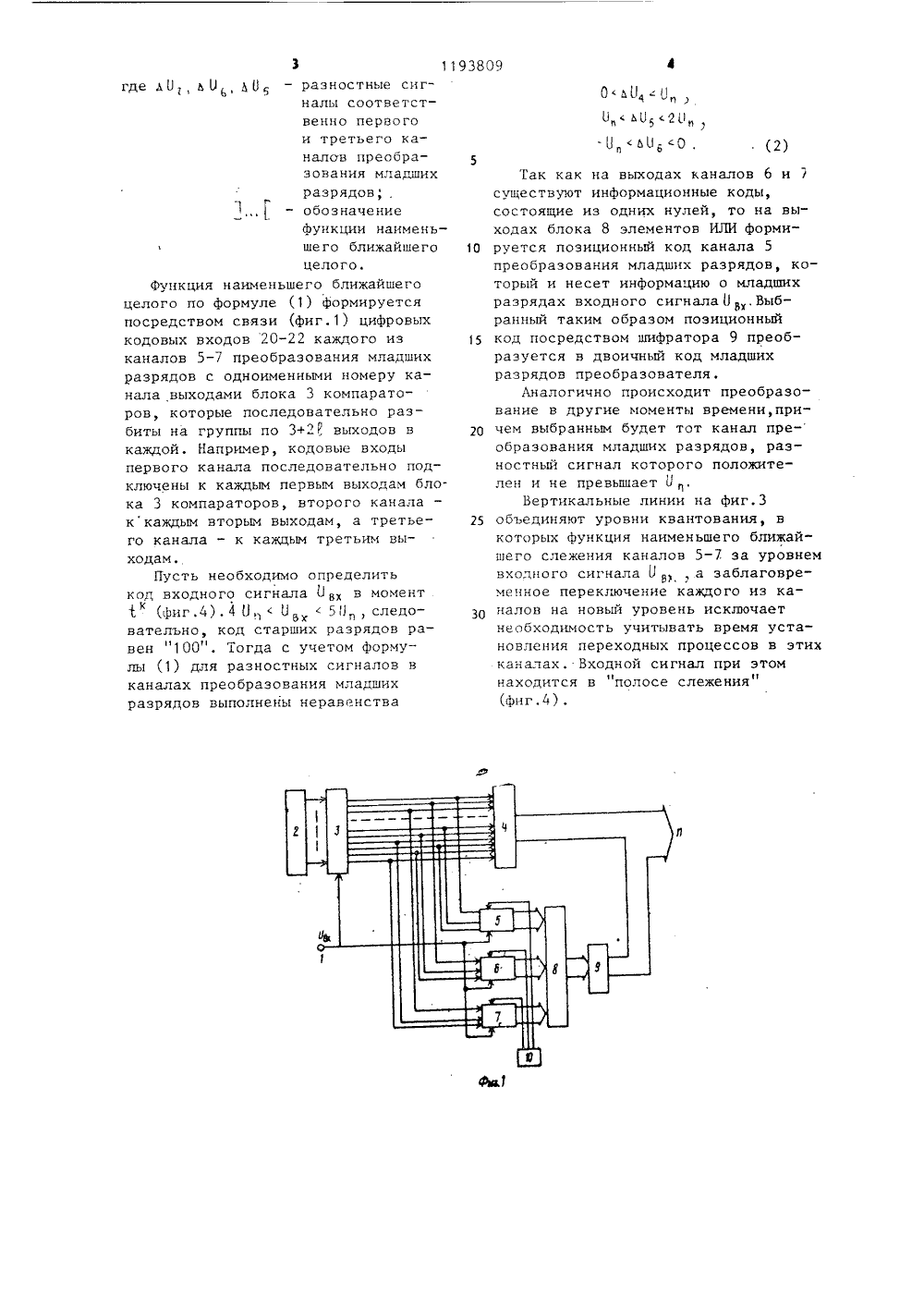

(21 (22 блока компараторо разования младших аналоговые входы образования младш динены с сигцальн компараторов кана а преобов, причемналов преядов объеом блокабразованця в кана. разря сех к лощенк цх разр ым вход ла и гори Ряза тарших разряда ай шиной, и ис И ЯВЛЯЮТСЯ ВХОД чник опорных сцг а ю щ и и с я темьшенця погрешносс. 20 (54) ( 11 ЬЙ А информации, вэлементов ИЛИ инаго када в двоичаго являются одер надшц разрядов, тветствуютов ИЛИ, с выходам преобразо- дополни эдемединень и омп анало рядов е вхо к вация младших ра тельные аналогов ми шинами старших- 3,5,7) каналападших разрядов,х выполнен на фор являются выходн разрядов, 11 ( и преобразования орых ыи из кото оследовательно сое енных и ний, блокеунитарноточнике эталонных компараторов и ши пр ратор ный, дами х ра ходы выходы котоканала прерядов, аналого кода в позрого являются ио выхо вация младши и цифровые вабра то ов налоговым мирователя ия выход ко нальному вхоразнос го напряж лючец к с о го по ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ 3680630/24-2427,12.8323.11,85. Вюл. 11 43Л.П. Петренко и С.А, Во о 681.325 (088,8)Статистические измерения и алмизация измерений. Вып. ь, 1978, с. 70-78, рис. 3. хтиаров Г,Д. и др. Аналоговые преобразователи.,1 1980, О, рис, 7.24.57) ПАРАЛЛЕЛЬ 110-Г 10 СЛЕДОВАТЕЛЬПАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ жащий канал преобразования их разрядов, выполненный ца довательцо соединенных источэталонных напряжений, блоке раторов и шифраторе унитарного в двоичный, В выходов которого мирователе разцостного напряжения ляются соответственн цифровым входами фор налов, о т л и ч что, с целью умен тц преобразования него введены блок шифратор позцццоц цып выходы катар выходными шццамц а входы подключен щцм выходам блока входы котарога Га саотьстствуюших к подключсны к соответствующим выходам источника опорных сигналов и являются дополнительными анало говььги входами соответствующихравателей разностных напряж аналов преобразования младших разрядов, при этом , -й цифровой вход , -го канала преобразования младших разрядов, где 1,2, ,(2 - 1)/я,= 1,2 и подключен к соответствующему Г (1 - 1 )ц + Д-му выходу блока компараторов канала преобразования старших разрядов.."Ос(.т"1"Е ИСПО;Е) ЗоваНО Ь автоыст - ТИ сОса;я)Е И" 10)00 с;с(т 0(ЬИО ИЗМЕ )Пт";(Ь.1 Х т И ТСМа.ьег:1(т пзобрстец тц яется; т Но ; С т 3Пот т ) Паогипа бок . КО пара Ора : ":. с ацьи ;ата-, СЯ С. ЦаОЕ)0.)Га)01 гЫУ НаП 1 Я -)Сто:(иКЗ ат:0(тццц;ЦСРЯКЕНИИ (С С):ЕПОБ Д"тсе.,(ЬЦО С Е ЕЕ 5.= и; б;гКО(:;КОМ араторов Ет Ш (фраторо т - П 3 Ь" ена(151старших разр);.сц3 ка)г дОс Кана.ГЕ О - т ИСТОЧНИЕ т; ЗтаЛОННЫХ НаПРЯжЕНй ПОСЛЕДОВатЕЛЬНО СОЕ- геинен с блОкОЯкомпаратороп и яаефоатором4, Бьехоль шифратора 14 ЯЦ;ТЯЮТС Я ЦЬЕХОДасьтс. К сЯЦОГГ) каналов гереобрззоваыия младших рсЗЗЕ)НЕЕ,ОБ Э / . ццало Овца,т) К .(и(РРовгь(е 2 с) 22 вхои к,1(Лого из КЯ Н,"ЛОБ )-: ЯВЛЯ 3)сСЯ г.)г " гЕТЕ яет-.ПО аиаГ(ОГОВЬЩ И 1;И(т)РОЕЬЫ(И БХОЛа.:И3 1193809 где Ь О Ь 0 , Л О 5 - разностные сигналы соответст 0 дО-О,ОО, г 0,(2) венно первогои третьего каналов преобразования младшихразрядовобозначениефункции наименьшего ближайшегоцелого.Функция наименьшего ближайшего целого по формуле (1) формируется посредством связи (фиг,1) цифровых кодовых входов 20-22 каждого из каналов 5-7 преобразования младших разрядов с одноименными номеру канала выходами блока 3 компараторов, которые последовательно разбиты на группы по 3+21 выходов в каждой. Например, кодовые входы первого канала последовательно подключены к каждым первым выходам блока 3 компараторов, второго канала ккаждым вторым выходам, а третьего канала - к каждым третьим выходам.Пусть необходимо определить код входного сигнала (1 в момент(фиг,),4 цО5 Н следовательно, код старших разрядов равен "100". Тогда с учетом Формулы (1) для разностных сигналов в каналах преобразования младших разрядов выполнены неравенства Так как на выходах каналов 6 исуществуют информационные коды,состоящие из одних нулей, то на выходах блока 8 элементов ИЛИ форми 1 О руется позиционный код канала 5преобразования младших разрядов, который и несет информацию о младшихразрядах входного сигнала(1 .ВыбЬхранный таким образом позиционный15 код посредством шифратора 9 преобразуется в двоичный код младшихразрядов преобразователя.Аналогично происходит преобразование в другие моменты времени,причем выбранным будет тот канал пре-образования младших разрядов, разностный сигнал которого положителен и не превышает ОВертикальные линии на фиг.325 объединяют уровни квантования, вкоторых функция наименьшего ближайшего слежения каналов 5-7. за уровнемвходного сигнала 0, а заблаговременное переключение каждого из каналов на новый уровень исключаетнеобходимость учитывать время установления переходных процессов в этихканалах, Входной сигнал при этомнаходится в полосе слежения1193809 Войтовмезей Коррект оставительехред А.Кик Реда Бугир М, Лемчик з 7325/ Тираж 871 ВНИИПИ Государственно по делам изобретени 3035, Москва, Ж, Раугород, ул ектная.ц иал ППП Патент Подписноео комитета СС и открытийкая наб., д

СмотретьЗаявка

3680630, 27.12.1983

ПРЕДПРИЯТИЕ ПЯ В-2201

ПЕТРЕНКО ЛЕВ ПЕТРОВИЧ, ВОЛОЩЕНКО СЕРГЕЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: H03M 1/34

Метки: аналого-цифровой, параллельно-последовательный

Опубликовано: 23.11.1985

Код ссылки

<a href="https://patents.su/4-1193809-parallelno-posledovatelnyjj-analogo-cifrovojj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Параллельно-последовательный аналого-цифровой преобразователь</a>

Предыдущий патент: Аналого-цифровой преобразователь

Следующий патент: Многооборотный преобразователь углового перемещения

Случайный патент: Строительный раствор