Устройство для определения объема контролируемых параметров

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1168903

Авторы: Бороденко, Вишневский, Дударев, Назаренко

Текст

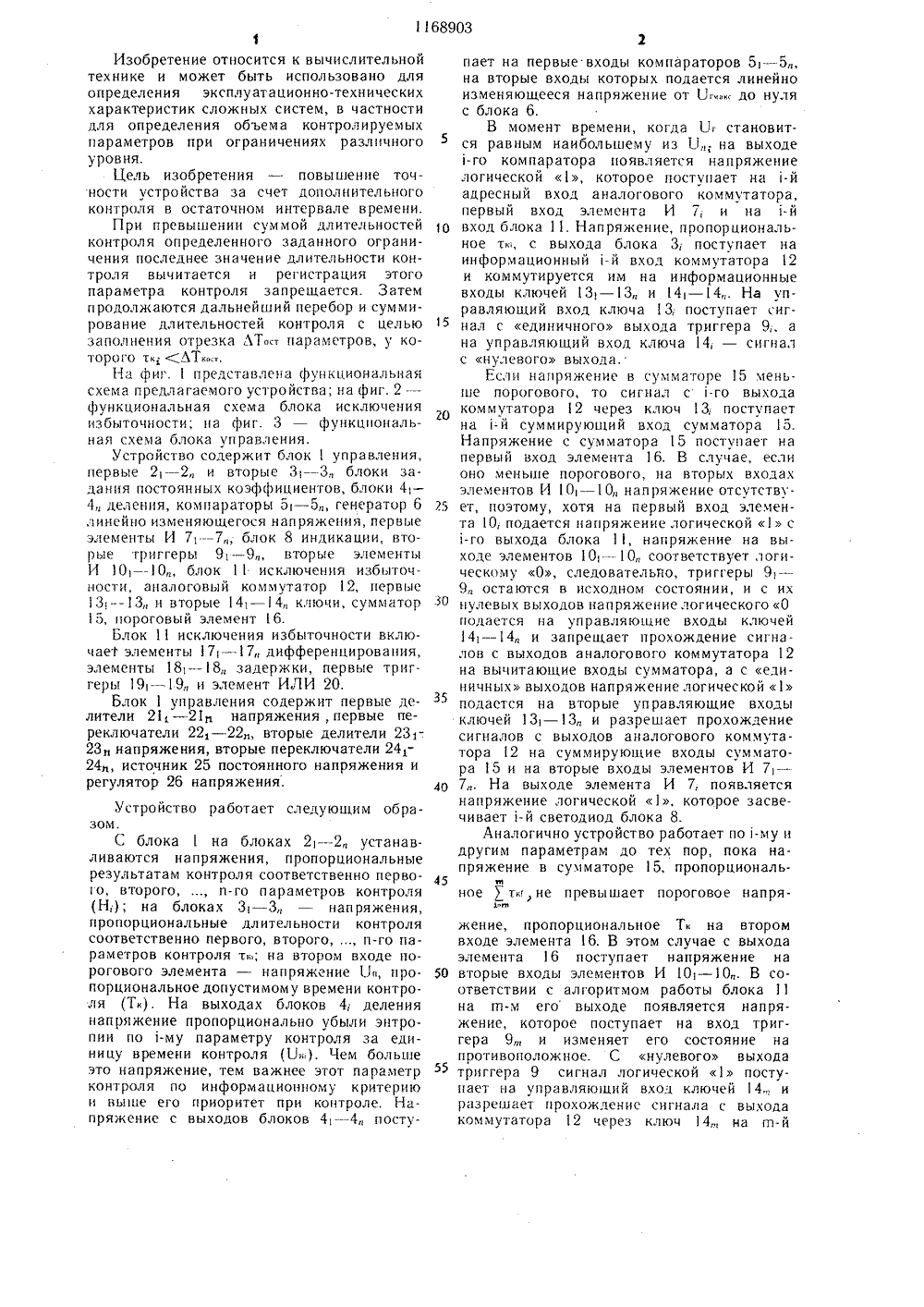

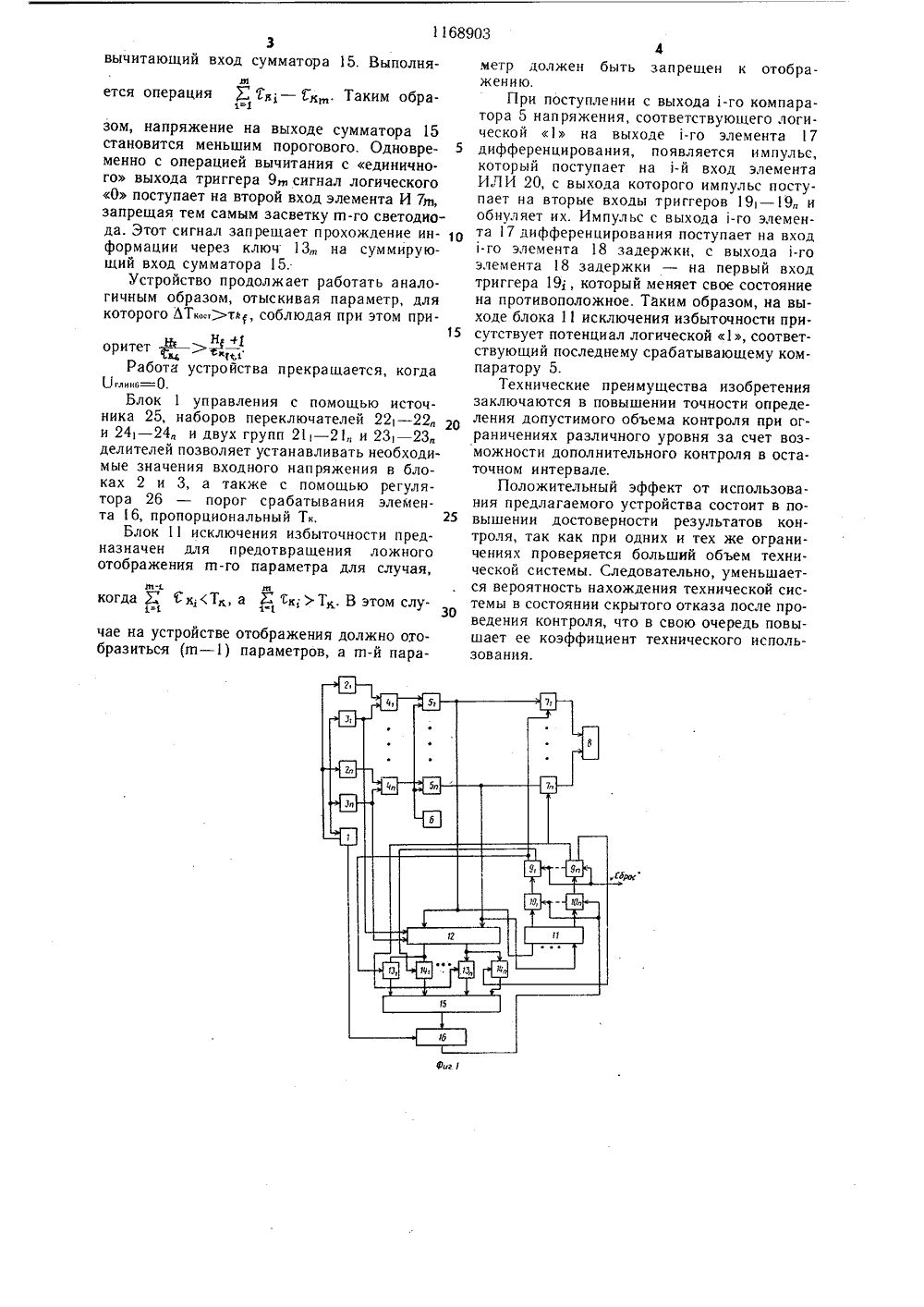

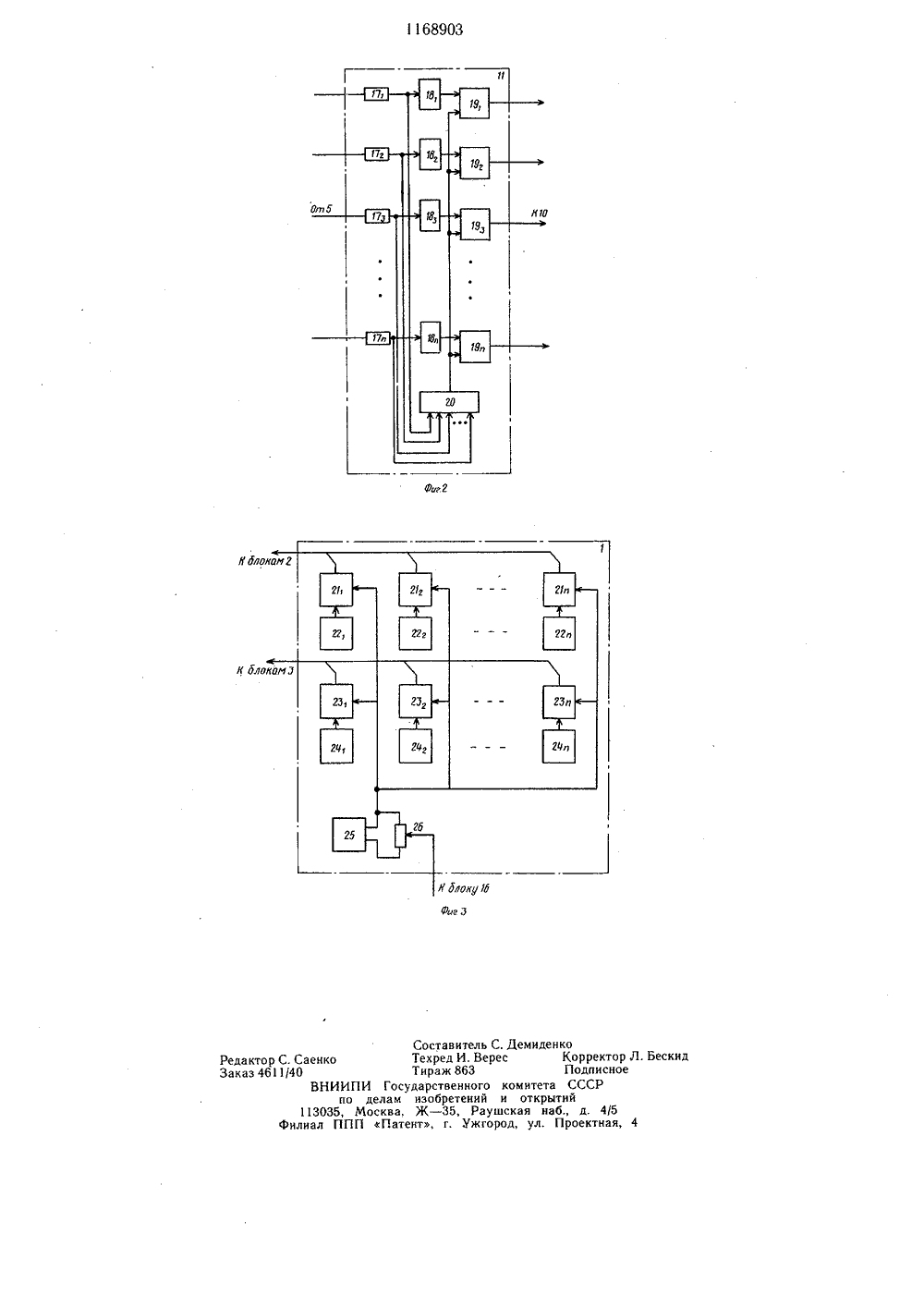

(51)4 мат а е юЧ:т этЩ -Г ЕНИ ОПИСАНИЕ ИЗОБРЕК А ВТОРСКОМУ СВИДЕТЕЛЬСТВ/02 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ(54) (57) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛ ЕН ИЯ ОБЪЕМА КОНТРОЛИ РУЕМЫХ ПАРАМЕТРОВ, содержащее первые и вторые блоки задания постоянных коэффициентов, сумматор, пороговый элемент, блоки деления, компараторы, генератор линейно изменявшегося напряжения, первые и вторые элементы И, блок индикации, блок исключения избыточности, состоящий из элементов дифференцирования, элементов задержки, первых триггеров и элемента ИЛИ, а также аналоговый коммутатор и блок управления, состояший из первых и вторых делителей напряжения, первых и вторых переключателей, источника постоянного напряжения и регулятора напряжения, причем выходы первых делителей напряжения объединены и связаны с входами первых блоков задания постоянных коэффициентов, выходы вторых делителей напряжения также объединены и подсоединены к входам вторых блоков задания постояйных коэффициентов, выход регулятора напряжения подключен к установочному входу порогового элемента, выходы первых блоков задания постоянных коэффициентов соединены с первыми входами соответствуюших блоков деления, выходы вторых блоков задания постоянных коэффициентов соединены с вторыми входами соответствуюших блоков деления и с соответствуюшими информационными входами аналогового коммутатора, первые входы компараторов соединены с выходами блоков деления, вторые входы компараторов - с выходом генератора линейно изменяющегося напряжения, а выходы компараторов - с первыми входами первых элементов И, с соответствуюшими адресными входами аналогового коммутатора и с входами соответствующих элементов дифференцирования, выходы первых триггеров соединены с первыми входами вторых элементов И, к вторым входам которых подключен выход порогового элемента, выходы первых элементов И связаны с входами блока индикации, а выход сумматора соединен с входом порогового элемента, выходы элементов дифференцирования подключены к входам соответствуюших элементов задержки и к входам элемента ИЛИ, выход которого связан с нулевыми входами первых триггеров, единичные входы которых соединены с выходами элементов задержки, выходы первых и вторых переключателей подсоединены к первым входам соответствующих первых и вторых делителей напряжения, вторые входы которых подключены к положительному выходу источника постоянного напряжения, через регулятор напряжения связанному с отрицательным выходом источника, отличающееся тем, что, с целью повышения точности устройства за счет дополнительного контроля в остаточном интервале, в него введены первые и вторые ключи, вторые триггеры, причем выходы вторых элементов И соединены с входами соответствующих вторых триггеров, единичные выходы вторых триггеров связаны с вторыми входами соответствующих первых элементов И, с управляющими входами соответствующих первых ключей, нулевые выходы вторых триггеров соединены с управляюшими входами соответствующих вторых ключей, выходы аналогового коммутатора связаны с информационными входами первых и вторых ключей, выходы первых ключей соединены с суммирующими входами сумматора, а выходы вторых ключей - с вычитаюшими входами сумма. тора.1Изобретение относится к вычислительнойтехнике и может быть использовано дляопределения эксплуатационно-техническиххарактеристик сложных систем, в частностидля определения объема контролируемыхпараметров при ограничениях различногоуровня.Цель изобретения - повышение точности устройства за счет дополнительногоконтроля в остаточном интервале времени.При превышении суммой длительностейконтроля определенного заданного ограничения последнее значение длительности контроля вычитается и регистрация этогопараметра контроля запрещается. Затемпродолжаются дальнейший перебор и суммирование длительностей контроля с цельюзаполнения отрезка ЛТост параметров, у которого т.; (ЛТ-,.На фиг.представлена функциональнаясхема предлагаемого устройства; на фиг. 2 -функциональная схема блока исключенияизбыточности; на фиг. 3 - функциональная схема блока управления,Устройство содержит блок 1 управления,первые 2, - 2 и вторые 3 - Зблоки задания постоянных коэффициентов, блоки 4 -4 деления, комлараторы 5 - 5, генератор 6линейно изменяющегося напряжения, первыеэлементы И 7; блок 8 индикации, вторые триггеры 9 - 9, вторые элементыИ 1 О - -10, блок 11 исключения избыточности, аналоговый коммутатор 12, первые13 13 и вторые 14 -4 ключи, сумматор5, пороговый элемент 16.Блок 11 исключения избыточности включае 1 элементы 17 -7 дифференцирования,элементы 18 - 18 задержки, первые триггеры 19 - 19 и элемент ИЛИ 20.Блок 1 управления содержит первые делители 21, - 21 напряжения, первые переключатели 22, - 22, вторые делители 2323 напряжения, вторые переключатели 24,24, источник 25 постоянного напряжения ирегулятор 26 напряжения.Устройство работает следующим образом.С блока 1 на блоках 2 - 2 устанавливаются напряжения, пропорциональные результатам контроля соответственно первого, второго, , и-го параметров контроля (Н,); на блоках 3 - 3 - нап ряжения, пропорциональные длительности контроля соответственно первого, второго, ., и-го параметров контроля т; на втором входе порогового элемента - напряжение и, пропорциональное допустимому времени контроля (Т) . На выходах блоков 4; деления напряжение пропорционально убыли энтропии по 1-му параметру контроля за единицу времени контроля (1;). Чем больше это напряжение, тем важнее этот параметр контроля по информационному критерию и выше его приоритет при контроле. Напряжение с выходов блоков 4 - -4 посту 68903 5 10 5 10 5 ЗО 35 4 О 45 пает на первые входы компараторов 5 - 5., на вторые входы которых подается линейно изменяющееся напряжение от 1".-. до нуля с блока 6.В момент времени, когда Ю становится равным наибольшему из 11,. на выходе 1-го компаратора появляется напряжение логической 1, которое поступает на 1-й адресный вход аналогового коммутатора, первый вход элемента И , и на 1-й вход блока 11. Напряжение, пропорциональное т., с выхода блока 3; поступает на информационный 1-й вход коммутатора 2 и коммутируется им на информационные входы ключей 13 - 13 и4 - 14. На управляющий вход ключа 13, поступает сигнал с единичного выхода триггера 9 а на управляющий вход ключа 14; - сигнал с нулевого выхода.Если напряжение в сумматоре 15 меньше порогового, то сигнал с 1-го выхода коммутатора 12 через ключ 13; поступает на гй суммирующий вход сумматора 15. Напряжение с сумматора 15 поступает на первый вход элемента 16. В случае, если оно меньше порогового, на вторых входах элементов И 10 - 10 напряжение отсутствует, поэтому, хотя на первый вход элемента 10, подается напряжение логической 1 с 1-го выхода блока 11, напряжение на выходе элементов 10 - 10 соответствует логическому 0, следовательно, триггеры 9 - 9 остаются в исходном состоянии, и с их нулевых выходов напряжение логического О подается на управляющие входы ключей 14 - 14 и запрещает прохождение сигналов с выходов аналогового коммутатора 12 на вычитающие входы сумматора, а с единичных выходов напряжение логической 1 подается на вторые уп равляющие входы ключей 13 - 13 и разрешает прохождение сигналов с выходов аналогового коммутатора 12 на суммирующие входы сумматора 15 и на вторые входы элементов И в 7. На выходе элемента И 7, появляется напряжение логической 1, которое засвечивает 1-й светодиод блока 8.Аналогично устройство работает по-му и другим параметрам до тех пор, пока напряжение в сумматоре 15, пропорциональноет, не превышает пороговое напряжение, пропорциональное Тк на втором входе элемента 16. В этом случае с выхода элемента 16 поступает напряжение на вторые входы элементов И 1 О - 10. В соответствии с алгоритмом работы блока 11 на в-м его выходе появляется напряжение, которое поступает на вход триггера 9, и изменяет его состояние на противоположное. С нулевого выхода триггера 9 сигнал логической 1 поступает на управляющий вход ключей 14 и разрешает прохождение сигнала с выхода коммутатора 12 через ключ 14., на гп-й1168903 3вычитающий вход сумматора 15. Выполняется операция Я 1,; - Гх,. Таким образом, напряжение на выходе сумматора 15становится меньшим порогового. Одновременно с операцией вычитания с единичного выхода триггера 9 сигнал логическогоО поступает на второй вход элемента И 7 в,запрещая тем самым засветку т-го светодиода. Этот сигнал запрещает прохождение информации через ключ 13 на суммирующий вход сумматора 15.Устройство продолжает работать аналогичным образом, отыскивая параметр, длякоторого ЛТко.)т, соблюдая при этом при 15оритет Ф - )Работа устройства прекращается, когда1,3 глин 6=0.Блок 1 управления с помощью источника 25, наборов переключателей 221 - 222 Ои 241 ви двух групп 2 ви 231 вделителей позволяет устанавливать необходимые значения входного напряжения в блоках 2 и 3, а также с помощью регулятора 26 - порог срабатывания элемента 16, пропорциональный Тк,25Блок1 исключения избыточности предназначен для предотвращения ложногоотображения т-го параметра для случая,когда Е Сх;(Т, а Е к;)Тк. В этом слуК30чае на устройстве отображения должно отобразиться (в - 1) параметров, а гп-й пара 4быть запрещен к отобраметр долженжени ю.При поступлении с выхода 1-го компаратора 5 напряжения, соответствующего логической 1 на выходе 1-го элемента 17 дифференцирования, появляется импульс, который поступает на 1-й вход элемента ИЛИ 20, с выхода которого импульс поступает на вторые входы триггеров 19 - 19 и обнуляет их. Импульс с выхода 1-го элемента 17 дифференцирования поступает на вход 1-го элемента 18 задержки, с выхода 1-го элемента 18 задержки - на первый вход триггера 19;, который меняет свое состояние на противоположное. Таким образом, на выходе блока 11 исключения избыточности присутствует потенциал логической 1, соответствующий последнему срабатывающему компаратору 5,Технические преимущества изобретения заключаются в повышении точности определения допустимого объема контроля при ограничениях различного уровня за счет возможности дополнительного контроля в остаточном интервале.Положительный эффект от использования предлагаемого устройства состоит в повышении достоверности результатов контроля, так как при одних и тех же ограничениях проверяется больший объем технической системы. Следовательно, уменьшается вероятность нахождения технической системы в состоянии скрытого отказа после проведения контроля, что в свою очередь повышает ее коэффициент технического использования..г Фиг Сост Техр Тира авитель С. Демиденко ед И. Верес Коррж 863 Под тве нного комитета ССС ретений и открытий 35, Раушская наб., д. г. Ужгород, ул. Проек 4/5ая 113035, лиал П Редактор С. СаенкоЗаказ 4611/40ВНИ ПИ Государсделам изоб Москва, Ж - П Патентъ,ектор Л. ВескиисноеР

СмотретьЗаявка

3692956, 24.01.1984

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

БОРОДЕНКО ЕВГЕНИЙ ИВАНОВИЧ, ДУДАРЕВ ВАЛЕРИЙ АЛЕКСЕЕВИЧ, НАЗАРЕНКО ВЛАДИМИР ЕВГЕНЬЕВИЧ, ВИШНЕВСКИЙ ОЛЕГ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/277, G06F 17/00, G07C 11/00

Метки: контролируемых, объема, параметров

Опубликовано: 23.07.1985

Код ссылки

<a href="https://patents.su/4-1168903-ustrojjstvo-dlya-opredeleniya-obema-kontroliruemykh-parametrov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для определения объема контролируемых параметров</a>

Предыдущий патент: Устройство для измерения динамических характеристик

Следующий патент: Устройство для определения выборки контролируемых параметров

Случайный патент: Изобретения