Устройство для функционально-параметрического контроля электронных блоков

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

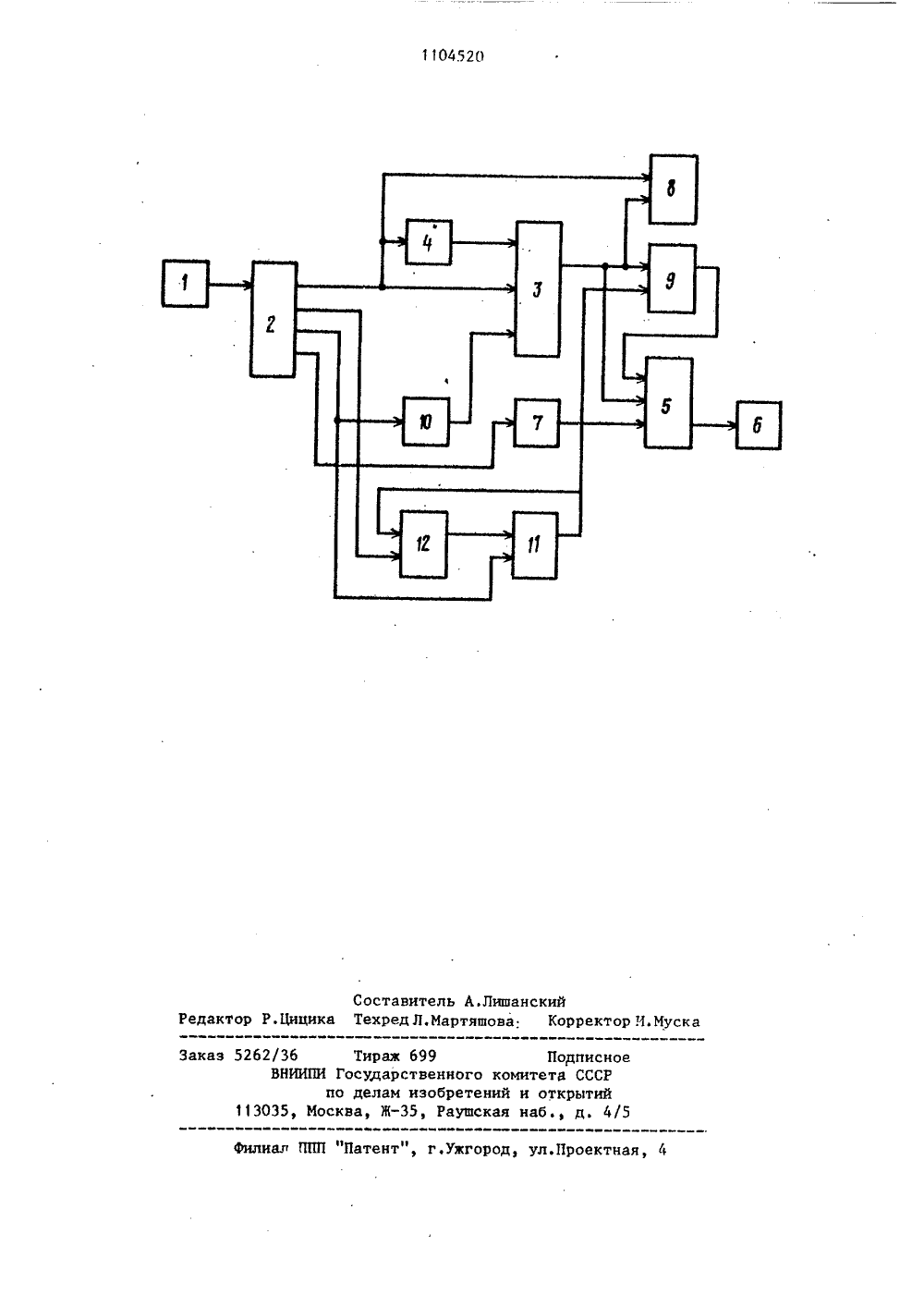

(56), 1. Авторское свидетельство ССУ 643877, кл. С 06 Г 11/08.2, Маловик К,Н., Суханов В.С .Автоматический контроль транзисторных стабилизаторов напряжения.Сборник. "Миниатюризация вторичныхисточников электропитания электронной аппаратуры". Материалы семинарМ МДНТП, 1973, с. 39-42.3. Авторское свидетельство СССРВ 830391, кл, С 06 Г 11/26(прототип). ие Всесоюзногго института е"(54) (57) УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНО-ПАРАМЕТРИЧЕСКОГО КОНТРОЛЯ ЭЛЕКТРОННЬИ БЛОКОВ, содержащее последовательно соединенные тактовый генерато и первый счетчик, подключенный первы ми выходами к входам контактного бло ка и входу дешифратора, соединенного ГОСУДАРСТВЕННЫЙ КОМПО ДЕЛАМ ИЗОБРЕТЕНИЙОПИСАНИЕН АВТОРСКОМУ,.ЯО 1045 выходом с входом контактного блока,связанного выходом с первым информационным входом мультиплексора, соединенного выходом с входом сигнатурноганализатора, а адресным выходом - свыходом второго счетчика, подключенного входом к выходу старшего разряда первого счетчика, о т л и ч а ю -щ е е с я тем, что, с целью расширния области применения устройства,в него введены блок нагрузок, блоккомпараторов, триггер, элемент И иформирователь тестов, подключенныйвыходами к входу контактного блока,входами - к третьему выходу первогосчетчика, соединенного вторым выходомс первым входом элемента И, подключенного вторым входом к прямому выходу триггера и стробирующему входублока компараторов, а выходом - кБ-входу триггера, связанного К-входом с третьим выходом первого, счетчика, адресный вход блока нагрузоксоединен с входом дешифратора, а информационный вход - с выходом конр тактного блока и информационнымвходом блока компараторов, соединенВного выходом с вторым информационнымвходом мультиплексора.Изобретение относится к автоматике и вычислительной технике и можетбыть использовано для функциональнопараметрического контроля смонтированных гибридных электронных блоков,содержащих логические элементы и стабилизаторы напряжения, а также длявходного контроля логических блокови стабилизаторов напряжения. в томчисле интегральных микросхем, у потребителя,Известно устройство для контролялогических блоков, содержащее блокуправления, генератор псевдослучайных кодов, блок свертки и накапливающий сумматор 1 3,Известно устройство для контроляФстабилизаторов напряжения, содержащее блок выдачи команд, блок задания уровня выходного напряжения ста- Обилизатора, блок управления узламиустройства, блок контроля токов,блок питания, блок нагрузок, коммутатор, блок допускового контроля,блок индикации и блок печати ( 2 1; 2Недостатком устройства являетсяневозможность контроля гибридныхэлектронных блоков, содержащих, кроме стабилизаторов напряжения, и логические элементы. ЗОНаиболее близким к изобретению является устройство для функциональ- но"параметрического контроля логических элементов, содержащее последовательно соединенные тактовый генератор и первый счетчик, первые выходы которого через коммутатор - преобра-, зователь и через последовательно соединенные,дешифратор и коммутатор- преобразователь подключены к входам контактного блока, выходы контактно" го блока через коммутатор-преобразователь соединены с одними входами мультиплексора, адресные входы ко торого через коммутатор-преобразова 45 тель подключены к выходам второго счетчика счетный вход которого через коммутатор-преобразователь соединен со старшим разрядом первого счетчика, выход мультиплексора подключен к информационному входу сигнатурного анализатора 13 . Недостатком известного устройства является невозможность контроля гиб-ридных электронных блоков, содержащих, кроме логических элементов, и стабилизаторы напряжения. Целью изобретения является расширение области применения устройства, т.е. наделение его функциями контроля гибридных электронных блоков, содержащих .как логические элементы, таки стабилизаторы напряжения (в том числе имеющие логику управления, например, входы электронного включения- отключения).Указанная цель достигается тем, что в устройство, содержащее последовательно соединенные тактовыйгенератор и первый счетчик, подключенный первыми выходами к входам контактного блока и входу дешифратора, соединенного выходом с входом контактного блока, связанного выходом с первым информационным входом мультиплексора, соединенного выходом с входом сигнатурного анализатора, а адресным входом - с выходом второго счетчика, подключенного входом к выходу старшего разряда первого счетчика, введены блок нагрузок, блок компараторов, триггер, элемент И и формирователь тестов, подключенный выходами к входу контактного блока, входами - к третьему выходу первогосчетчика, соединенного вторым выходом с первым входом элемента И, подключенного вторым входом к прямому выходу триггера и стробирующему входу блока компараторов, а выходом - к Я-входу триггера, связанного К-входом с третьим выходом первого счетчика, адресный вход блока нагрузок соединен с входом дешифратора, а информационный вход - с выходом контактного блока и информационным.входом блока компараторов, соединенноговыходом с вторым информационным входом мультиплексора. На чертеже приведена структурная схема устройства.Устройство содержит тактовый генератор 1, которьй формирует тактовые сигналы рабочей частоты; первый счетчик 2, предназначенный для обеспечения перебора входных тактовых последовательностей; контактный блок 3, в к;.торый вставляется контролируемый электронный блок дешифратор 4, необходимый для формирования тестовых сигналов для несовместимых входов контролируемого электронного блока (несовместимыми называются входы, одновременная ,подача управляющих сигналов на кото3 1104 рые приводит к неопределенному со.= тоянию на выходе блока); мультиплексор 5, выбирающий в каждый отрезок времени один из входных сигналов (в качестве мультиплексора в устройстве используется микросхема К 155 КП 7); сигнатурный анализатор 6, являющийся регистратором последовательностей выходных сигналов контролируемого электронного блока; второй счетчик 7, 1 О осуществляющий перебор адресных входов мультиплексора 5; блок 8 нагрузок, задающий токи нагрузки на выхо" дах контролируемого электронного бло" ка, величины которых определяются значениями на адресных входах блока; блок 9 компараторов, фиксирующих выход за пределы допусков выходных напряжений контролируемого электронного блока, каждый компаратор блока содер- о жит микросхему К 55 С 4 А 1, представляющую собой сдвоенный компараторнапряжения, на один вход каждого иэ которых падает соответствующее пороговое напряжение, другие входы обоих компараторов соединены между собой и на них поступает выходное напряжение .контролируемого электронного блока;формирователь 10 тестов, обеспечивающий тестовые напряжения стандартной или специальной формы на входах контролируемого электронного блока, величины которых определяются значениями входных сигналов; триггер 11, запрещающий прохождение сигнала через блок 9 компараторов,35 начиная с момента изменения входного сигнала формирователя 10 тестов; элемент И 12, устанавливающий триггер 11 в исходное состояние по фронту сиг." 40 нала на втором выходе первого счетчика 2, при этом длительность запрещающего сигнала на прямом выходе триггера 11 не менее длительности переходного процесса выходных напряжений формирователя 10 тестов.Устройство работает следукнцим образом.При проверке конкретного электронного блока его подключают к устройству с помощью контактного бло 50 ка 3, После этого включается такто" 520 4вый генератор 1, запускаются первыйсчетчик 2, дешифратор 4 и второйсчетчик 7. Фсрмирователь 10 тестови блок 8 нагрузок под управлениемпервого счетчика 2 обеспечивают формирование всех необходимых значений входных тестовых напряжений и выходных токов соответственно стабилизаторов напряжения контролируемого электронного блока. Благодаря этому осуществляется полный перебор всех необходимых стимулирующих воздействий для контролируемого гибридного электронного блока (как для входящих в него логических элементов, так и стабилизаторов напряжения). Выходные последовательности с выходов контро- лируемого электронного блока непосредственно или через блок 9 Компараторов последовательно подаются через мультиплексор 5 на вход сигнатурного анализатора 6, формирующего сигнатуру электронного блока. Полученная сигнатура сравнивается с эталонной. При совпадении сигнатур контролируемый электронный блок исправен. Предлагаемое устройство позволяет осуществлять функционально-параметрический контроль гибридных электронных блоков, содержащих логические элементы и стабилизаторы напряжения (в том числе имеющие логику управления, например входы электронного включения-отключения). При этом уменьшается количество требуемых устройств и операции контроля, что обеспечивает экономию материальных затрат на обеспечение производственного контроля Производимых электронньЫ блоков и входного контроля комплектующих, сокращение требуемых производственных площадей, уменьшение обслуживающего персонала, Кроме того, повышается производительность контроля за счет уменьшения числа установок контролируемого гибридного электронного блока на устройство контроля (для электронных блоков с малым числом входов и выходов время установки элемента значительно больше времениконтроля).1104520 Тирвк 699 Поцписное суцарственного комитета СССР делам изобретений и открытий а, %-35, Раушская наб., д. 4/5 аз 5262/36ВНИИПИ п 13035, Мос

СмотретьЗаявка

3516279, 02.12.1982

ИСТРИНСКОЕ ОТДЕЛЕНИЕ ВСЕСОЮЗНОГО НАУЧНО-ИССЛЕДОВАТЕЛЬСКОГО ИНСТИТУТА ЭЛЕКТРОМЕХАНИКИ

САРЫЧЕВ КОНСТАНТИН ФЕДОРОВИЧ, БУЛЫЧЕВА ОЛЬГА ВЛАДИМИРОВНА, БЛИНОВ АЛЕКСАНДР МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 11/08

Метки: блоков, функционально-параметрического, электронных

Опубликовано: 23.07.1984

Код ссылки

<a href="https://patents.su/4-1104520-ustrojjstvo-dlya-funkcionalno-parametricheskogo-kontrolya-ehlektronnykh-blokov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для функционально-параметрического контроля электронных блоков</a>

Предыдущий патент: Многоканальное устройство для автоматического контроля микропроцессоров

Следующий патент: Устройство для отладки программ

Случайный патент: Теплоприемник к радиационным пирометрам и радиометрам