Устройство для логарифмирования двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

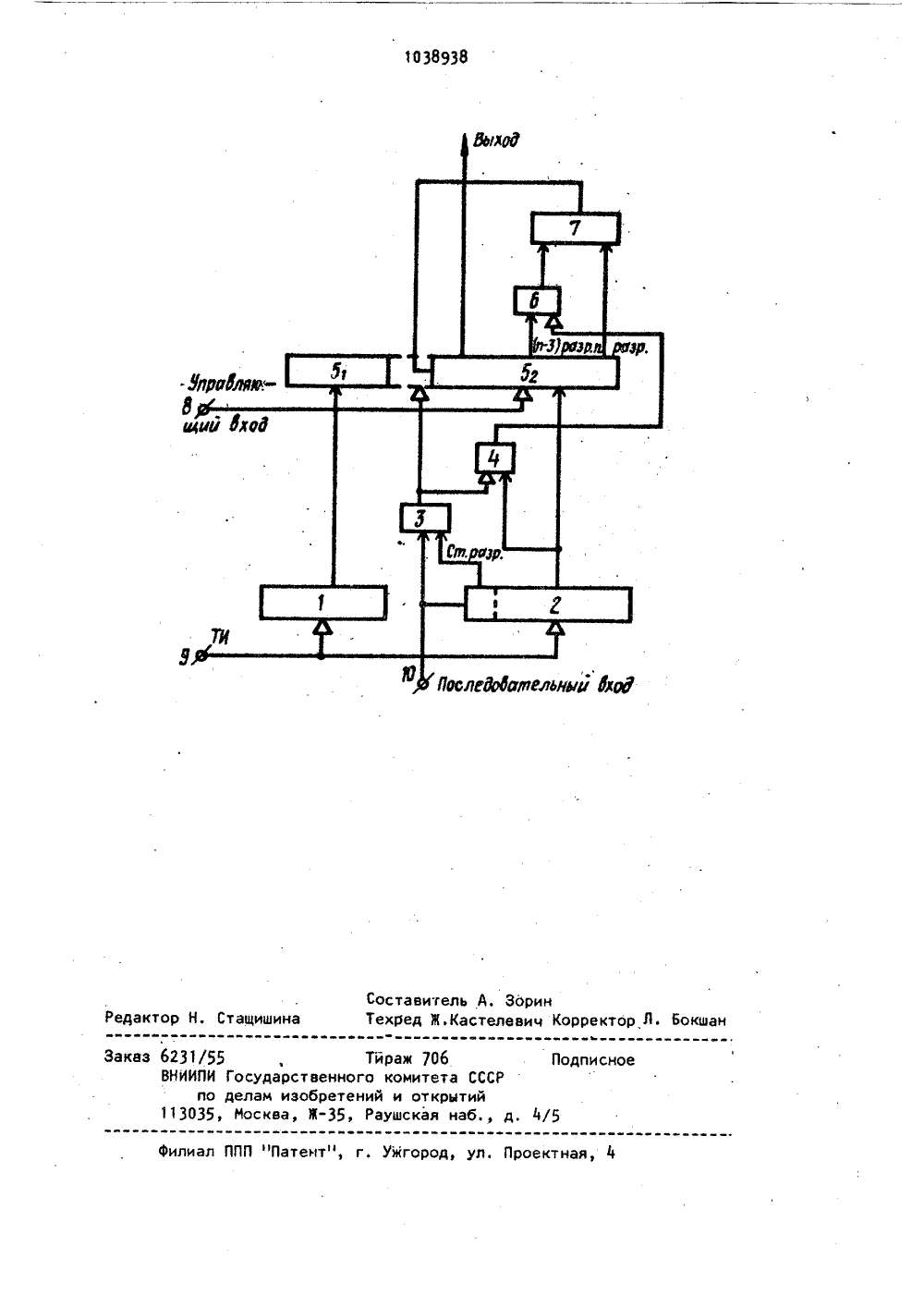

,выОСУДАРСТНЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ АВТОРСКОМУ СВИДЕТЕЛЬСТВ(72) Е, Д. Горячева и И. ш. Розенблат (71) Львовский ордена Ленина политехнический институт им. Ленинского комсомола(56) 1, Волгин А. Н; и др. Логарифмический преобразователь двоичных чисел.-. "Приборы и техника эксперимента", 1978, й б, с. 48.2. Авторское свидетельство СССР й 926655, кл. С Об Г 7/556 (прототип) (54)(57) устРойстВО для логАРифииРО- ВАНИЯ ДВОИЧНЫХ ЧИСЕЛ, содержащее счет чик порядка, сдвиговый регистр,сумматор по модулю два, регистр старших разрядов числа и регистр младших разрядов чи.сла, причем вход аргумента устройства соединен с информационным входом сдвигового регистра, тактовый вход которого соединен с входом тактовых импульсов записи устройства и входом счетчика порядка, выход которого соединен с информационным входом регистра старших разрядов числа, управляющий, вход которого соединен с выходом сумматора по модулю два и управляоцим входом регистра младших разрядов числа, выход первого раэряЯО.1038938 А да сдвигового регистра соединен спервым входам сумматора по модулюдва, второй вход которого соединенс информационным входом устройст"ва, о т л и ч а ю щ е е с я тем,что, с целью уменьшения аппаратурных затрат, оно содержит триггер,коммутатор.и одноразрядный сумматор, выход которого соединен с последовательным входом регистра младших разрядов числа, параллельныйвход которого соединен, с выходомс второго по п-й разрядов сдвигового регистра, где и - разрядностьаргумента, тактовый вход регист"ра младших разрядов числа соединенс входом тактовых импульсов коррек" Еции устройства, выход сумматора помодулю два соединен с первым входомтриггера, второй вход и выход которого соединены соответственно с выходом второго разряда сдвиговогорегистра и управляющим входом коммутатора, первый и второй информационные входы которого. соединены соответственно с прямым щ инверсным вы- Мходами (и)-го разряда регистра 00младших разрядов числа, выход и-го (;фразряда которого соединен с первым фф.входом одноразрядного сумматора, Явторой аход которого соединен сходом коммутатора.10389Изобретение относится к вычисли,тельной технике, в частности к специ"ализированным вычислительным устройствам, и может быть использовано дляопределения, например.,спектральныххарактеристик в логарифмическом масштабе в спектроанализаторах.Известен логарифмический преобразователь двоичных чисел, содержащийдешифратор, схему разрешения, одно пос-тоянное запоминающее устройство,представляющее собой таблицу логарифмов щ-разрядных двоичных чисел, другоепостоянное запоминающее устройствои- итаблицу логарифмов чисел 2 , М-разрядный комбинированный сумматор 1.Однако зто устройство:характеризуется сложностью схемы, наличиемдорогостоящих узлов таких, как ПЗУ ирезисторная матрица. 20Наиболее близким к предлагаемомупо технической сущности является устройство для логарифмирования чисел,содержащее регистр числа, сдвиговыйрегистр, счетчик порядка, сумматор 25по модулю два, блок, памяти таблицылогарифмов.Двоичное число в последовательном коде поступает младшими разрядами вперед в сдвиговый регистр. Счетчик порядка считает количество сдвигов. Сумматором по модулю два анализируются два соседних разряда двоичного числа, при каждом несовпадении их содержймого на выходе сумматора появляется сигнал, разрешающий занесение в регистр числа содержимого счетчика порядка и выходногосигнала блока памяти таблицы логарифжов, который определяется содержимым 40регистра сдвига 2 ,38 2Указанная цель достигается тем, что устройство для логарифмирования двоичных чисел, содержащее счетчик порядка, сдвиговый регистр, сумматор по модулю два, регистр старших азрядов числа, регистр младших разрядов числа, причем вход аргумента устройства соединен с информационным входом сдвигового регистра, тактовый вход которого соединен с входом тактовых импульсов записи устройства и входом счетчика порядка, выход которого соединен с информационным входом регистра старших разрядов числа, управляющий вход которого соединен с выходом сумматора по модулю два и.управляющим входом регистра младших разрядов числа, выход первого разряда сдвигового регистра соединен с первым входом сумматора по модулюдва, второй вход которого соединен с информационным входом устройства, содержит триггер, коммутатор и одноразрядный сумматор, выход которого соединен с последовательным входом регистра младших разрядов числа,параллельный вход которого соединен с выходом с второго по и-й разрядов сдвигового регистра, где и - разрядность аргумента, тактовый вход регистра младших разрядов числа соединен с входом тактовых импульсов коррекции устройства, выход сумматорапо модулю два соединен с первым входом триггера, второй вход и выход которого соединены соответственно с выходом второго разряда сдвигового регистра и управляющим входом коммутатора, первый и второй информационные входы которого соединены соотвественно с прямым и инверсным выхоНа чертеже показана функциональная схема устройства.Устройство содержит счетчик 1 порядка, сдвиговый регистр 2,сумматор 3 по модлую два, триггер 4,регистр 5 числа, содержащий регистр5 старших и регистр 5младшихразрядов числа, коммутатор 6,одноразрядный сумматор 7, входы 8-10. Недостатком известного устройства является наличие блока памяти таблицы логарифмов, представляющего собой, например ПЗУ, Причем емкость 45 и разрядность ПЗУ зависит от разрядности логарифмируемых двоичных чисел и от необходимой точности логарифмирования.Так как нет серийно выпускаемых полупроводниковых интегральных микросхем таких специальных функций как 1 од а, необходимо реализовать эту функцию на интегральных макросхемах типа ПЗУ или программируемых постоян ных запоминающих устройствах (ППЗУ ).Цель изобретения - уменьшение ап. паратурных затрат. дами (и)-го разряда младших разрядов числа, выход и-го разряда которого соединен с первым входом одноразрядного сумматора, второй вход которого соединен с выходом коммутатора.3 Работа устройства основана на соотношении:1038938значащего разряд числа. Процесс ввода числа окончен. Теперь происходит/ 21 где Р - порядок числа;х - двоичный код нормализованного числа а без старшей значащей единицы.0Устройство работает следующим образом,Двоичное число в последовательном коде поступает младшими разрядами вперед в сдвиговый регистр 2.Насчетный вход счетчика 1 порядка иуправляющий вход сдвигового регист- .ра 2 поступают тактовые импульсы повходу 9. Счетчик 1 считает количество сдвигов, Сумматором 3 по модулю 20два анализируются два соседних разряда двоичного числа, при каждомнесовпадении их содержимого происходит занесение в старшие 5 ч и младшие 52 разряды регистра числа и втриггер 1 соответственно содержимогосчетчика 1 порядка, содержимого регистра 2, не включая старший разряд,и следуюЩего за старшим разряда регистра 2.После последнего занесения в 30старших разрядах. регистра 5 числасодержится порядок двоичного числа (характеристика логарифма) , а вмладших - двоичный код числа послестаршего значащего разряда, в триг-.гере 1 - следующий после старшего коррекция двоичного кода, содержащегося в и- младших разрядах регистра 52 числа, т.е. Определение мантиссы логарифма. В зависимости от содержимого триггера 4 (нуль или единица) на выход коммутатора б пропускается сдвинутый на три разряда в сторону младших прямой или обратный двоичный код и-. младших разрядов регистра 5 2,числа соответственно.На одноразрядном сумматоре 7 этот код суммируется поразрядно, начиная с младших разрядов, с прямым несДвинутым двоичным кодом, С выхода сумматора 7 сумма задвигается по последовательному информационному входу на место регистра 52 младших разрядов числа, Сдвигом этих разрядов во время коррекции мантиссы логарифма управляет вход 8,ФПосле и сдвигов в регистрах 5 и52 находится значение характеристикии мантиссы числа.Предлагаемое устройство значитель"но проще по сравнению с прототипом.Логарифмирование ведется в реальноммасштабе времени по мере поступлениядвоичных чисел .из арифметическогоустройства.Вместо дорогостоящих специально.программируемых ПЗУ используетсяодин коммутатор, триггер и однораз"рядный сумматор.1638938 Составитель А, Зори ащишина Техред Ж. КастелевичеТйраж 706осударственного комитета СССРелам изобретений и открытийМосква, -35, Раушская наб д. Подписное лиал ППП "Патент", г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

3418452, 08.04.1982

ЛЬВОВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. ЛЕНИНСКОГО КОМСОМОЛА

ГОРЯЧЕВА ЕЛЕНА ДМИТРИЕВНА, РОЗЕНБЛАТ МИША ШЛЕМОВИЧ

МПК / Метки

МПК: G06F 7/556

Метки: двоичных, логарифмирования, чисел

Опубликовано: 30.08.1983

Код ссылки

<a href="https://patents.su/4-1038938-ustrojjstvo-dlya-logarifmirovaniya-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для логарифмирования двоичных чисел</a>

Предыдущий патент: Устройство для умножения

Следующий патент: Логарифмический преобразователь

Случайный патент: Устройство для сепарации кусковых материалов