Устройство для деления п-разрядных двоично-десятичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

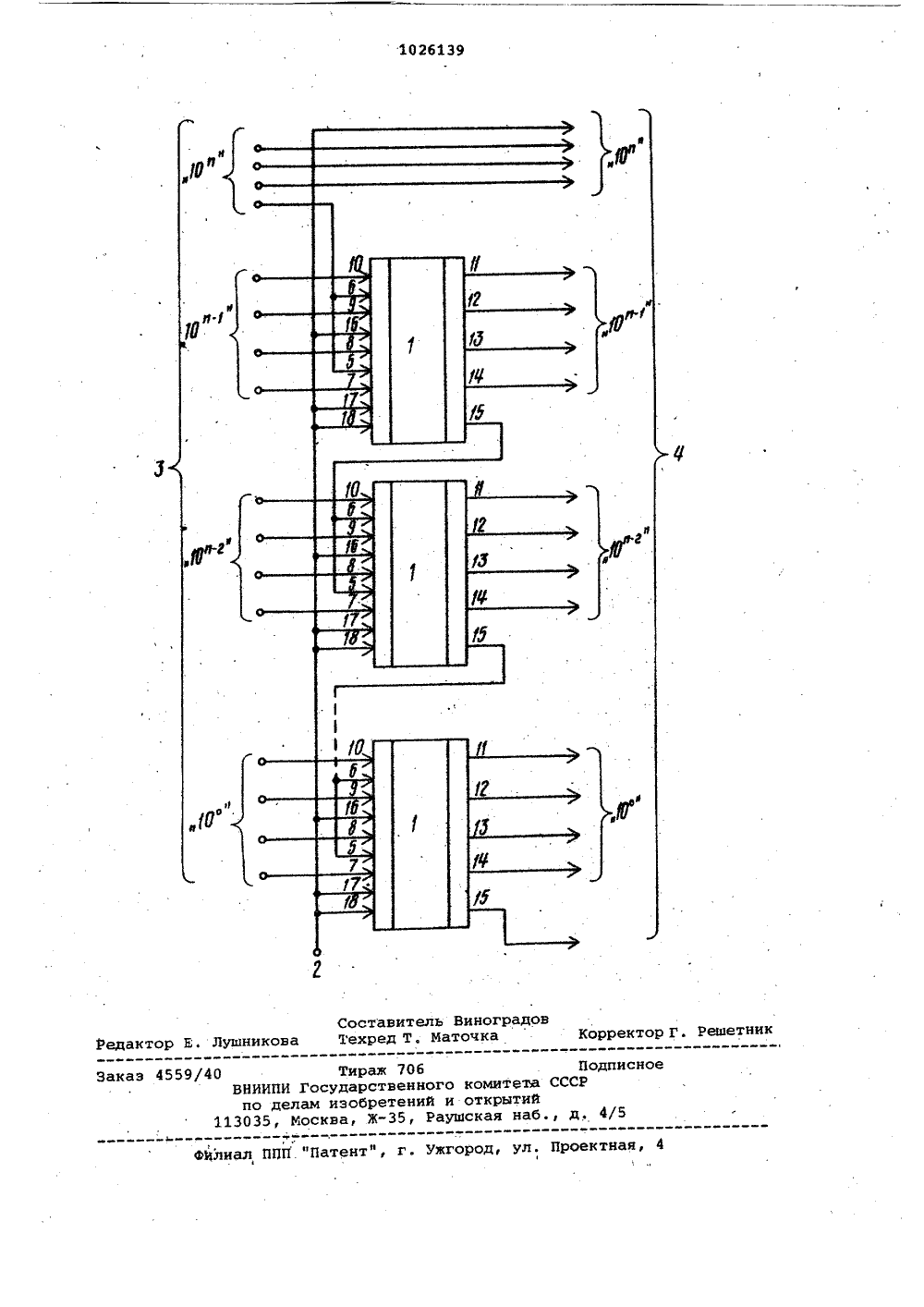

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК у 5 ц С 06 Р 7/5 РЕТЕНИ гЧ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛМЫ ИЭОБРЕТЕНИЙ И ОТКРЫТИИОПИСАНИЕ ИзК АВТОРСНОМУ СВИМПОЪС Г 21)3411694/18-24(54)(57) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯК-РАЗРЯДНЫХ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ,содержащее вычислительный блок, о т"л и ч а ю щ е е с я тем, что,с целью упрощения устройства и повышения быстродействия при делении надва, оно содержит дополнительно(и) вычислительных блоков (и -число десятичных разрядов), каждый извычислительных блоков, представляетсобой комбинационный сумматор, причем каждый сумматор имеет четыре дноичных разряда, первые входы разрядов, 8 ОА сумматоров соединены с входными шинами соответствующих десятичных разря дов деленого устройствй, вторые входы первых и третьих разрядов комбинационных сумматоров соединены с шиной сигналалогического нуля устройства, вторые входы вторых-н четвертых разрядов комбинационных сумматоров соединены с выходами первых разрядов суммы предыдущих комбинационных сумматоров соответственно, вторые входы второго и четвертого разрядов (и-го комбинационного сумматора соединены с первой входной шиной и-го десятичного разряда делимо-. го устройства, входные шины с второй по четвертую и-го десятичного раз ряда делимого.устройства и шина логического нуля устройства соединены с выхойиыми шинами и-го десятичного разряда частного, выходные шинн каж- С дого разряда частного с первого по (п)"й устройства соединены с вы- р ходами разрядов суммы с второго по четвертый и выходом переноса соответствующего комбинационного сумматора.рые входы второго и четвертого разря.- дов ( и) -го комбинационного сумматоров соединен с первой входной шиной и-го десятичного разряда делимого устройства, входные шины с второй по четвертую и-го десятичного разряда делимого устройства и шина логического нуля устройства соединены с выходными шинами и-го десятичного разряда частного, выходные шины каждого разряда частного с первого по (и)-й устройства соединены с выходами разрядов суммы с второго по четвертый и выходом переноса соответствующего комбинационного сумматора.На чертеже изображена схема устройства для деления и-разрядных дво.ично-десятичных чисел.Устройство содержит (и) четырех. разрядных полных двоичных комбинаци- ,онных сумматоров 1, вычислительных блоков , шину 2 сигнала логического нуля, входные шины 3 делимого, выходные шины 4 частного.устройство работает следующим об-,разом.п-разрядное десятичное число в двоично"десятичном коде поступает на входные шины 3 делимогоТри старших разряда двоичного кода цифры и-го разряда делимого являются тремя младшими разрядами двоичного кода цифры и-го разряда частного, старший разряд кода цифры п-го разряда частного равен нулю, Младший разряд двоичного кода п-го разряда делимого подается на входы 5 и б сумматора 1 (и)-Го разряда. Если младший разряд двоичного кода и-го разряда равен нулю, то двоичный код цифры (и)-го разряда делимого, поступающий на входы 7-10 сумматора 1 (и)-го разряда, передается на выходы этого сумматора без изменения, и с выходов 11-14 снимается двоичный код цифры (п)-го разряда частного, равный половине значения цифры (и) -го разряда делимого. Если младший разряд 15 двоичного кода и-го разряда делимого равен единице, то в сумматоре 1 ( и)-го разряда происходит сложение цифры (и)-го разряда делимого с цифрой десяти (1010), и с выходов 11-14 сумматора 1 (и)-го разряда снимается двоичный код цифры ( и) -го разряда частного, равный половине значения полученной двоичной суммы. Шина 2 подключена к входам 1 бсумматоров 1.Младший разряд суммы с выхода 15 сумматора 1 1 и) -го разряда подается на входы 5 и б сумматора 1 ( и)-го разряда, на входы 7-10 которого подается двоичный код цифры (и-го разряда делимого, На выходах 11-14 сумматора 1 ( и)-го разряда формируИзобретение относится к вычислительной технике и может быть исполь-.зовано, в частности, в системах формирования кодов, а также в специализированных вычислительных устройствах.статической обработки информации,Известны устройства для делениядесятичных чисел, содержащие регистры операндов, сумматоры, логическиеэлементы, в которых очередная цифрачастноГо вычисляется с помощью серии 10вычитаний делителя из положительногоостатка до получения отрицательнойразности или серии сложений делителяс отрицательным остатком до получения положительной или нулевой разности ) 1.Наиболее близким к предлагаемомуявляется устройство для деленияи-разрядных двоично-десятичныхчисел,содержащее регистр делимого, регистр,20делителя, регистр частного, блок Формирования цифр частного, блок управления и вычислитель, два управляющих входа которого подключены к соответствующим выходам блока управле 25ния, третий вход которого через блокФормирования цифр частного подключен к первому входу регистра част- .ного, второй вход которого подключенк четвертому входу блока управления 30и к управляющему входу регистра делимого, первый выход которого подключен к первому входу сумматора, а второй вход последнего - к первому выходу регистра делителя, выход сум матора подключен к входу регистра делимого 2.Недостатком являются избыточность аппаратуры и низкое быстродействие при решении частной задачи де ление и-разрядных двоично-десятичныхчисел на два.Цель изобретения - упрощение устройства и повышение быстродействия при делении на два. 45Поставленная цель достигается тем, что устройство для деления и-разрядных двоично-десятичных чисел, содержащее вычислительный блок, содержит дополнительно) (и) вычислительных блокови-число десятичных разрядов),5 каждый из вычислительных блоков представляет собой комбинационный сумматор, причем .каждый сумматор имеет четыре двоичных разряда, первые входы разрядов сумматоров соединены с 55 входными шинами соответствующих десятичных разрядов делимого устройства, вторые входы первых и третьих разрядов комбинационных сумматоров соединены с шиной сигнала логического нуля 60 устройства, вторые входы вторых и четвертых разрядов комбинационных сумматоров соединены с выходами первых разрядов Суммы предыдущих комбинационных сумматоров соответственно, втоется двоичный код цифры 1( п)-го разряда частного, равный половине значения цифры (и) -го разряда дели- мого, если младший, разряд суммы с выхода разряда 15 сумматора 1 ( п) -го разряда равен нулю, или равный поло вине значения полученной суммы от сложения цифры (и)-го разряда делимого с цифрой десять (1010), если младший разряд суммы с выхода разряда 15 сумматора 1(п)-го разряда равен единице.Младший разряд суммы с выхода раз ряда 15 сумматора 1 (и)-го разряда подается на входы 5 и 6 сумматора и)-го разряда (не показан.Формирование десятичной цифры частного ( и) -го и последующих разрядов аналогично описанному выше Фор. мированию цифры частного (и)-го разряда.Первый разряд 15 выхода суммы сумматора 1 младшего разряда свидетельствует о четности делимого, Если данный разряд равен нулю, то дели" мое - число четное и разделилось надва без остатка, если разряд равен единице, то делимое число нечетноеи к частному добавляется 0,5,Например, когда на входные шины3,подается код трехзначного десятич,ного .числа 728(0111 0010 1000), навыходных шинах 4 получается кодчисла 364(0011 0110 0100 О), а когдана входные шины 3 подается код числа729(0111 0010 1001) на выходных шинах 4 получается код числа 364,5(001110, 0110 0100 1) .Предлагаемое устройство в отличиеот.известных содержит меньшее числоэлементов, так как в нем отсутствуют регистры делимого, делителя и15 частного, блок Формирования цифрчастного и блок управления. Быстродействие устройства опреде-,ляе ся только собственным временемпереключения двоичных полных четырехразрядиых сумматоров и не зависит оталгоритма Формирования цифр частногои времени переключения регистровделимого, делителя, частного, блока 25Формирования цифр частного и блокауправления.102 б 139 тавитель Виноградоред Т, Маточка орректор Г. Решетник Лушнико едакт 59/4 писное Эак илиал ППП "Патентф, г. Ужгород, ул. Проек ИИо35 Тираж 70 б Государственног лам изобретений Москва, Ж, Ра омитета СССР ткрытий кая наб., д,

СмотретьЗаявка

3411694, 24.03.1982

ПРЕДПРИЯТИЕ ПЯ Р-6510

ШИШОВ СЕРГЕЙ ЯКОВЛЕВИЧ, СУЧКОВА АНТОНИНА БОРИСОВНА

МПК / Метки

МПК: G06F 7/52

Метки: двоично-десятичных, деления, п-разрядных, чисел

Опубликовано: 30.06.1983

Код ссылки

<a href="https://patents.su/4-1026139-ustrojjstvo-dlya-deleniya-p-razryadnykh-dvoichno-desyatichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для деления п-разрядных двоично-десятичных чисел</a>

Предыдущий патент: Устройство для сопряжения цифровой вычислительной машины с накопителем на магнитной ленте

Следующий патент: Устройство для вычисления полинома второй степени

Случайный патент: Устройство для дозирования и распределения сыпучего материала