Программируемое логическое устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 982092

Авторы: Голованевская, Левин, Рувинский, Селютин

Текст

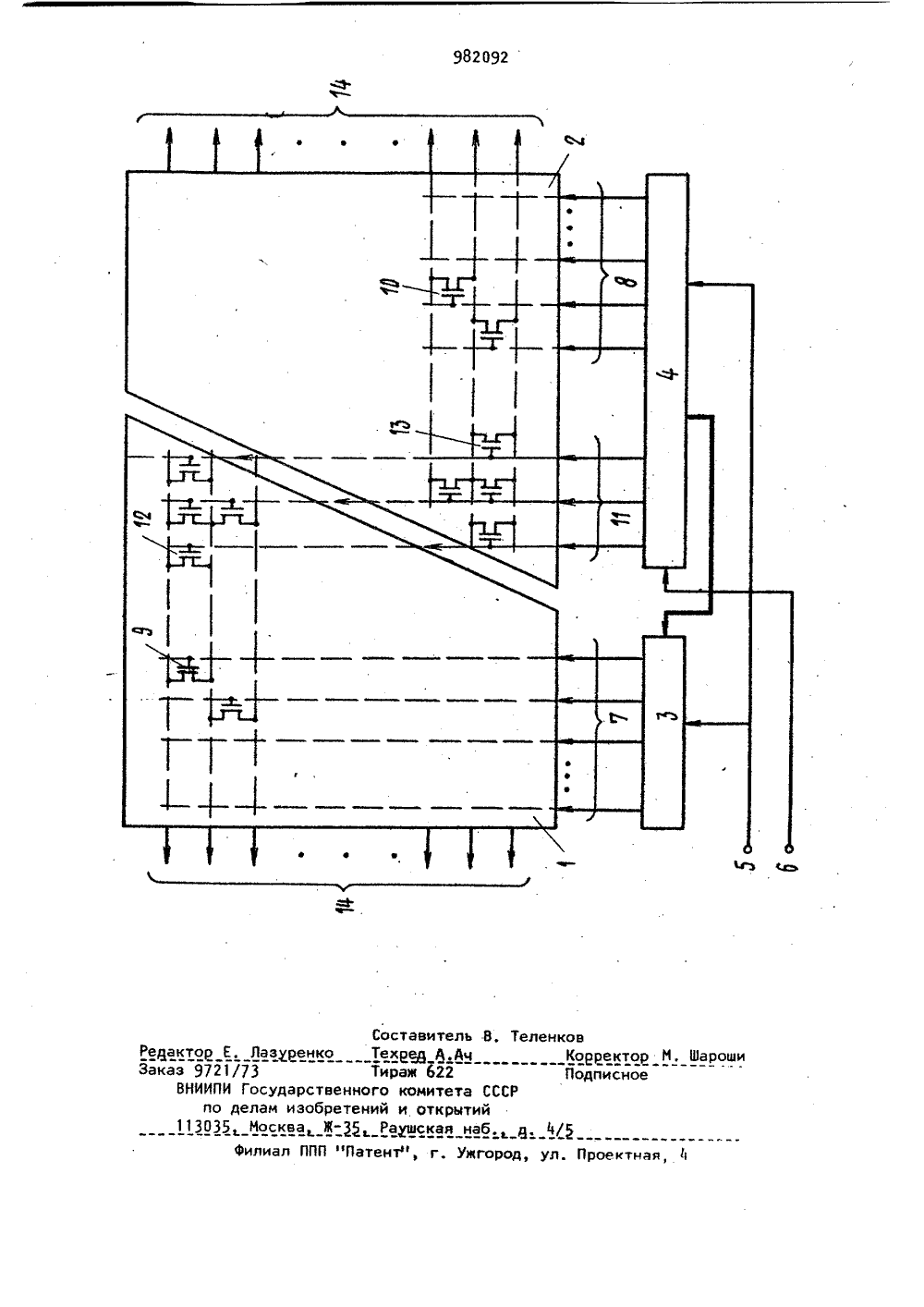

,ОЛ ИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ и 982092. Союз СоветекикСоциалистическихРеспублик(22)Заивлеио 2.12.8 О(21) 322296 У 18-2 Цс присоединением заявки И(5)М. Кл,6 11 С 15/04 3 Ьеударезюай каетет ИСР Ю ЗВММ ЮЕбрвтеннВ в втврвпвй.66088.8) Дата опубликования описания 1812,82- .сЕ.Д. Голованевская, А.В. Левин, Ь.И, Руи. С.А. Селютин(72) Авторы изобретения 4) ПРОГРАИИИРУЕИОЕ ЛОГИЧЕСКОЕ УСТРОЙС 3Изобретение относится к вычисли.тельной технике и может быть исполь зовано при разработке устройств микропрограммного управления,Известно устроиство микропрограм много управления, выполненное на программируемых логических матрицах (ПЛИ) Я.Недостатком этого устройства является малая плотность занесения ин Формации за счет невозможности использования ячеек памяти при опреде ленном кодировании между соседнимивыходными шинами. Это приаодит к ув личениа площади интегральной схемы устройства при заданном объеме исходной ийфрмации.Наиболее близким техническим решением к изобретению является уст" ройство, состоящее из нескольких й и соответствующих им сдвиговых регистров адреса. Управляюцие и адрес ные входы регистров соединень 1 соответственно с шиной синхронизации и.регистров - с входами соответствующих блоков памяти 12,Недостатками данного устройства.являются большая площадь кристаллаи соответственно стоимость интегральной схемы из-за наличия значительного числа неиспользуемых ячеек памяти, поскольку запись информации (впроцессе технологического изготовления) каждого блока памяти выполненанезависимо от остальных блоков.Цель изобретения -, повышение .нае- дежности программируемого логического устройства за счет уменьшенияплощади кристалла и снижения стоимости интегральной схемы устройства.Поставленная цель достигается тем,что в программируемом логическом устЛИ, 2 в ройстве, содержащем первый и второйблоки памяти, входы которых подключены к соответствующим выходам первого и второго сдвиговых регистров,ф 1 управляющие входы которых соединены2092 Формула 3 98с шиной синхронизации, адресный входвторого сдвигового регистра соединенс шиной адреса, адресный выход второго сдвигового регистра подключен кадресному входу первого сдвиговогорегистра, а.выход второго сдвиговогорегистра соединен с соответствующимвходом первого блока памяти,На чертеже схематично изображенопредлагаемое устройство,Устройство содержит программируемые блоки 1 и 2 памяти и сдвиговыерегистры 3 и 4, Управляющие входырегистров 3 и 4 соединены с шиной5 синхронизации. Адресный вход регистра 3 соединен с адресным выходомрегистра 4, адресный вход регистра 4соединен с шиной б адреса, Разрядныевыходы регистра 3 и первые разрядные выходы регистра 4 через входныешины 7 и 8 соединены с затворами первой группы МОП-транзисторов 9 и 10в блоках 1 и 2 памяти соответственно. Вторые разрядные выходы регистра4 с помощью общих входных шин 11соединены с затворами второй группыМОП-транзисторов 12 и 13 в блокахи 2 памяти. Истоки и стоки МОПтранзисторов обеих групп подключенык выходным шинам 14.Устройство работает следующим образом.На адресный вход регистра 4 с шины 6 адреса последовательно поступает слово адреса, состоящее из двухчастей, Одновременно с этим происходит сдвиг регистра .4 и запись внего адреса. В процессе записи адреса в регистр 4 первая часть адресного слова поступает также на адресный вход регистра 3 посредством егосвязи с адресным выходом регистра 4и записывается в регистр 3 аналогичным образом. После записи адресав регистры 3 и 4 на шине 5 появляется сигнал синхронизации, который поступает на управляющие входы регистров 3 и 4 и обеспечивает опрос адреса. При этом первая часть. адресапоступает с разрядных выходов регистра 3 и с первых разрядных выходоврвгистра 4 на входные шины 7 и 8 соответственно и далее на затворы первой группы МОП-транзисторов 9 и .10соответственно. фВторая часть адреса поступаетс вторых разрядных выходов регистра4 на общие входные шины 11, которыеобеспечивают выполнение совместнойпрошивки матриц, и на затворы второйгруппы МОП-транзисторов 12 и 13, Врезультате происходит считываниеинформации из блоков 1 и 2 памятина выходные шины 14,Совместаня запись информации вдва блока 1 и 2 памяти осуществляется таким образом, чтобы увеличениечисла транзисторов в строке в одномблоке памяти соответствовало уменьшению числа транзисторов в другомблоке, Поскольку в блоках памяти,как правило, осуществляется неполнаядешифрация адресного слова, то возможность совместной записи информации с учетом отмеченного требования практически всегда существует.Изобретение позволяет сократитьобщую площадь кристалла в блоках памяти на 1 Опри совместной записи информации и понизить стоимостьинтегральной .схемы устройства. изобретенияПрограммируемое логическое устройство, содержащее первый и второй блоки памяти, входы которых подключены к соответствующим выходампервого и второго сдвиговых регистров, управляющие входы которых соединены с шиной синхронизации, адресный вход второго сдвигового регистра соединен с шиной адреса, о т л ич а ю щ е е.с я тем, что, с цельюповышения надежности программируемого логического устройства, в немадресный выход второго сдвиговогорегистра подключен к адресному входу первого сдвигового регистра, авыход второго сдвигового регистрасоединен с соответствующим входомпервого блока памяти,Источники информации,принятые во внимание при экспертизе1. Реализация микропрограммногоавтомата на БИС. Электронная техника, сер. 3, "Микроэлектроникаф,вып, 5(53), М., 1974, с. 21-26,2, Микросхема Р, Схема принципиальная электрическая ИУ 3.487,982092 Корректор М,Подписное илиал ППП "Патент", г. Ужгород Проектная,У Составитель 3, Теленецактор Е, Лазаренко Техцщ ,Дчаказ 9721/73 Тираж 522ВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035 Москва Ж-Я Раушскан наб. д, 4

СмотретьЗаявка

3222963, 25.12.1980

ПРЕДПРИЯТИЕ ПЯ Х-5263

ГОЛОВАНЕВСКАЯ ЕЛЕНА ДМИТРИЕВНА, ЛЕВИН АЛЕКСАНДР ВАСИЛЬЕВИЧ, РУВИНСКИЙ БОРИС ИОСИФОВИЧ, СЕЛЮТИН СЕРГЕЙ АБРАМОВИЧ

МПК / Метки

МПК: G11C 15/04

Метки: логическое, программируемое

Опубликовано: 15.12.1982

Код ссылки

<a href="https://patents.su/3-982092-programmiruemoe-logicheskoe-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Программируемое логическое устройство</a>

Предыдущий патент: Накопитель для ассоциативного запоминающего устройства

Следующий патент: Запоминающее устройство

Случайный патент: Устройство для продувки труб