Устройство формирования сигнала отсчета для дифференциального кодера изображений

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 906033

Автор: Сергеев

Текст

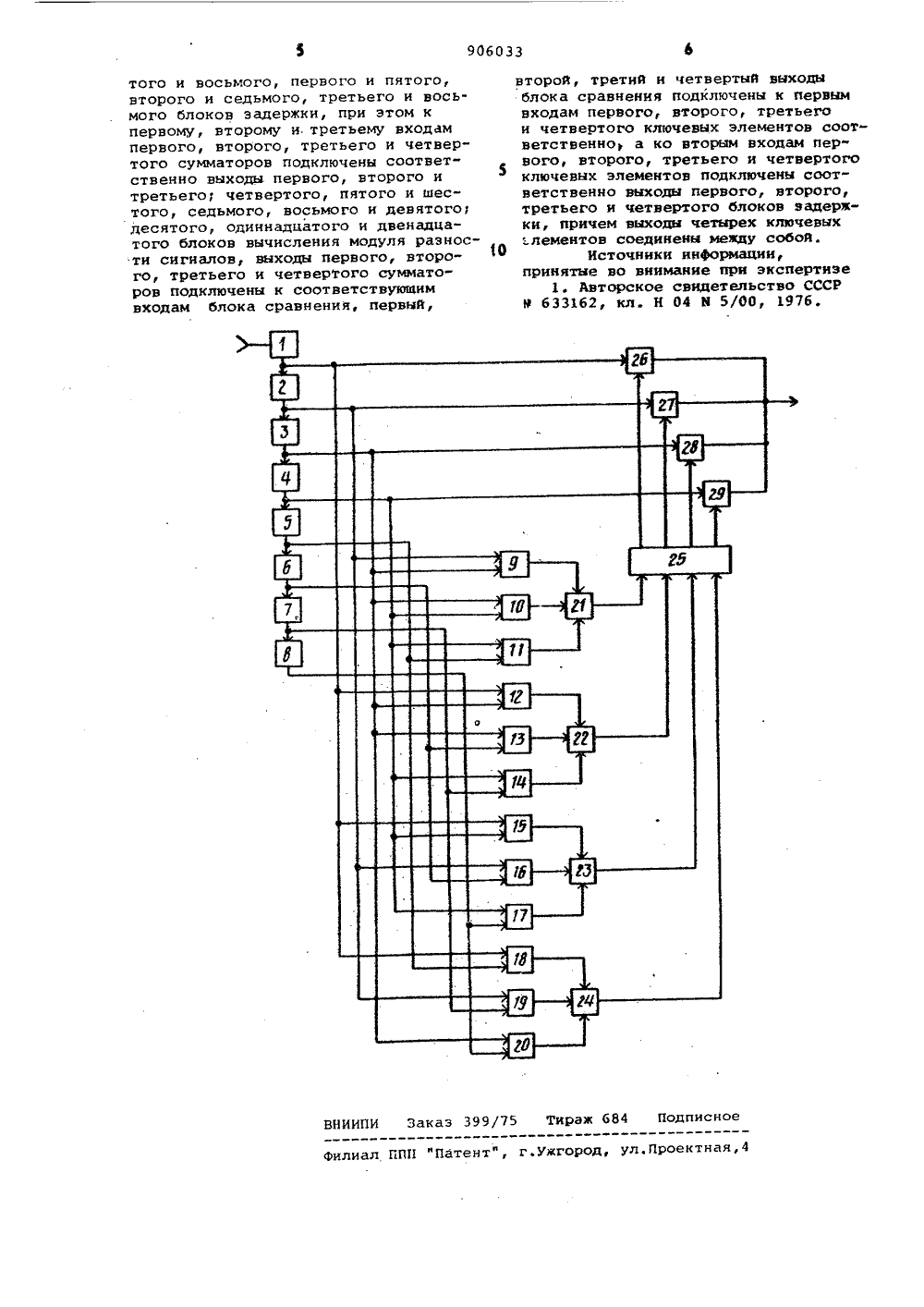

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоцналнстическихРеспублнк р 1906033(22) Заявлено 02 Л 079 (21) 2824926/18-09с присоединением заявки Мо(23) ПриоритетОпубликовано 150232, Бюллетень М 6Дата опубликования описания 15,02,82 111 М. Кп.з Н 04 Н 7/13 Государственный комитет СССР по делам изобретений н открытий(72) Авторизобретения В.В. Сергеев Куйбвввевскнй ордена ррудового Красного янадннн авиационный институт им, акад. С.П.Королева(54) УСТРОЙСТВО ФОРИНСОВАНИЯ СИГНАЛА ОТСЧЕТА ДЛЯ ДИФФЕРЕНЦИАЛЬНОГО КОДЕРА ИЗОБРАЖЕНИЙ Изобретение относится к радиотехнике и может использоваться припостроении кодирующих устройств, прЪменяющих дифференциальное кодирование построчно развертываемых иэображений для их передачи по цифровомуканалу.Известно устройство формированиясигнала отсчета для дифференциального кодера изображений, содержащеепоследовательно соединенные семьблоков задержки, первый и второйсумматоры 1).Однако известное устройство имеетнизкую точность Формирования сигнала отсчета при наличии в изображении криволинейных контуров.Цель изобретения - повьааение точности формирования сигнала отсчетапри наличии в иэображении криволинейных контуров,Цель достигается тем, что в устройство Формирования сигнала отсчетадля дифференциального кодера изображений, содержащее последовательносоединенные семь блоков задержки,первый и второй сумматоры, введенывосьмой блок задержки, двенадцатьблоков вычисления модуля разностисигналов, третий и четвертый сумматоры, блок сравнения и четыре ключевых элемента, причем вход восьмого блока задержки подключен к выходу седьмого блока задержки, а к первому и второму входам первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого, двенадцатого блоков вычисления, модуля разности сигналов подключены соответственно выходи второго и третьего, третьего и четвертого, четвертого и пятого, первого и третьего, третьего и шестого, четвертого и седьмого, пер" вого и четвертого, второго и шестого, четвертого и восьмого, первого и пятого, второго и седьмого, третьего и восьмого блоков задержки, прн этом к первому, второму н третьему входам первого, второго, третьего и четвертого сумматоров подключены соответственно выходы первого, второго и третьего четвертого, пятого и шестого седьмого, восьмого и девятого десятого, одиннадцатого и двенадцатого блоков вычисления модуля разности сигналов, выходы первого, второго, третьего и четвертого сумматоров подключены к соответствую щим входам блока сравнения, первый, 906033второй, третий и четвертый выходыблока сравнения подключены к первымвходам первого, второго, третьегои четвертого ключевых элементов соответственно, а ко вторым входампервого, второго, третьего и четвертого ключевых элементов подключенысоответственно выходы первого, второго, третьего и четвертого блоковзадержки, причем восходы четырех ключевых элементов соединены между собой.На чертеже представлена структурная электрическая схема предложенного устройства,Устройство Формирования сигналаотсчета для дифференциального кодераизображений содержит первый, второй,третий, четвертый, пятый, шестой,седьмой и восьмой блоки задержки1 - 8 соответственно; первый, второй,третий, четвертый, пятый, шестой,седьмой, восьмой, девятый, десятый,одиннадцатый и двенадцатый блоки9-20 вычисления модуля разности сигналов соответственно; первый, второй,третий,и четвертый сумматоры 21,22, 23 и 24 соответственно: блок 25сравнения, четыре ключевых элемента 26, 27, 28 и 29.Устройство работает следующимобразом,На вход первого блока задержки 1поступают отсЧеты видеосигнала. Свыходов всех блоков задержки 1 - 8снимаются значения отсчетов, задержанные соответственно на один такт,на (М) такт, на М тактов, на(2 И+1) такт. Пусть изображение задано квадратной сеткой отсчетов з(в,п),где в - номер отсчета в строке(по строкам) и выполнения Функциональных преобразований,в блоках9-20 на выходе первого сумматора 21имеет сигналУ 1з(в+1) и - 1) з(в)п - 1) ++з(й, и -1)-з(в, и)1 (1)на выходе второго сумматора 22у=з (в),п -з (й,п - 1)++ з(в, п)-з(в, и) (3)на выходе четвертого сумматора 2474 щз(в, п)-з(в, и) ++з (в, и)-з (в, и)(4)Сигналы 7.) У) У и У 4 поступают соответственно на первый, вто рой, третий и четвертый входы блокасравнения 25. Блок сравнения 25Формирует управляющий сигнал на одном нз четырех своих выходов ) которому соответствует вход с наименьшимзначением У; (1=1)4), Этот управляющий сигнал открывает один из ключевых элементов 26, 27, 28 и 29, которые пропускают на выход устройствазначение задержанного видеосигналас выхода соответствующего блока задержки. Таким образом получаем оценку текущего отсчета; 0)тъ- ,) 5п 1, -1)5(,п,ю): 15 Раи Ч= ЩЮ)= 1,45 (е 1,п.) РРи Чс г)", Ч.формирование оценки текущего отсчета в соответствии с (1) в (5) позволяет получить точное предсказание значения отсчета при пересечении в процессе развертки прямолинейных контуров, ориентированных под углами 0 ) 45 ) 90 и 135 к строке.Таким образом, предложенное устройство формирования сигнала отсчета для дифференциального кодера изображений обеспечивает более высокую точность предсказания при пересечении в процессе развертки непрямолинейных контуров и при наличии %а изображении флуктуационной помехи. 8 , -) 25 30 г 35Устройство формирования сигнала отсчета для дифференциального кодера изображений, содержащее последовательно соединенные семь блоков задержки, первый и второй сумматоры, о т л и ч а ю щ е е с я . тем, что, с целью повышения точности формирования сигнала отсчета при наличии в изображении криволинейных контуров, введены восьмой блок задержки, двенадцать блоков вычисления модуля разности сигналовтретий и четвертый сумматоры, блок сравнения и четыре ключевых элемента, причем вход восьмого блока задержки подключен к выходу седьмого блока задержки, а к первому и второму входам первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого, двенадцатого блоков вычисления модуля разности сигналов подключены соответственно выходы второго и третьего, третьего и четвертого, четвертого и пятого, первого и третьего, третьего и шестого, четвертого и седьмого, первого и четвертого, второго и шестого, четверао 45 50 55 60 65 Формула изобретения906033 ИПИ Заказ 399/75 Тираж 684 Подписно иал ППП "Патент", г.ужгород, ул.Проектная,4 того и восьмого, первого и пятого,второго и седьмого, третьего и восьмого блоков задержки, при этом кпервому, второму и третьему входампервого, второго, третьего и четвер"того сумматоров подключены соответственно выходы первого, второго итретьего; четвертого, пятого и шестого, седьмого, восьмого и девятогодесятого, одиннаднатого и двенадцатого блоков вычисления модуля раэности сигналов, выходы первого, второго, третьего и четвертого сумматоров подключены к соответствующимвходам блока сравнения, первый,второй, третий и четвертый выходыблока сравнения подключены к первымвходам первого, второго, третьегои четвертого ключевых элементов соответственно а ко вторым входам первого, второго, третьего и четвертогоключевых элементов подключены соответственно выходы первого, второго,третьего и четвертого блоков задержки, причем выходы четырех ключевыхлементов соединены между собой.Источники информации,принятые во внимание прн экспертиэе1. Авторское свидетельство СССРМ 633162, кл. Н 04 Н 5/00, 1976.

СмотретьЗаявка

2824926, 02.10.1979

КУЙБЫШЕВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ АВИАЦИОННЫЙ ИНСТИТУТ ИМ. АКАД. С. П. КОРОЛЕВА

СЕРГЕЕВ ВЛАДИСЛАВ ВИКТОРОВИЧ

МПК / Метки

МПК: H04N 7/42

Метки: дифференциального, изображений, кодера, отсчета, сигнала, формирования

Опубликовано: 15.02.1982

Код ссылки

<a href="https://patents.su/3-906033-ustrojjstvo-formirovaniya-signala-otscheta-dlya-differencialnogo-kodera-izobrazhenijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство формирования сигнала отсчета для дифференциального кодера изображений</a>