Устройство для вычисления элементарных функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 890402

Автор: Кузин

Текст

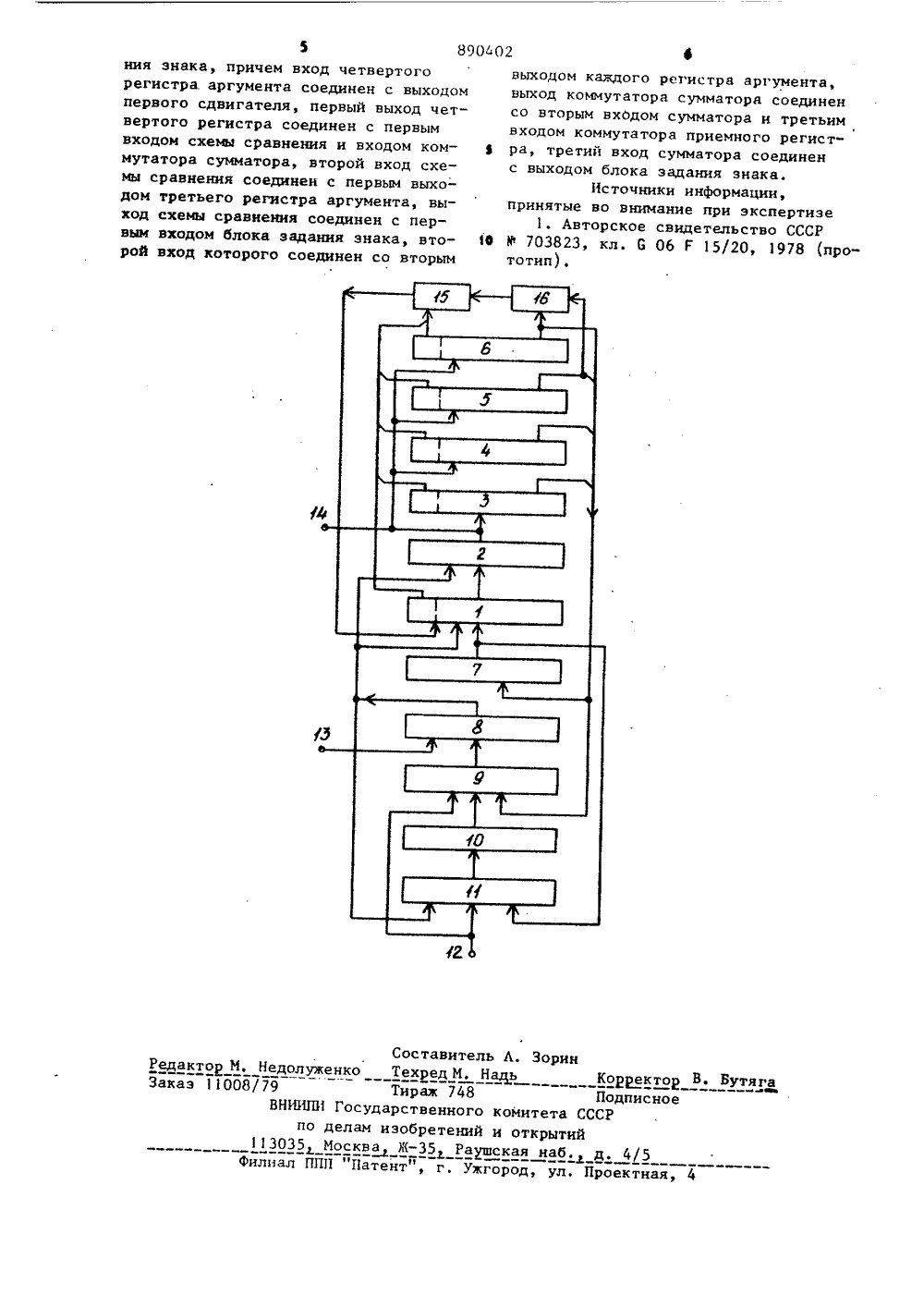

(71) Заявите 4) РОЙС ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕИЕНТАРНЫХ ФУНКЦИИ цифровойожет быть ра ровой выч лительнои машины.По основному авт.св, В 703823 известно устройство для вычисления элементарных функций, содержащее комбинационный сумматор, соединенный выходом с первым входом первого двигателя, выход которого подключен ко входам регистров и к выходу операционно 1 О го устройства, причем первые выходы регистра аргументов подключены к первому входу коммутатора буферного регистра и к первому входу входного1 коммутатора, ко второму входу которого подключен выход приемного регистра, соединенного своим, входом с выходом коммутатора приемного регистра, первый вход которого соединен с входом записи информации устройства, с тре 20 тьим входом входного коммутатора, вход буферного регистра соединен с выходом коммутатора буферного регистИзобретение отнаситс вычислительной технике использовано в составе а выход буферного регистра соединен с первым входом комбинационного сумматора, второй сдвигатель, соЕдиненный первым входом с выходом входного коммутатора, а выходом - со вторым входом комбинационного сумматора, со вторым входом коммутатора приемного регистра, со вторым входом коммутатора буферного регистра и со вторым входом первого сдвигателя, второй и третий входы второго сдвигателя соединены соответственно с первой и второй управляющими шинами устройства, вторые выходы регистра аргументов и комбинационного сумматора подключены к шине знаковых разрядов устройства, кроме того, выход буферного регистра подключен к третьему входу коммутатора приемного регистра 13.Недостатком известного устройства является низкое быстродействие.Цельюизобретения является повышение быстродействия.элемен03823,что,вия,стр ар лнител ок зад Поставленная цель достигается тем, что в устройство дополнительно введены четвертый регистр аргумента, схема сравнения н блок задания знака, причем вход четвертого регистра аргумента соединен с выходом первого сдвигателя, первый выход четвертого . регистра соединен с первым входом схемы сравнения и входом коммутатора сумматора, второй вход схемы сравне О ния соединен с первым выходом третьего регистра аргумента, выход схемы сравнения соединен с первым входом блока задания знака, второй вход которого соединен со вторым выходом 15 каждого регистра аргумента, выход коммутатора сумматора соединен со вторым входом сумматора и третьим входом коммутатора приемного регистра, третий вход сумматора соединен , 26 с выходом блока задания знака.На чертеже показана блок-схема устройства.Устройство содержит комбинационный сумматор 1, первый сдвигатель 2, 25 первый 3, второй 4, третий 5 и четвертый 6 регистры аргументов, коммутатор сумматора 7, второй сдвигатель 8, входной коммутатор 9, приемный регистр 10, коммутатор приемного регист- щ ра 11, информационный вход устройства 12, управляющий вход устройства 13, выход устройства 14, блок задания знака 5 и схему сравнения 16.Работу устройства рассмотрим на примере вычисления функции агсзпу по методу цифра эа цифрой, вычислительная процедура которого описывается формулами х х +у. ,2С 1) 40-С 1-1).с 1 - фйЯ-1;и, Сз) где 0 - угловые константы, вычисленные по формуле Я агсй 921)5 Индексхарактеризует номер итерации, причем, каждая итерация должна выполняться дважды;и - характеризует количество разрядов в числе.Оператор поворота вектора= Ф 1. Он характеризует значение знака операции н вырабатывается блоком 15.Для Функции агсэи= "1, если У( 2 н х 1 ( О, ; = +1 в против в 55 ном случае.Для выполнения сравнимости чисел у;и к введен блок 16 и допоь 24 ный регистр 6, который с учетом знака числавыдает его на схему сравнения 16 в прямом или обратном (дополнительном) коде.Начальные координаты вектора Схо = - 1/кф; у д = 0; й=О) записываются соответственно в 4, 5 и 3 регистры аргументов, а в четвертый регистр 6 записывает управляющий аргумент гу,Реализацию алгоритма целесообразно начинать с вычисления ; , что позволяет заблаговременно сформировать оператор Ц для следующей итерации.Один из операндов Формул поступает на сумматорчерез коммутатор сумматора 7, а второй через второй сдвигатель 8 и входной коммутатор 9. Для того, чтобыможно было испольэовать и при вычислении х 1, то он записывается на хранение в приемный регистр 10 через коммутаторы 7 и 11.После выполнениядвойных итераций в регистре 5 будетЪ:1 д С 1,; в регистре 4Х в 1-Ъ 605, в регистре 3уф 1 гММ Таким образом, схемная реализация формирования оператора ; позволяет уменьаить время вычисления Функции агсз 1 п на время выполнения двух ко - манд умножения, что эквивалентно по-, выюению производительности устройства на 753 по сравнению с известным.Сопутствующий экономический эффект ЗаКЛЮЧаЕтСЯ В РаС 1 ПИРЕНИИ ФУНКЦИОНаЛьных возможностей устройства, например, записав в регистр 6 третью линейную координату вектора у , а в регистры 3, 4 и 5 соответственно О, Х и У к применив дважды операцию вычисления полярных координат вектора, описанную в известном, можно вычислить пространственные координаты век- тора Устройство для вычислениятарных функций по авт.св. Уотличающееся темс целью повьппения быстродейсв него введены четвертый реггумента, схема сравнения и бл890402 ставитель Л. ЗоринхредМ. Н ь едактоо едолужен Ко екто В. Бутяга каз 11008/79 Тираж 748 По ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035 Москва Л(-35 Раушская наб. д. 4/5 филиал ППП "Патент, г. Ужгород, ул. Проектная, И 2 дписное ния знака, причем вход четвертогорегистра аргумента соединен с выходомпервого сдвигателя, первый выход четвертого регистра соединен с первымвходом схемы сравнения и входом коммутатора сумматора, второй вход схемы сравнения соединен с первым выходом третьего регистра аргумента, выход схемы сравнения соединен с первым входом блока задания знака, второй вход которого соединен со вторым выходом каждого регистра аргумента,выход коммутатора сумматора соединенсо вторым входом сумматора и третьимвходом коммутатора приемного регистФ ра, третий вход сумматора соединенс выходом блока задания знака.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР11 В 703823, кл. С 06 Г 15/20, 1978 (про"тотип).

СмотретьЗаявка

2837099, 26.10.1979

ЛЕНИНГРАДСКОЕ ОРДЕНА ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ ВЫСШЕЕ ИНЖЕНЕРНО МОРСКОЕ УЧИЛИЩЕ И АДМ. С. О. МАКАРОВА

КУЗИН ЗОТИК СЕМЕНОВИЧ

МПК / Метки

МПК: G06F 15/20

Метки: вычисления, функций, элементарных

Опубликовано: 15.12.1981

Код ссылки

<a href="https://patents.su/3-890402-ustrojjstvo-dlya-vychisleniya-ehlementarnykh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления элементарных функций</a>

Предыдущий патент: Электронная клавишная вычислительная машина

Следующий патент: Устройство для перевода выражений в польскую инверсную запись

Случайный патент: Блок проводниковых магнитных головок