Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

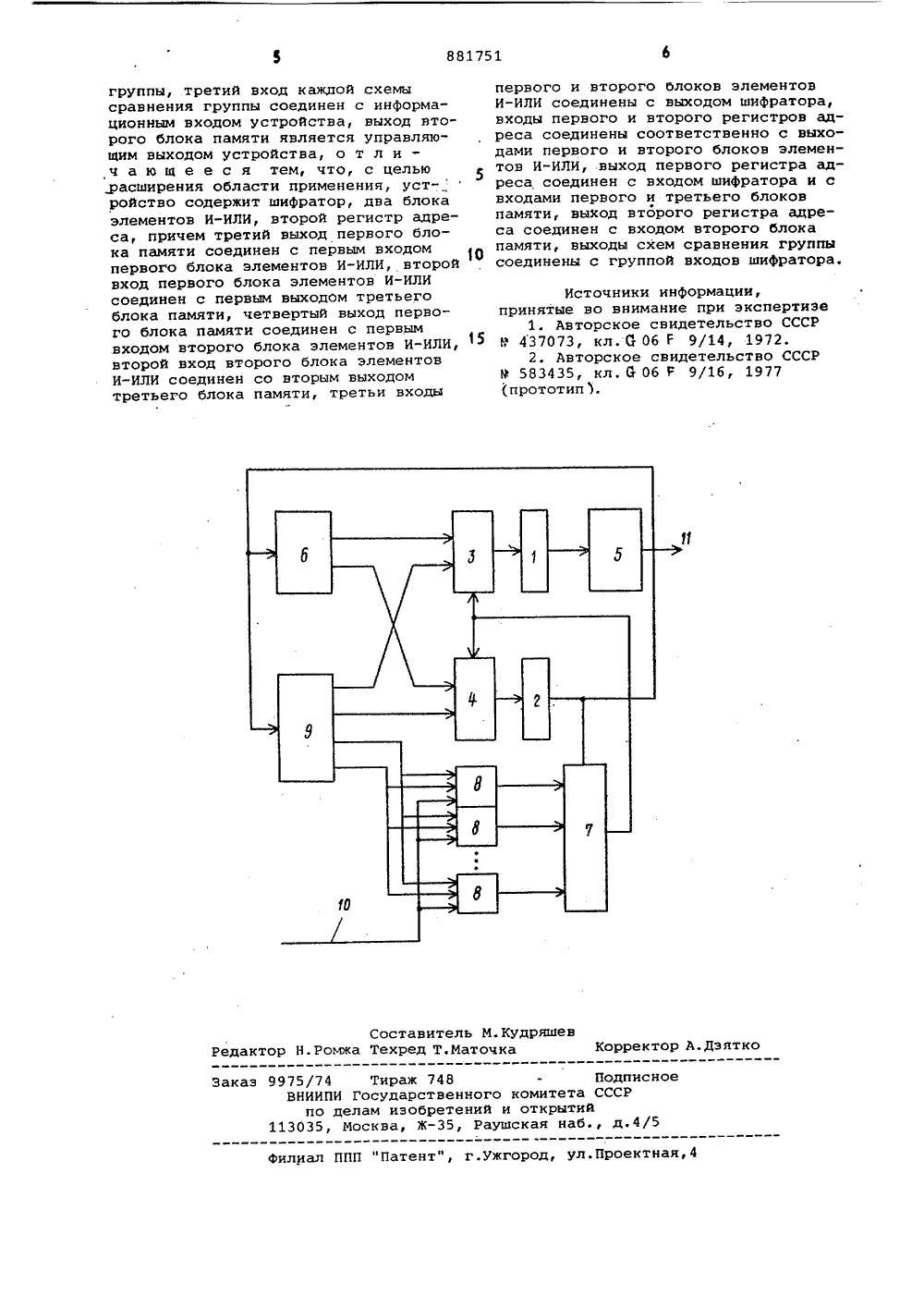

(и 881751 1) Дополнительное к ввт. сви 1) М. 1682/18 Р 9/22 явим Но с присоединение (23) Приоритет -сударствеииый комите СССР оо делам изобретений и открытий(7) Заявит 41 УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ е отнке издани много управления, содержащка,памяти, первый регистр адгруппу схем сравнения, причвторой выходы первого блокасоединены соответственно свторым входами каждой схемыния группы, третий вход каждмы сравнения группы соединемационным входом устройствавторого блока памяти являетляющим выходом устройства,шифратор, два блока элементвторой регистр адреса, причвыход первого блока памятис первым входом первого блотов И-ИЛИ, второй вход первэлементов И-ИЛИ соединен сходом третьего блока памятитый выход первого блока памнен с первым входом второгоэлементов И-ИЛИ, второй вхоблока элементов И-ИЛИ соедивторым выходом третьего блотретьи входы первого и вторков элементов И-ИЛИ соединедом шифратора, входы первогго регистров адреса соединеветственно с выходами перворого блоков элементов И-ИЛИпервого регистра адреса сое тел зов про ре- иза- око- фунство характериластью применео тсяограм(22) Заявлено 10. 01. 80 ( Изобретени осьной техни моано при со ицессоров..Известно устройство микропрограммного управления, содержащее блок памяти, усилители, дешифратор, схемувыбора, регистры адреса, схему управления, группы элементов И, группу элементов ИЛИ, триггер управления, блокобъединения признаков условного перехода 1,Недостатком такого устройства является большой объем оборудования.Наиболее близким к изобретению потехнической сущности и достигаемомурезультату является устройство многопрограммного управления, содержащееблок сравнения, три блока памяти,гисгр кода операции, блок синхронции, регистр адреса, регистр микрманды, дешифратор, формирователькциональных сигналов 21,Однако такое устройзуется ограниченной обния.Цель изобретения - расширение бласти применения устройства.Поставленная цель достигаетем, что в устройство микропр е три блореса,ем первыйпамяти/первым,сравнеой схен с инфорвыходся управвведеныов И-ИЛИ,ем третийсоединенка элеменого блокапервым вы- четверяти соедиблокад второгонен сока памяти,ого блоны с выхоо и второны соотго и втовыходдинен свходом шифратора и с входами первогои третьего блоков памяти, выход второго регистра адреса соединен с вхо"дом второго блока памяти, выходысхем сравнения группы соединены сгруппой входов шифратора.На чертеже приведена блок-схемаустройства.Устройство содержит регистры 1 и2 адреса, блоки 3 и 4 элементов И-ИЛИ,блок 5 памяти микрокоманд, блок 6 памяти адресов, шифратор 7, группу схем8 сравнения, блок 9 памяти адресов,информационный вход 10 устройства,управляющий выход 11 устройства.Устройство работает следующим образом, 15В исходном состоянии в блоки памяти 5, 6 и 9 заносится необходимаяинформация, а в адресные регистры 1и 2 - начальные адреса. В блок 5 памяти микрокоманд записываются все 2 Онеобходимые, причем различные, микрокоманды (М 1) без какого-либо повторения или дублирования.Каждое слово блока 6 памяти адресов содержит адрес текущей МК из 25блока 5 А , адрес безусловного(условного) перехода А+ . и адресблока памяти адресов . А 6 ПУказанная информация записывается вв блок 6 только в тех случаях, когдаданный переход программы к следующейМК является безусловным, т.е. не требует анализа состояния условий системы поступающих по входу 10.Каждое слово блока 9 памяти адресов содержит К адресов Ацк, составл яющих первую группу выходов блока9, К адресов безусловного (условного) перехода А+ и А вторая группа выходов блока 9 , а также векторы условий ( 9; (1 = 1 - К ), составляющих четвертую группу выходов блока 9, и векторы маски условийй;(1 = 1 - К ) (третья группа выходов) .Единичные значения разрядов М,выделяют разряды вектора Г, , которые необходимо сравнивать со значениями шин условий входа 10, РазрядыЧ;, которым в М; соответствуют "О",в сравнении не участвуют.Информация из блока 9 памяти используется только при организацииусловного перехода к следующей МКпрограммы. В этом случае выбор адреса А и А+ определяется по состоянию шин условий входа 10.Рассмотрйм работу устройства поселекции адресов,С выхода регистра 2 на управляющий вход шифратора 7 поступает адресблока памяти АБП . Если Ад = О,то шифратор 7 закрывается и на еговыходах устанавливается код "00",Поэтому блоки 3 и 4 переключаютсяна прием адресов А, АБ, А из блока 6 памяти, Если АБ, = 1, то шифратор 7 открыт и код его выхода опреде ляется результатом сравнения в схемах 8. Пусть сравнение происходит в-й схеме 8 ( =1-К). Тогда на выходе шифратора 7 появляется код, равный ), и блоки 3 и 4 переключаются на прием информации по 1 -му направлению. Тем самым выполняется селекция адресов Ац, А+ ,.А 9, иэ блока 9 памяти.Рассмотрим, как выбирается на-. правление перехода программы. В каждой схеме 8 значение условий входа 10 сравнивается с одними из векторов ;,под вектором маски Й;Так как для любой пары направлений перехода в произвольной графе программы существует хотя бы одно общее условие перехода, то совпадение одного из векторов условий Ч; с состоянием входа 10 может произойти только в одной схеме сравнения 8. Это совпадение и определяет адреса А, А, А,п, которые должны быть использованы при данном условном переходе к следующей МК программы.Устройство работает следующим образом.В каждом такте работы из блоков 5,6 и 9 памяти по адресам А (регистр 1) и А+ ( регистр 2 ) одновременно считается следующая информация: иэ блока 5 памяти - текущая микрокоманда, подлежащая выполнению, из блока 6 памяти возможны следующие адреса Аи, А Ап, из блока 9 памяти набор возможнйх следующих адресов Ац, А, АБ, а также надзор векторов условий( 9;) и маски ( М;) .Затем в схемах 8 происходит сравнение набора( 9) с состоянием условий входа 10 и выбирается направление условного перехода программы ( если А на выходе регистра 2 равен 1) , т.е. с помощью блоков 3 и 4 на входы регистра 1 подается следующий адрес Ам, а на входе регистра 2 - следующие адреса А Ап . В случае, когда переход к следующей МК является безусловным (т,е. А = 0 на выходе регистра 2), блоки 3 и 4 принимают информацию с выходов блока 6 памяти.В конце рабочего такта выбранные адреса А, А, Ащ записываются в адресные регистры 1 и 2. После этого рабочий такт закончен.Применение изобретения позволяет расширить область применения устройства.Формула изобретенияУстройство микропрограммного управления, содержащее три блока памяти, первый регистр адреса, группу схем сравнения, причем первый, второй выходы первого блока памяти соеднены соответственно с первым, вторым входами каждой схемы сравнения881751 Составитель М.Кудряшеведактор Н.Ромжа Техред Т.Маточка Корректор А.Дзятк Заказ 9975/74 Тираж 748 ВНИИПИ Государственного по делам изобретений 113035, Москва, Ж, Раушсное Подкомитета СССоткрытийская наб., д.4/ П "Патент", г.ужгород, ул.Проектная,ли группы, третий вход каждой схемысравнения группы соединен с информационным входом устройства, выход второго блока памяти является управляющим выходом устройства, о т л ивч а ю щ е е с я тем, что, с целью.расширения области применения, устройство содержит шифратор, два блокаэлементов И-ИЛИ, второй регистр адреса, причем третий выход первого блока памяти соединен с первым входомпервого блока элементов И-ИЛИ, второйвход первого блока элементов И-ИЛИсоединен с первым выходом третьегоблока памяти, четвертый выход первого блока памяти соединен с первымвходом второго блока элементов И-ИЛИ,второй вход второго блока элементовИ-ИЛИ соединен со вторым выходомтретьего блока памяти, третьи входы первого и второго блоков элементовИ-ИЛИ соединены с выходом шифратора,входы первого и второго регистров адреса соединены соответственно с выходами первого и второго блоков элементов И-ИЛИ, .выход первого регистра адреса соединен с входом шифратора и свходами первого и третьего блоковпамяти, выход второго регистра адреса соединен с входом второго блокапамяти, выходы схем сравнения группысоединены с группой входов шифратора. Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРР 437073, кл. 6 06 Е 9/14, 1972.2. Авторское свидетельство СССРР 583435, кл. 6 06 Р 9/16, 1977

СмотретьЗаявка

2871682, 10.01.1980

ПРЕДПРИЯТИЕ ПЯ В-2655

ИЛЬИН АНАТОЛИЙ АНАТОЛЬЕВИЧ, КАЛИНЧЕВ СЕРГЕЙ СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 15.11.1981

Код ссылки

<a href="https://patents.su/3-881751-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство для распределения потоков информации

Случайный патент: Способ гибки по окружности