Устройство для суммирования одноразрядных двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 817700

Автор: Кайма

Текст

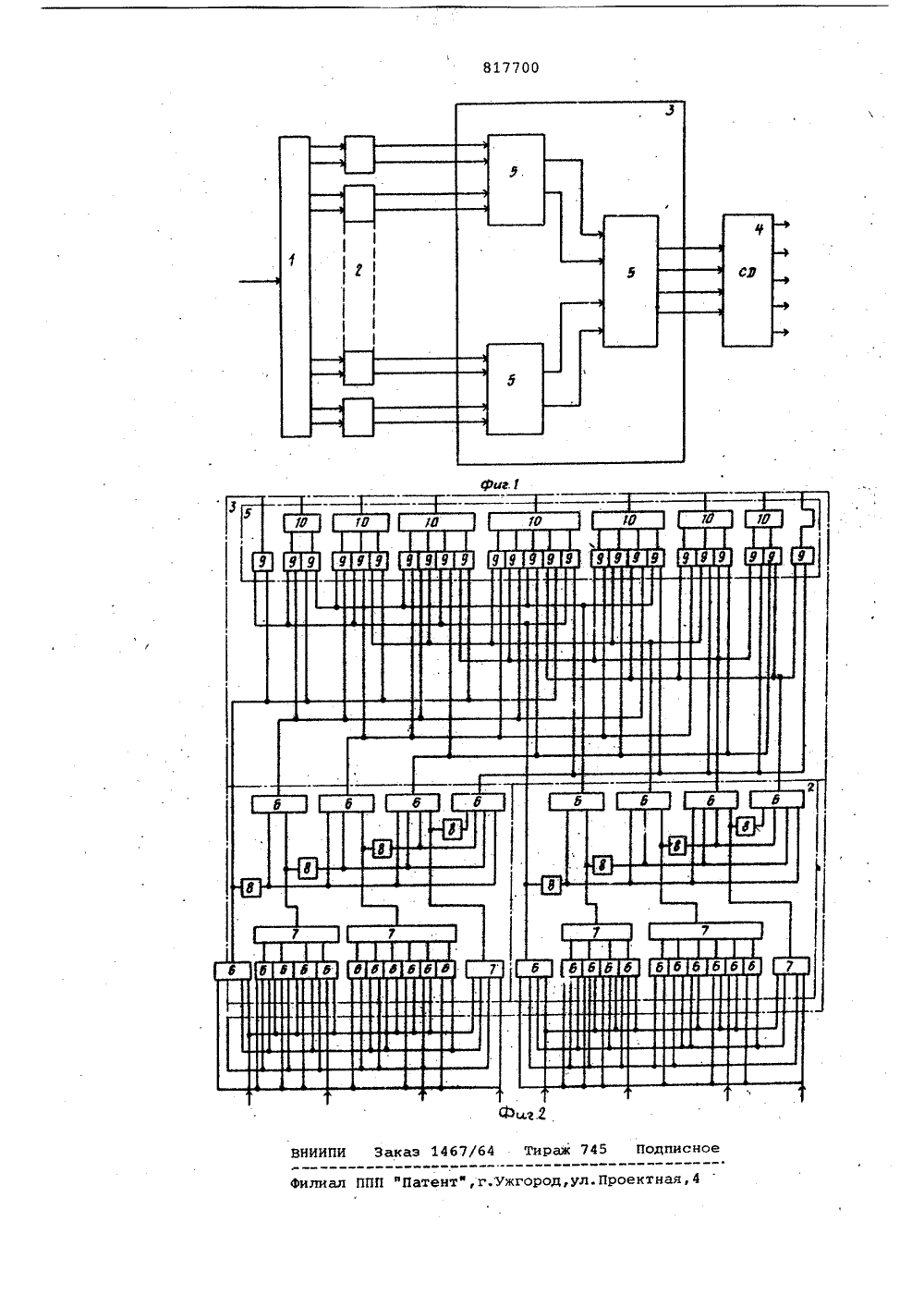

ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОУСКЬМУ СВИ ОИЛЬСТВУ Союз Советских Социалистических Рвслублнк(22) Заявлено 2805,79 (21) 2770671/18-24с присоединением заявки Йо(51)М. Кл.з 6 06 Г 7/50 Государствениый комитет СССР по делам изобретевий и открытий(54) УСТРОИСТВО ДЛЯ СУММИРОВАНИЯ и ОДНОРАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ Изобретение относится к вычислительной технике и может найти применение в средствах связи, автоматикии телемеханике.Известны устройства для суммирования одноразрядных двоичных чисел(параллельные счетчики), построенныес помощью одноразрядных двоичныхполусумматоров или сумматоров 11 .Наиболее близким к предлагаемомуявляется устройство для суммирования и одйоразрядных двоичных чисел,применяемое при ускоренном умножениии представляющее собой многокаскадную суммирующую схему из трехвходовых одноразрядных двоичных сумматоров 2 .Недостатком известных устройствявляется невысокое быстродействие.Цель изобретения - повышение быестродействия,Поставленная цель достигаетсятем, что устройство для суммированияи одноразрядных двоичных чисел содержит в преобразователей двоичныхкодов в унитарные коды количестваединиц (вПк,где М - количествовходных шин устройства, образующиходну группу 1 в - количество группвходных шин устройства), блок сумми рования представляет собой узел суммирования а унитарных кодов и двоичный шифратор, выходы которого подключены к выходным шинам устройства,а.входы подключены к выходам узласуммирования унитарных кодов, входыкоторого подключены к выходам соответствующих преобразователей двоичных кодов в унитарные коды, входикаждого из которых соединены с свходными шинами устройства.Кроме того, узел суммирования уни.тарных кодов содержит сумматоры унитарных кодов, образующих пирамидуЙэ 1092 тл рядов, причем сумматорыунитарйых кодов первого ряда, соединены со входами узла суммирования унитарных кодов, взятыми попарно, сумматор каждого последующего ряда соеди О нен входами с выходами попарновзятых сумматоров предыдущего ряда, выход сумматора последнего ряда является выходом узла суммирования а унитарных кодов.На фиг. 1 представлена схема устройства, на фиг. 2 - пример выполнения преобразователей двоичных кодовв унитарные коды и узла суммирования унитарных кодов при е2, 30 :" М узел суммирования в этом случаесодержит единственный сумматор унитарных кодов).Устройство содержит регистр 1, вкотором записано исходное и-разрядноедвоичное слово (й одноразрядных двоичных чисел), и собственно образующие устройство преобразователи 2двоичных кодов в унитарные коды, узел3 суммирования унитарных кодов и шифратор 4. Узел 3 суммирования унитарных кодов выполнен в виде пирами-,ды сумматоров 5 унитарных кодов.П р и м е р,При выполнении преобразователей 2 и узла 3 для случая . в.ю 2, М 4, я = в М = 8, устройствосодержит два преобразователя 2 двоичных кодов в унитарные коды, выполненные на элементах И 6, ИЛИ 7,НЕ 8, и в состав узла 3 суммирования унитарных кодов входит в этомслучае единственный сумматор 5 унитарных кодов, выполненный в виде матрицы двухвходовых элементов И 9,выходы элементов И 9, каждой диагонали матрицы объединены одним элементом ИЛИ 10. Каждый иэ двух преобразователей 2 преобразует двоичную четырехразрядную комбинацию на своемвходе в сигнал на одном из своихпяти выходов, наличие которого указывает, сколько единиц содержится во.входной комбинации,Устройство работает следующим образом.Перед началом суммирования и одноразрядные двоичные числа в видеи"разрядного двоичного слова занесены в регистр 1. Разряды регистра 1разбиты на в групп поразрядов вкаждой (е к и). Выходы каждой группы разрядов регистра 1 подключеныко входам соответствующего преобразователя 2 двоичного кода в унитарный, 40который преобразует двоичное представление данной группы двоичных разрядов в сигнал на одном из своих выходов. Образованные таким образом щунитарных кодов суммируются узлом 3(построенным, например, по пирамидальной схеме) . Результат образованный на выходе узла 3 в унйтарном коде, преобразуется двоичным шифратором 4 в параллельный двоичный код,значение которого показывает числоразрядов регистра 1, в которых былозаписано значение "1". Входами устройства являются входы преобразователей 2, а выходами - выходы шифратора 4. 55Используя для построения преобразователей 2, узла 3 и шифратора 4 логические элементы с задержкой наносекундного диапазона, быстродействие для подсчета количества единиц в 8- 16-, 32,-64-, и 128-разрядных словах составляет соответственно 12, 16,.20, 24 и 28 нс, что примерно в 2-3 раза выше, чем в известном устройстве одноразрядные сумматоры которого, образующие многокаскадную схему, выполнены на таких же элементах, Объем оборудования предлагаемого и известного устройств примерно одинаков.формула изобретения1. Устройство для суммирования иодноразрядных двоичных чисел, содержащее блок суммирования, о т л ич а ю щ е е с я тем, что с цельюповышения быстродействия, оно содержит в преобразователей двоичных кодов в унитарные коды количества единиц (в =п(к,где 1 - количество входных шин устройства, образующих однугруппу, щ - количество групп входныхшин устройства), блок суммированияпредставляет собой узел суммирования а унитарных кодов и двоичный шифратор,выходы которого подключены квыходным шинам устройства, а входыподключены к выходам узла суммирования унитарных кодов, входы которогоподключены к выходам соответствующих преобразователей двоичных кодовв унитарные коды, входы каждого изкоторых соединены с Е входными шинами устройства.2. Устройство по п1, о т л ич а ю щ е е с я тем, что узел суммирования.унитарных кодов содержит сумматоры унитарных кодов, образующихпирамиду из 1 о 9е рядов, причем сумматоры унитарных кодов первого рядасоединены со входами узла суммирования унитарных кодов, взятыми попарно,.сумматор каждого последующего ряда соединен входами с выходами попарно взятых сумматоров предыдущего ряда, выход. сумматора последнего рядаявляется выходом узла суммированияв унитарных кодов.Источники информации,принятые во внимание при экспертизе1. Мелкумян Д.О. Синтез параллельного счетчика и его оптимизация,

СмотретьЗаявка

2770671, 28.05.1979

ПРЕДПРИЯТИЕ ПЯ А-3706

КАЙМА АНАТОЛИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 7/50

Метки: двоичных, одноразрядных, суммирования, чисел

Опубликовано: 30.03.1981

Код ссылки

<a href="https://patents.su/3-817700-ustrojjstvo-dlya-summirovaniya-odnorazryadnykh-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для суммирования одноразрядных двоичных чисел</a>

Предыдущий патент: Сумматор п-разрядных комплексныхчисел

Следующий патент: Устройство для умножения

Случайный патент: Прибор для определения неравномерности вращения вала и линейной скорости отдельных точек механизмов