Устройство для генерирования сигналовзаданной формы

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 811237

Автор: Кренев

Текст

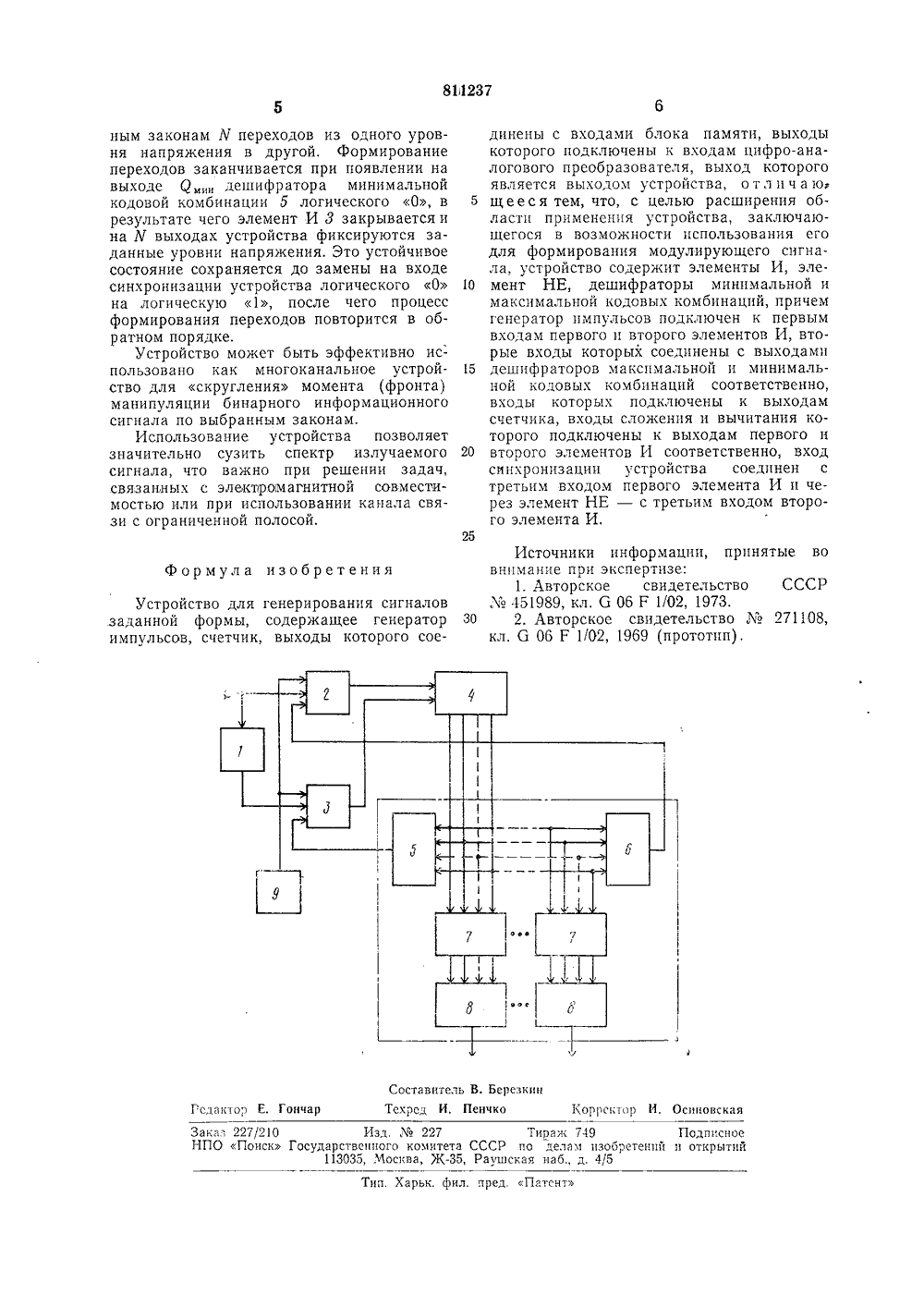

Союз Советских Социалистических Республик(45) Дата опубликования описания 10.03.81Государственный комитет по делам изобретений и открытий(72) Автор изобретения А, Н, Кренев Я росл авский Государственный университет,(54) УСТРОЙСТВО ДЛЯ ГЕНЕРИРОВАНИЯ СИГНАЛОВ ЗАДАННОЙ ФОРМЫИзобретение относится к вычислительной технике и может найти применение в области радиосвязи для получения модулирующего сигнала из исходного бинарного сигнала для систем передачи дискретной информации с ограниченным спектром.Известны цифровые генераторы, содержащие преобразователь временного интервала в последовательность импульсов, блок весовых коэффициентов, выходной реверсивный счетчикрегистр, блок деиодирования линейных участков аппроксимации, блок памяти 1). Использование операций умножения и деления в таком генераторе функций ограничивает его быстродействие.Наиболее близким к изобретению является устройство для генерирования сигналов заданной формы, содержащее соединенныс между собой генератор импульсов, счетчик, а в цепи между выходом устройства и выходом счетчика последовательно включены цифро-аналоговый преобразователь и преобразователь двоичных сигналов 21,Однако данное устройсто нельзя использовать для формирования модулирующего сигнала в системах передачи дискретной информации с ограниченным спектром. При непосредственном использовании бинарного цифрового сигнала в качестве модулпрующсго получаемые сигналы занимают значительную полосу частот. Получаемый радиосигнал занимает гораздо меньшую полосу частот при условии сглаживания фронтов (моментов) манипуляции цифрово го модулирующего сигнала по определенному закону.Целью изобретения является расширение области применения устройства, заключающееся в возможности его использования 10 для формирования модулирующего сигнала.Для этого устройство для генерированиясигналов заданной формы, содержащее генератор импульсов, счетчик, выходы кото рого соединены с входами блока памяти,выходы которого подключены к входам цпфро-аналогового преобразователя, выход которого является выходом устройства, содержат элементы И, элемент НЕ, дешифраторы минимальной и максимальной кодовых комбинаций, причем генератор импульсов подключен к первым входам первого и второго элсмснтов П, вторые входы которых соединены с выходамп дешифраторов мак спмальной и минимальной кодовых комбинаций соответственно, входы которых подключены к выходам счетчика, входы сложения и вычитания которого подключены и выходам первого и второго элементов И соЗ 0 отвстственно, вход синхронизации устрой5 О 15 20 25 30 35 40 45 50 60 65 ства соединен с третьим входом первого элемента И и через элемент НЕ - с третьим,входом элемента И.Необходимо отметить, что в зависимости от конкретного вида модуляции и используемого модулятора может потребоваться различное число синхронных сигналов, изменяющихся по определенным и разным законам. Поэтому, вообще говоря, к выходу счетчика может быть параллельно подключено различное число блоков памяти, выход каждого будет подключен к выходу устройства через свой цифро-аналоговый преобразователь. Устройство в этом случае будет многоканальным,На чертеже представлена блок-схемаустройства.Устройство содержит элемент НЕ 1,вход которого соединен с входом синхронизации устройства (па который поступает информационный сигнал -- последовательный бинарный код), элемент И 2, вход которого соединен с входом синхронизации устройстга, элемент И 3, вход которого соединен с выходом элемента НЕ 1. С помощью элемента НЕ 1 и элементов И 2, 3 осуществляется синхронизация устройства внешним информационным сигналом. Выход элемента И 2 соединен с входом сложения реверсивного счетчика 4, а выход элемента И 3 - с входом вычитания реверсивного счетчика 4. Выходы всех разрядов счетчика 4 соединены с входамп дешифратора минимальной кодовой комбинации 5, дешифратора максимальной кодовой,комби-.нации б и в общем случае с Л блоков памяти 7, выходы которых подключены и входам цифро-аналоговых преобразователей 8 соответственно, выходы которых являются выходамп устройства.С помощью данного устройства осуществляется формирование (сглаживание) момента фронта манипуляции информационногого сигнала по Л требуемым законам.Блоки памяти выполняют роль функциональных кодовых преобразователей, где каждому коду адреса считывания ставятся в соответствие выходные коды большей разрядности, находящиеся в линейной зависимости с требуемыми значениями напряжения выходных сигналов формирователя.Таким ооразом, выходы всех разрядовсчетчика 4 соединены с соответствующими входами дешифраторов мшшмальпой 5 и максимальной б кодовых комбинаций и с адресными входами У блоков памяти 7, выходы которых соединены с соответствующими входами У цифро-аналоговых прсооразоватслей 8, выходы которых являются выходами формирователя. Причем выход Ядешпфратора минимальной кодовой комбинации 5 соединен с входом элемента И 3, а выход дешифратора максимальной кодовой комбинации б соединен с входом элемента И 2. Выход генератора импульсовподключен к входам элементов И 2 и 3,Устройство работает следующим образом. На вход синхронизации устройства подастся бинарный сигнал, несущий информацию, а с выхода генератора импульсов 9 следуют тактовые импульсы с периодом нс1больше, чем длительности самого короткого информационного импульса (где lг - число разрядов счетчика 4). Если в первый момент времени после включения счетчик 4 находится в промежуточном состоянии (пе в экстремальном), то с выхода Ядеп.пфратора минимальной кодовой комбинации 5 и с выхода Я.,., дсшпфратора максимальной кодовой комбинации б на входы элементов И 2 и 3 воздействует логическая 1, Допустим, что в момент включения на вход синхронизации устройства воздействовали логическая 1, тогда тактовые импульсы проходят на вход сло:ксппя реверсивного счетчика 4 через элемент И 2. По мере поступления тактовых импульсов па ревсрспвный счетчик 4 на адресные входы У блоков памяти 7 поступает сигнал с соответствующих выходов счетчика 4, который подается также на входы дешифраторов экстремальных кодовых комбинаций 5 и б, Блоки памяти 7 осуществляют функциональное преобразование двоичного кода реверсивного счетчика 4 в У кодов большей разрядности, линейно связанных с требуемыми значениями выходных напряжений у стройства. Кодовые комбинации с выходов блоков памяти 7 подаются на соответствующие входы цифроаналоговых преобразователей 8, осуществляющих линейное преобразование этих комбинаций в У напряжений с последующей фильтрацией пар азитпых спектральных составляющих тактовой частоты. После достижения полного заполнения реверсивного счетчика 4 сигнал на выходе Я, дешифратора максимальной кодовой комбинации б заменяется на лопгческий О, а на выходе Ядешифратора минимальной кодовой комбинации остается логическая 1, в результате чего оба элемента И 2 и 3 закрыты и тактовые импульсы на реверспвный счетчик 4 пе поступают, На выходе устройства фиксируются экстремальные напряжения. Устойчивое состояние схемы устройства сохраняется до замены на входе синхронизации устройства логической 1 па лопгчсскпй О. В этом случае элемент И 2 остается в закрытом состоянии, а па первом входе элемента И 3 после инвертирования элементом НЕ 1 лопгческпй О заменяется на логическую 1 и элемент И 3 открывается, Тактовые импульсы, проходя через него, воздейстзуют на вход вычитания реверсивного счетчика 4, и на выходе устропства формируется по задан811237 Составитель В. БерезкинТерод И, Пеичко ректор И. Осиповская Редактор онча Подписное ннй и открытийЗакал 227/210 НПО Поиск Изд. Мо 227венного комитета СССР п 5, Москва, Ж, Раушска раж (49 делам нзобр наб., д. 4/5 арс 113 Тип. Харьк. фил. пред. Патснт ным законам У переходов из одного уровня напряжения в другой. Формирование переходов заканчивается при появлении на выходе Янв дешифратора минимальной кодовой комбинации 5 логического О, в результате чего элемент И д закрывается и на У выходах устройства фиксируются заданные уровни напряжения. Это устойчивое состояние сохраняется до замены на входе синхронизации устройства логического О на логическую 1, после чего процесс формирования переходов повторится в обратном порядке.Устройство может быть эффективно использовано как многоканальное устройство для скругления момента (фронта) манипуляции бинарного информационного сигнала по выбранным законам.Использование устройства позволяет значительно сузить спектр излучаемого сигнала, что важно при решении задач, связанных с электромагнитной совместимостью или при использовании канала связи с ограниченной полосой. Формула изобретения Устройство для генерирования сигналов заданной формы, содержащее генератор импульсов, счетчик, выходы которого соединены с входами блока памяти, выходы которого подключены к входам цифро-аналогового преобразователя, выход которого является выходом устройства, о т л и ч а ю;5 щ е е с я тем, что, с целью расширения области применения устройства, заключающегося в возможности использования его для формирования модулирующего сигнала, устройство содержит элементы И, эле мент НЕ, дешифраторы минимальной имаксимальной кодовых комбинаций, причем генератор импульсов подключен к первым входам первого и второго элементов И, вторые входы которых соединены с выходами 15 дешифраторов максимальной и минимальной кодовых комбинаций соответственно, входы которых подключены к выходам счетчика, входы сложения и вычитания которого подключены к выходам первого и 20 второго элементов И соответственно, входсинхронизации устройства соединен с третьим входом первого элемента И и через элемент НЕ - с третьим входом второго элемента И.25 Источники информации, принятые вовнимание при экспертизе:1. Авторское свидетельство СССРМ 451989, кл. б 06 Е 1/02, 1973.30 2. Авторское свидетельство ЪЪ 271108,кл. й 06 Р 1/02, 1969 (прототпп).

СмотретьЗаявка

2622674, 01.06.1978

ЯРОСЛАВСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ

КРЕНЕВ АЛЕКСАНДР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 1/02

Метки: генерирования, сигналовзаданной, формы

Опубликовано: 07.03.1981

Код ссылки

<a href="https://patents.su/3-811237-ustrojjstvo-dlya-generirovaniya-signalovzadannojj-formy.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для генерирования сигналовзаданной формы</a>

Предыдущий патент: Термозависимый источник опорногонапряжения

Следующий патент: Устройство для оптимального управле-ния многоканальными автоматическимилиниями

Случайный патент: Способ сушки гранулированной сажи