Устройство для вычисления элементарнойфункции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

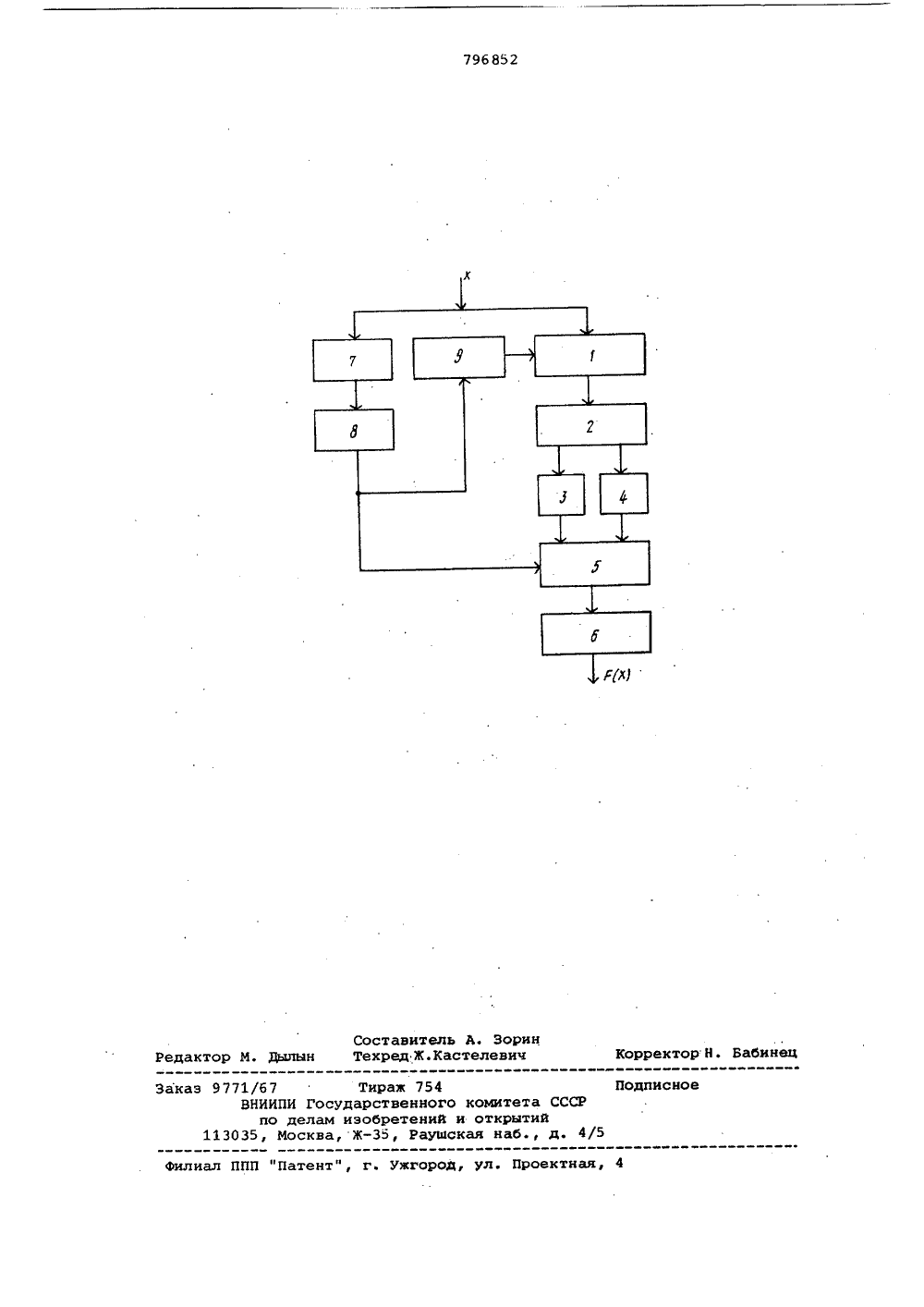

Союз Советских Соцналнстнческнх РеслублнкОПИСАНИЕ щИЗОБРЕТЕНИЯК АВТОРСКОМУ СВ ИТИЛЬСТВУ(22) Заявлено 08.02.79 (21) 2722 Ь 94/18-24 (51)М. Кл. с присоединением заявки йо(23) Приоритет В 06 С 15/З 1 ГосударствеииыИ комитет СССР во дедам изобретеииИ и открытиИ(71 Заявитель Ленинградский ордена Ленина электротехнический институт им. В. И. Ульянова (Ленина)(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНОЙФУНКЦИИ ргу 10 Изобретение относится к вычислительной технике и может применяться в качестве дополнительного спецпроцессора большой и мини-ЭВМ и как самостоятельный генератор функций в автоматизированных системах,Известен цифровой интерполятор, содержащий регистр для хранения а мента, постоянные запоминающие ус ройства для хранения параметров аппроксимации и арифметический блок для вычисления функций 1.Наиболее близким по технической сущности к предлагаемому является 15 цифровое устройство для получения начального приближения к обратной величине, содержащее регистр аргумента, первый и второй блоки памяти, блок умножения и сумматор, причем 20 выходы регистра аргумента подключены ко входам первого и второго блоков памяти, выход первого блока памяти подключен к первому входу бло-ка умножения, выход которого соеди нен со входом сумматора, выход которого является выходом устройства 2 .Недостатком этого устройства является невозможность реализации широкого класса вычисляемых функций. 30 Целью изобретения - расширение класса решаемых задач за счет возможности вычисления любых непрерывных элементарных функций.Поставленная цель достигается тем, что в устройство, содержащее регистр аргумента, первый и второй блоки памяти, блок умножения и сумматор, причем выходы регистра аргумента подключены ко входам первого и второго блоков памяти, выход первого блока памяти подключен к первому входу блока умножения, выход которого соединен со входом сумматора, выход которого является выходом устройства, дополнительно введены на" капливающий сумматор, дешифратор, регистр сдвига и генератор одиночных импульсов, при этом вход устройства подключен ко входам дешифратора и накапливающего сумматора, выходы которых подключены ко входам регистра сдвига и регистра аргумента соответственно, выход регистра сдвига подключен ко входу генератора оди" ночных импульсов, выход знакового. разряда регистра сдвига соединен с управляющим входом блока умножения, второй вход которого соединен с выходом второго блока памяти, выход5 30 15 20 25 30 35 40 45 0 55 генератора одиночных импульсов соединен с младшим разрядом накапливающего сумматора.На чертеже представлена блок-схема устройства.Она содержит накапливающий сумматор 1, регистр 2 аргумента, первыйи второй блоки 3 и 4 памяти, блок 5умножения, сумматор б, дешифратор 7,регистр 8 сдвига, генератор 9 одиночных импульсов.Воспроизводимая устройством функция вычисляется по формуле усеченного ряда(К ЧК Фгде ф КК 1 - базисные функции (двойные интегралы функцииУолша),С - коэффициенты ряда, которые для каждой заданнойфункции Г(х) вычисляютсязаранее и записываются вблок 4 памяти,Устройство работает следующим образом.Цикл вычислений начинается с передачи аргумента на дешифратор 7,определяющий число членов ряда, и внакапливающий сумматор 1, которыйвначале обнулен. Аргумент поступаетна вход дешифратора, а на выходев параллельном коде выдается числочленов ряда,.Параллельный код поступает на регистр 8 сдвига и преобразуется в последовательный. Числозначащих разрядов в последовательномкоде и есть число членов ряда. Разряд последовательного кода, представляющего собой последовательностьдвоичных единиц и нулей, поступаетна знаковый разряд блока умножения и(формирует знак произведения СК икк) . Одновременно генератор 9 одиничных импульсов с каждым текущимразрядом последовательного кода вырабатывает двоичную единицу, котораяпоступает в младший разряд накапливающего сумматора 1, где она суммируется со значением аргумента и гдеформируется адрес следующих сомножителей С," и ц), Х) . По коду аргумента, переданного из накапливающегосумматора 1 в регистр 2 аргумента,производится выбор базисной кусочноквадратичной функции из блока 4 памяти и коэффициентов разложения из блока 3 памяти. В блоке 5 производитсяумножение функции ц Х) на соответствующий ей коэффициент Ск и ихКпроизведение поступает с необходимымзнаком на вход сумматора б для накопления сумы согласно формуле (1). Пос ле формирования первой сум(ы по указанному выше алгоритму формируются вторая, третья и т. д. Тем самым происходит воспроизведение заданной функции.Технические преимущества устройства по сравнению с известными заключаются в широком классе функций, им воспроизводимых. Реализация устройства на современных дешевых интегральных микросхемах дает значительный экономический эффект при серийном выпуске. С помощью устройства можно воспроизводить функции очень широкого класса (все известные непрерывнйе элементарные функции) - тригоНометрические, обратные тригонометрические, полиномиальные, экспоненциальные, логарифмические и др.Формула изобретенияУстройство для вычисления элементарной функции, содержащее регистр аргумента, первый и второй блоки памяти, блок умножения и сумматор причем выходы регистра аргумента подключены ко входам первого и второго блоков памяти, выход первого блока памяти подключен к первому входу блока умножения, выход которого соединен со входом сумматора, выход которого является. выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения класса решаемых задач за счет воэможности вычисления любых непрерывных элементарных функций, в него введен накапливающий сумматор, дешифратор, регистр сдвига и генератор одиночных импульсов, при этом вход устройства подключен ко входам дешифратора и накапливающего сумматора, выходы которых подключены ко входам регистра сдвига и регистра аргумента соответственно, выход регистра сдвига подключен ко входу генератора одиночных импульсов, выход знакового разряда регистра сдвига соединен с управляющим входом блока умножения, второй вход которого соединен с выходом второго блока памяти, выход генератора одиночных импульсов соединен с младшим разрядом накапливающего сумматора.Источники информации,принятые во внимание при экспертизе1. Патент США Р 3813529,кл. 235-152, 19742. Авторское свидетельство СССРР 318940, кл. 6 06 Г 7/38, 1970796852 Составитель А, Зоринн Техред Ж.Кастелевич Корректор Н. Бабинец Редакто 9771/б 7 Тираж 754ВНИИПИ Государственного комитетапо делам изобретений и открыти 13035, Москва, Ж, Раушская наб.,аказ одписное 4 5 филиал ППП "Патент", г. УжгороД, ул. Проектная,

СмотретьЗаявка

2722694, 08.02.1979

ЛЕНИНГРАДСКИЙ ОРДЕНА ЛЕНИНА ЭЛЕКТРО-ТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. B. И. УЛЬЯНОВА

БАЛАШОВ ЕВГЕНИЙ ПАВЛОВИЧ, СМОЛОВ ВЛАДИМИР БОРИСОВИЧ, СВИНЬИН СЕРГЕЙ ФЕДОРОВИЧ, СМАГИН АЛЕКСЕЙ АРКАДЬЕВИЧ

МПК / Метки

МПК: G06F 17/10

Метки: вычисления, элементарнойфункции

Опубликовано: 15.01.1981

Код ссылки

<a href="https://patents.su/3-796852-ustrojjstvo-dlya-vychisleniya-ehlementarnojjfunkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления элементарнойфункции</a>

Предыдущий патент: Генератор экспоненциальной функции

Следующий патент: Цифровой резонатор

Случайный патент: Бортовое сцепное устройство судов