Параллельно-последовательный аналогоцифровой преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

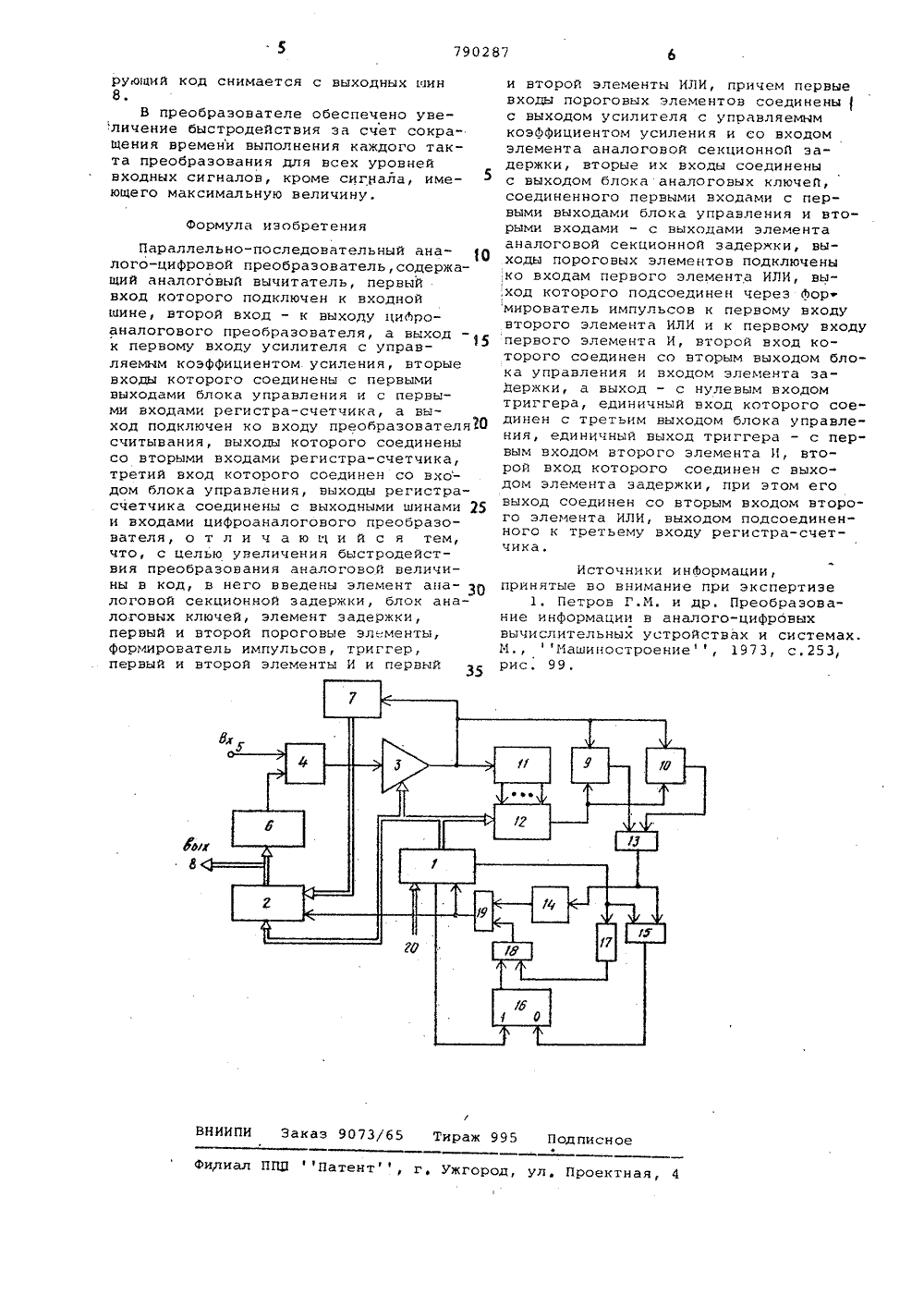

Союз Советскнк Соцналнстнческнк Республик(22) Заявлено 010878 (21) 2650586/18-21с присоединвнием заявки Йо(5)М. Кл. Н 03 К 13/03 Государственный комитет СССР ло делам изобретений и открытий(54) ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ Изобретение относится к преобразователям аналоговых сигналов в цифровые с повышенным быстродействием и, н частности, предназначено для построения ,на его основе систем сбора аналоговой 5 информации для управляющих вычислительных комплексов.Известен преобразователь, содержащий аналоговый вычитатель, усили" тель с управляемым коэффициентом уси-(О ления, преобразователь считывания, цифроаналоговый преобразователь, регистр-счетчик и блок управленияПри этом управляющая шина блока управления соединена с управляющими 15 входами регистра-счетчика и усилителя, вход которого соединен через аналоговый вычитатель с входной шиной и с выходом цифроаналогового преобразователя, выход - через преобразонатель 20 считывания с кодовыми входами регистра-счетчика, кодовыми выходами подсоединенного к кодовым входам цифроаналогового преЬбразователя, а входом параллельной записи кода - к 25 блоку управления 1 .В этой схеме имеется один преобразователь считынания и с его помощью последовательно по тактам определяются группы разрядов Время выполнения 30 этих тактов определяется переходным процессом усилителя, как самого инерционного узла иэ всех элементов схемы, Для всех уровней входных сигналов время выполнения такта преобразования остается неизменным и устанавливается исходя иэ наиболее длительного переходного процесса усилителя. Это приводит к дополнительным затратам времени при выполнении преобразования. На устранение этого недостатка направленно данное предложение.Цель изобретения - увеличение быстродействия преобразования аналоговой величины в код.Посталенная цель достигается тем, что в параллельно-последовательный аналого-цифровой преобразователь, содержащий аналоговый вычитатель, первый вход которого подключен к входной шине, второй вход - к выходу цифроаналогового преобразователя, а выход к первому входу усилителя с управляемым коэффициентом усиления, вторые входы которого соединены с первыми выходами блока управления и первыми входами регистра"счетчика, а выход подключЕн ко входу преобразователя считывания, выходы которого соединенысо вторыми входами регистра-счетчика,третий вход которого соединен со входом блока управления, выходы регистрасчетчика соединены с выходными шинамии входами цифроаналогового преобразователя, введены элемент аналоговойсекционной задержки, блок аналоговыхключей, элемент задержки, первый и второй пороговые элементы, формировательимпульсов, триггер, первый и второйэлементы И и первый и второй элементыИЛИ, причем первые входы пороговыхэлементов соединены с выходом усилителя с управляемым коэффициентом усиления и со входом элемента аналоговойсекционной задержки, вторые их входысоединены с выходом блока аналоговых 15ключей, соединенного первыми входамис первыми выходами блока управления ивторыми входами с выходами элементааналоговой секционной задержки, выходы подключены ко входам первого эле-щмента ИЛИ, выход которого подсоединенчерез формирователь импульсов к первому входу второго элемента ИЛИ и кпервому входу первого элемента И,второй вход которого соединен со вторым выходом блока управления и входомэлемента задержки, а выхоц - с нулевым входом триггера, единичный входкоторого соединен с третьим выходомблока управления, единичный выходтриггера - с первым входом второго Мэлемента И, второй вход которого соединен с выходом элемента задержки,при этом его выход соединен со вторым"входом второго элемента ИЛИ, выходомподсоединенного к третьему входу 35регистра-счетчика.На чертеже представлена структурная схема параллельно-последовательного аналого-цифрового преобразователя. 40Преобразователь содержит блок управления 1, регистр-счетчик 2, усили-,тель 3 с управляемым коэффициентомусиления, аналоговый вычитатель 4.входную шину 5, цифроаналоговый преобразователь б, преобразователь 7считывания, выходные шины 8, первыйи второй пороговые элементы 9 и 10,элемент 11 аналоговой секционнйй задержки, блок 12 аналоговых ключей,первый элемент 13 ИЛИ, формирователь 5014 импульсов, первый элемент 15 И,триггер 16, элемент задержки 17,второй элемент 18 И, второй элемент19 ИЛИ, шина 20 связи с микропроцессором. 554Преобразователь работает следующимобразом,Получение результирующего кодапроисходит последовательно по тактамотдельными Группами разрядов, которые формиру. тся с помощью преобразователя 7 считывания и записываются врегистр-счетчик 2. Выходной код этогсрегистра преобразуется с помощью преобразователя 6 в аналоговый сигнал,который вычитается из входного сигнала вычитателем 4. Полученный разностный сигнал усиливается усилителем 3 с коэффициентом, соответствующим выполняемому такту преобразования.В первом такте по сигналам блока 1 управления устанавливается минимальное значение коэффициента усиления усилителя 3 и гасится регистр 2. Входной сигнал без изменения проходит через вычитатель 4 на вход усилителя 3. Время установления выходного сигнала усилителя 3 определяется скоростью отклика усилителя, которая постоянна на данном такте и уменьшается при увеичении коэффициента усиления усилителя. Только после истечения времени установления выходного сигнала усилителя можно выполнять считывание кода из преобразователя 7. Считывание кода происходит по сигналу, сформированному формирователем 14 импульсов по перепадам выходных сигналов пороговых элементов 9 или 10. Эти элементы имеют одинаковые, но противоположные по знаку пороги срабатывания относительно выходного сигнала блока 12, представляющего собой сдвинутый во времени элементом 11 (на различную величину в зависимости от выполняемого такта) выходной сигнал. усилителя 3. Поэтому после установления сигнала на выходе усилителя один из пороговых элементов обязательно срабатывает. Для тех случаев, когда сигнал на выходе усилителя 3 не изменяется на величину, меньшую порога срабатывания элементов 9 и 10, в схеме предусмотрено считывание кода с выходов преобразователя 7 по другому сигналу, который формируется следующим образом. Каждый такт преобразования начинается с выдачи блоком 1 сигнала, который устанавливает триггер 16 в единичное состояние, Через некоторое время блоком 1 формируется сигнал, который подается на элементы 15 и 17. Если ни один из элементов 9 и 10 не сработал, то этот сигнал, задержанный элементом 17 на время срабатывания триггера, проходит через элементы 18 и 19 и по нему выполняется считывание, Если элементы 9 или 10 сработали, упомянутый сигнал проходит через элемент 15 и устанавливает триггер 16 в исходное состояние. Считывание произойдет в этом случае, как описано выше.После записи кода в регистр-счетчик 2 данный такт работы преобразователязаканчивается, Вновь записанная группа разрядов в регистре-счетчике 2 изменяет в преобразователе 6 выходной сигнал и начинается процесс преобразования следующего такта. Послевыполненйя последнего такта блок .1 на шину связи 20 выдает сигнал об ,окончании преобразования. Результи790287 ФормУла изобретения ВНИИПИ Заказ 9073/65 Тираж 995 Подписно Филиал ППДПатент , г, Ужгород, ул, Проектная,рующий код снимается с выходных шин 8.В преобразователе обеспечено увеличение быстродействия за счет сокращения времени выполнения каждого такта преобразования для всех уровней входных сигналов, кроме сигнала, имеющего максимальную величину,Параллельно-последовательный ана- о лого-цифровой преобразователь, содержащий аналоговый вычитатель, первый вход которого подключен к входной шине, второй вход - к выходу цироаналогового преобразователя, а выход к первому входу усилителя с управляемым коэффициентом усиления, вторые входы которого соединены с первыми выходами блока управления и с первыми входами регистра-счетчика, а выход подключен ко входу преобразователяЮ считывания, выходы которого соединены со вторыми входами регистра-счетчика, третий вход которого соединен со вхо- дом блока управления, выходы регистра- счетчика соединены с выходными шинами 25 и входами цифроаналогового преобразователя, о т л и ч а ю щ и й с я тем, что, с целью увеличения быстродействия преобразования аналоговой величины в код, в него введены элемент ана- О логовой секционной задержки, блок аналоговых ключей, элемент задержки, первый и второй пороговые элементы, формирователь импульсов, триггер, первый и второй элементы И и первый и второй элементы ИЛИ, причем первыевходы пороговых элементов соединеныс выходом усилителя с управляемымкоэффициентом усиления и со входомэлемента аналоговой секционной задержки, вторые их входы соединеныс выходом блока аналоговых ключей,соединенного первыми входами с первыми выходами блока управления и вторыми входами - с выходами элементааналоговой секционной задержки, выходы пороговых элементов подключеныко входам первого элемента ИЛИ, вы,ход которого подсоединен через формирователь импульсов к первому входувторого элемента ИЛИ и к первому входупервого элемента И, второй вход которого соединен со вторым выходом блока управления и входом элемента задержки, а выход - с нулевым входомтриггера, единичный вход которого сое"динен с третьим выходом блока управления, единичный выход триггера - с первым входом второго элемента И, второй вход которого соединен с выходом элемента задержки, при этом еговыход соединен со вторым входом второго элемента ИЛИ, выходом подсоединенного к третьему входу регистра-счетчика. Источники информации,принятые во внимание при экспертизе1, Петров Г.М. и др. Преобразование информации в аналого-цифрбвыхвычислительных устройствах и системах.М., Машиностроение, 1973, с.253,рис, 99.

СмотретьЗаявка

2650586, 01.08.1978

ПРЕДПРИЯТИЕ ПЯ Г-4128

ВОИТЕДЕВ АЛЕКСАНДР ИЛЬИЧ, ЛУКЬЯНОВ ЛЕВ МИХАЙЛОВИЧ

МПК / Метки

МПК: H03K 13/03

Метки: аналогоцифровой, параллельно-последовательный

Опубликовано: 23.12.1980

Код ссылки

<a href="https://patents.su/3-790287-parallelno-posledovatelnyjj-analogocifrovojj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Параллельно-последовательный аналогоцифровой преобразователь</a>

Предыдущий патент: Аналого-цифровой преобразователь

Следующий патент: Декадирующий накопитель

Случайный патент: Буферная жидкость для разделения бурового и тампонажного цементного растворов