Приемник дискретной информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 786040

Авторы: Бродская, Спиваковский, Чурус

Текст

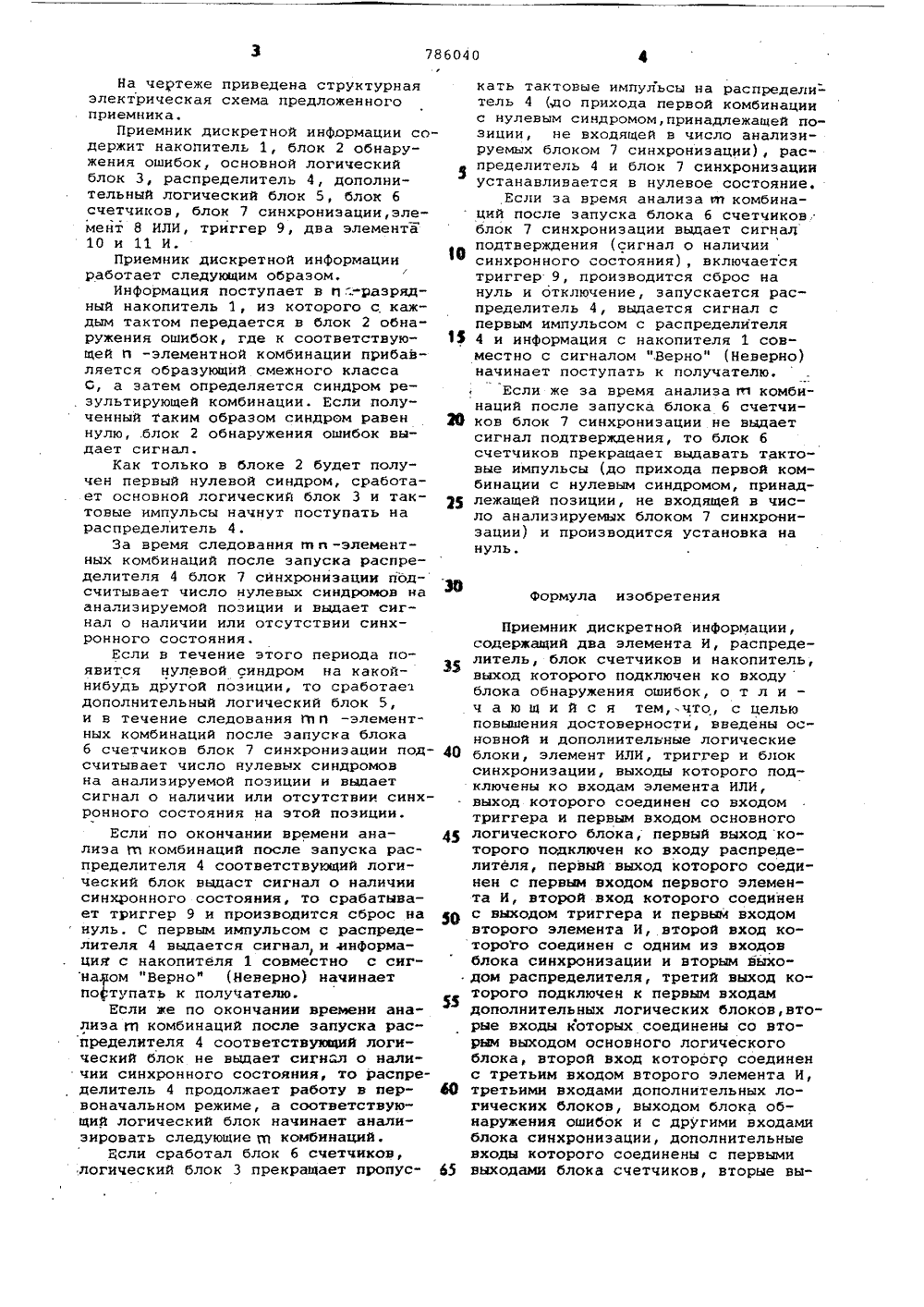

ЪСЕСОФЗИАЯв гф ОП ИЗРАНИВ ИЗОБРЕТЕНИЯ о 78 о 040. Союз Соввтскик Социалистических Рвспублик(22) Заявлено 0111,78 (21) 2680948/18-09с присоединением заявки йо(51) М. Кл. Н 04 . 17/16 Государственный комитет СССР по делам изобретений и открытий(54) ПРИЕМНИК ДИСКРЕТНОЙ ИНФОРМАЦИИ Изобретение относится к технике связи и может быть использовано для циклового фазирования аппаратуры передачи дискретной информации.Известен приемник дискретной информации, содержащий два элемента И, распределитель, блок счетчиков и накопитель, выход которого подключен ко входу блока обнаружения ошибок 11,Однако достоверность работы такого приемника недостаточнаЦель изобретения - повышение достоверности работы. Для этого в приемник дискретной информации, содержащий два элемента И, распределитель, блок счетчиков и накопитель, выход которого подключен ко входу блока обнаружения ошибок, введены основной и дополнитель, ные логические блоки, элемент ИЛИ, триггер и блок синхронизации, выходы которого подключены ко входам элемента ИЛИ, выход которого соединен сс входом триггера и первым входом основного логического блока, первый выход. которого подключен ко входу распределителя. Первый выход распре.делителя соединен е первым входом,2первого элемента И, второй вход которого соединен с выходом триггера и первым входом второго элемента И, второй вход которого соединен с од ним из входов блока синхронизациии вторым выходом распределителя,Третий выход распределителя подключен к первым входам дополнительных логических блоков, вторые входы которых 1 О соединены со вторым выходом основного логического блока, второй вход которого соединен с третьим входом второго элемента И, третьими входами дополнительных логических блоков, 15 выходом блока обнаружения ошибок ис другими входами блока синхронизации, дополнительные входы которого соединены с первыми выходами блока счетчиков, вторые выходы которых 20 подключены к соответствующим входамосновного и дополнительныХ логических блоков, тактовые входы которых соединены со входом накопителя. Входы блока счетчиков соединены с пер выми выходами дополнительных логических блокова вторые выходы соответствующих дополнительных логических блоков подключены к четвертым входам соответствующих дополнитель ных логических блоков./На чертеже приведена структурнаяэлектрическая схема предложенногоприемника.Приемник дискретной информации содержит накопитель 1, блок 2 обнаружения ошибок, основной логическийблок 3, распределитель 4, дополнительный логический блок 5, блок бсчетчиков, блок 7 синхронизации,элемент 8 ИЛИ, триггер 9, два элемента10 и 11 И.Приемник дискретной информацииработает следующим образом,Информация поступает в О =-разрядный накопитель 1, из которого с.каждым тактом передается в блок 2 обнаружения ошибок, где к соответствующей П -элементной комбинации прибавляется образующий смежного классаС, а затем определяется синдром ре. зультирующей комбинации. Если полученный таким образом синдром равеннулю, блок 2 обнаружения ошибок выдает сигнал.Как только в блоке 2 будет получен первый нулевой синдром, сработает основной логический блок 3 и тактовые импульсы начнут поступать нараспределитель 4.За время следования т д -элементных комбинаций после запуска распределителя 4 блок 7 синхронизации подсчитывает число нулевых синдромов наанализируемой позиции и выдает сигнал о наличии или отсутствии синхронного состояния.Если в течение этого периода появится нулевой синдром на какойнибудь другой позиции, то сработаедополнительный логический блок 5,и в течение следования Ф й -элементных комбинаций после запуска блокаб счетчиков блок 7 синхронизации подсчитывает число нулевых синдромовна анализируемой позиции и выдаетсигнал о наличии или отсутствии синхронного состояния на этой позиции.Если по окончании времени анализа т комбинаций после запуска распределителя 4 соответствующий логический блок выдаст сигнал о наличиисинхронного состояния, то срабатывает триггер 9 и производится сброс нануль. С первым импульсом с распределителя 4 вццается сигнал,и информация с накопителя 1 совместно с сигналом "Верно" (Неверно) начинаетпоступать к получателю.Если же по окончании времени анализа щ комбинаций после запуска распределителя 4 соответствующий логический блок не выдает сигнал о наличии синхронного состояния, то распределитель 4 продолжает работу в первоначальном режиме, а соответствующий логический блок начинает анализировать следующие щ комбинаций.Если сработал блок б счетчиков,логический блок 3 прекращает пропус"кать тактовые импульсы на распределитель 4 (до прихода первой комбинациис нулевым синдромом, принадлежащей позиции, не входящей в число анализируемых блоком 7 синхронизации), рас"пределитель 4 и блок 7 синхронизацииустанавливается в нулевое состояние.Если за время анализа пп комбинаций после запуска блока б счетчиковблок 7 синхронизации выдает сигнаЛподтверждения (сигнал о наличиисинхронного состояния), включаетсятриггер 9, производится сброс нануль и отключение, запускается распределитель 4, выдается сигнал спервым импульсом с распределителя 33 4 и информация с накопителя 1 совместно с сигналом "Верно" (Неверно)начинает поступать к получателю. наций после запуска блока б счетчи 36 ков блок 7 синхронизации не выдает 33 45 59 53 ед 65 Если же за время анализа ю комбисигнал подтверждения, то блок бсчетчиков прекращает выдавать тактовые импульсы (до прихода первой комбинации с нулевым синдромом, принадлежащей позиции, не входящей в число анализируемых блоком 7 синхронизации) и производится установка нануль. Формула изобретения Приемник дискретной информации, содержащий два элемента И, распределитель, блок счетчиков и накопитель, выход которого подключен ко входублока обнаружения ошибок, о т л и ч а ю щ и й с я тем, что, с целью повышения достоверности, введены основной и дополнительные логические блоки, элемент ИЛИ, триггер и блок синхронизации, выходы которого подключены ко входам элемента ИЛИ, выход которого соединен со входом триггера и первым входом основного логического блока, первый выход ко" торого подключен ко входу распределителя, первый выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом триггера и первым входом второго элемента И, второй вход которого соединен с одним из входов блока синхронизации и вторым выходом распределителя, третий выход которого подключен к первым входам дополнительных логических блоков,вторые входы которых соединены со вторым выходом основного логического блока, второй вход которого соединен с третьим входом второго элемента И, третьими входами дополнительных логических блоков, выходом блока обнаружения ошибок и с другими входами блока синхронизации, дополнительные входы которого соединены с первыми выходами блока счетчиков, вторые вы786040 Составитель А. ЕрофеевУтехина ТехредМ.Табаковнч Корректор С. Щомак акт Подписноеа СССРтийнаб., д. 4/5 каэ 8866/61 Тираж 729 ВНИИПИ Государственного ком по делам изобретений и о 113035, Москва, Ж, Раушскт Кр а Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 ходы которых подключены к соответствующим входам основного и дополнительньщ логических блоков, тактовыевходы которых соединены со входомнакопителя, причем. входы блока счетчиков соединены с первыми выходами,Дополнительных логических блоков,а вторые выходы соответствующих дополнительных логических блоков подключены к четвертым входам соответствующих дополнительных логических блоков,.Источники информации,принятые во внимание при зкспертиэе 1. Авторское свидетельство СССР М 464979, кл. Н 041/10, 1973 (прототип),

СмотретьЗаявка

2680948, 01.11.1978

ПРЕДПРИЯТИЕ ПЯ А-1221

БРОДСКАЯ ЕЛЕНА БОРИСОВНА, ЧУРУС АНАТОЛИЙ ПЕТРОВИЧ, СПИВАКОВСКИЙ ЕФИМ ЛАЗАРЕВИЧ

МПК / Метки

МПК: H04L 17/16

Метки: дискретной, информации, приемник

Опубликовано: 07.12.1980

Код ссылки

<a href="https://patents.su/3-786040-priemnik-diskretnojj-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Приемник дискретной информации</a>

Предыдущий патент: Способ передачи дискретной информации

Следующий патент: Устройство для приема сигналов двойной частотной телеграфии

Случайный патент: Кожух для шлифовальных кругов