Процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

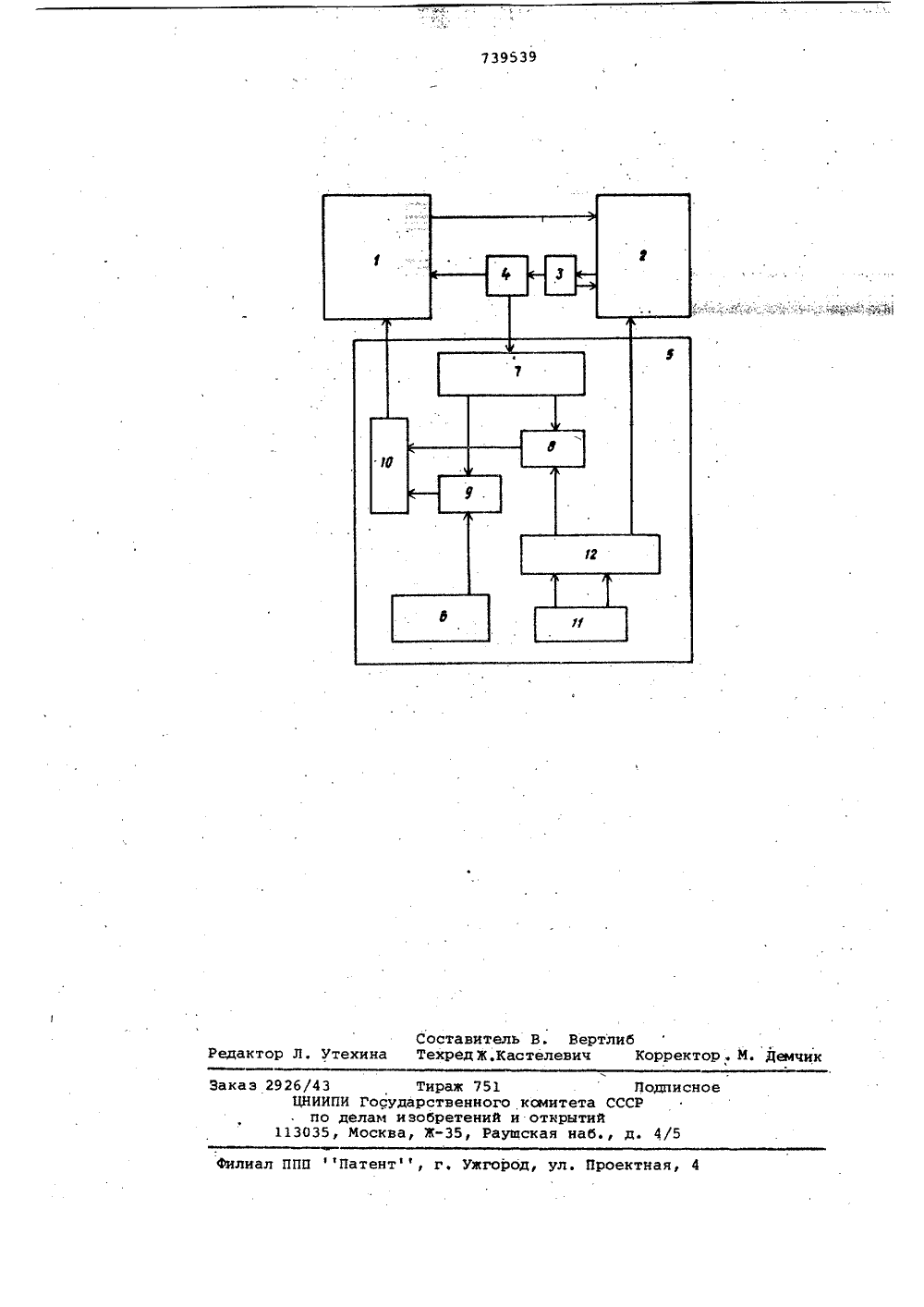

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИ ЕТИЛЬСТВУ Сова Советских Социалистических Республик(51)М. Кл. С 06 Г 15/00 с присоединением заявки МоГосударственный комитет СССР по делам изобретений и открытий(088, 8) Дате опубликования описания 0506.80(72 Авторы изобретения В Л. Гуляев, В Л. Иванов, А.В; Палагин и П.М, Сиваченко. Институт электродинамики АН украинской ССР(5 4) ПР ЩЕССОР Изобретение относится к области,вычислительной техники и может бытьиспользовано в вычислительных системах различного назначенйя.Известны процессоры (11, содержащие устройство управления, генератор синхросигналов, операционноеустройство со средствами контроля иблок синхронизации. Принцип работы устройства состоит в том, чтопо сигналу детектора ошибки запускаются средства, обеспечивающие выработку специальных синхросигналовс периодом повторения, превьыающим перибд повторения рабочих синхроСигналов на время переходного процесса.Недостатком устройства являетсябовьшое время контроля из-за низких диагностических свойств, обусловленных тем, что устройство управления и операционное устройство работают на одинаковой частоте следования синхросигналов и устройствоуправления не успевает анализироватьрезультаты преобразований в операционном устройстве,Наиболее близким по технической сущности к изобретению является про цессор 21, содержащий блок микропрограммного управления, соединенный двусторонней связью с регистроммикрбкоманд, выход которого подклю- .чен ко входу дешифратора микрокоманд,операционный блок, вход и выход которого.подключены соответственно квыходу дешифратора.микрокоманд иадресному входу блока микропрограммного управления, и блок синхронизации,включающий узел формирования основныхи рабочих .тактовых импульсов, соединЕнный группой выходов с группойвходов узла распределения тактовыхимпульсов, первая группа выходов которого подключена к группе входовсинхронизации блока микропрограммного управления.Однако надежность этого устройства недостаточна из-за значительного,времени, необходимого для проведения тактового контроля в случаях по-явления неисправностей как в самомпроцессоре, так и в вычислительнойсистеме в целом,Целью изобретения является повышение надежности работы.Поставленная цель достигаетсятем что в предложенном процессорев блок синхронизации введены узел формированияеконтрольных тактовых импульсов, триггер управления, две группы элементов И и группа элементов ИЛИ; выходы которых соединены с группой входов синхронизации операционного блока. Входы триггера управления соединены с соответствующими- дбполнительными выходами дешифрато- . ра микрокоманд. Выходы второй группы выходов узла распределения тактовых импульсов подключены ко входам соответствующих элементов И первой группы; управляющие входы которых соединены с первым выходом триггера управления, а выходы - с первыми входами элементов ИЛИ группы. Вьио ды узла формирования контрольных тактовых импульсов подключены ко входам соответствующих элементов И второй группы, управляющие входы которых подключены ко второму выходу тригге .ра уйравления, а выходы - ко вторым входам соответствующих элементов ИЛИ группы.На чертеже дана структурная схема процессора.25Он содержит операционный блок 1, блок 2 микропрограммного управления, регистр 3 микрокоманд, дешифратор 4 микрокоманд, блок 5 синхронизации, включающий узел 6 формирования контрольных тактовых импуль- ЗО сов:, триггер 7 управления, первую 8 и вторую 9 группы элементов И, группу 10 элементов ИЛИ, узел 11 формирования основных и рабочих тактовых импульсов и узел 12 распределения так товых импульсовУстройство работает следующим образом.При нормальной работе процессора рабочие тактовые импульсы, вырабатываемые узлом 11, поступают с выходов узла 12 на входы синхронизации блока 2 и блока 1, буричем на входы последнего эти тактовые импульсы поступают через элементы И первой группы 8, открытые управляющим сигналомс .ффнулевого выхода триггера 7, который установлен н единичное состояние сигналом с выхода дешифратора 4.При обнаружении ошибки в работе процессора осуществляется переход 50 на программу, поиска неисправности. Одно из микрокоманд этой программы вызывает переключение триггера 7 вединичноеф состояние, что вызывает снятие разрешающего сигйала с эле ;ментов И группы 8 и подачу его с единичного выхода триггера 7 на управляющие входы элементов И группы 9, В результате на входы синхронизации блока 1 черезгруппу 9 элементов И начинают:поступать тактовые импульсы, форщруемые узлом б.Если частота тактовых импульсов, поступающих иэ узла б, ниже частоты тактовых импульсов, генерируемым узлом 12, то в режиме поиска неисправностей блок 2 может работать с более высокой частотой, чем блок 1, Это обеспечивает возможность анализа результата выполнения микрооперации до начала выполнения другой, и, следовательио, облЕгчает процесс поиска неисправностей и исключает необходимость перезапуска процессора для повторения ситуаций.Таким образом, предложенный процес" сор позволяет упростить процедуры поиска неисправностей, сократить мх количество, повысить разрешающую способность диагностирования и снизить за счет этого время контроля. формула изобретенияПроцессор, содержащий блокмикропрограммного управления, соединенный двусторонней связью с регистром микрокоманд, выход которогоподключен ко входу дешифратора микрокоманд, операционный блок, вход ивыход которого подключены.соответственно к выходу дешифратора микрокоманд и адресному входу блока микропрограммного управления, и блок синхронизации, включающий узел формирования оснонных и рабочих тактовыхимпульсов, соединенный группой вы-.ходов с группой входов узла распределения тактоных импульсов, перваягруппа выходов которого подключенак группе входов синхронизации блока микропрограммного управления,о т л и ч а ю щ и й с я тем, что,с целью повышения надежности, вблок синхронизации введены узелФормирования контрольных тактовыхимпульсов, триггер управления, двегруппы элементов И и группа элементов ИЛИ, выходы которых соединены сгруппой входов синхронизации операционного блока, а входы триггерауправления соединены с соответствующими дополнительными выходами дешифратора микрокьманд, причем выходы иэвторой"группы выходов узла распределения тактовых импульсон подключены ко нходам соответствующих элементов И первой группы, управляющиевходы которых соединены с первымвыходом триггера управления, а выходы - с первыми нходами элементов .ИЛИ группы, выходы узла формирования контрольных тактовых импульсовподключены ко входам соответствующихэлементов И второй группы, управляющие входы которых йодкАючены ковторому выходу триггера управления,а выходы - ко вторым входам соответствующих элементов ИЛИ группы.Источники информации,принятые во внимание при экспертизе1, Патент США Р 3868647,Н, кл. 340-172.5, 1970.2. Процессор ЭВМ ЕС, М.,739539 Составитель В. ВертлибРедактор Л. Утехина ТехредЖ,Кастелевич КорректоРЗаказ ПП фПатент, г, Ужгород, Ул. Проектна л 926/43 Тираж 751 ЦНИИПИ Государственног по делам изобретений 113035, Москва, Ж, Ра

СмотретьЗаявка

2462586, 15.03.1977

ИНСТИТУТ ЭЛЕКТРОДИНАМИКИ

ГУЛЯЕВ ВАСИЛИЙ АНАТОЛЬЕВИЧ, ИВАНОВ ВЛАДИМИР АНДРЕЕВИЧ, ПАЛАГИН АЛЕКСАНДР ВАСИЛЬЕВИЧ, СИВАЧЕНКО ПЕТР МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 11/22, G06F 15/00

Метки: процессор

Опубликовано: 05.06.1980

Код ссылки

<a href="https://patents.su/3-739539-processor.html" target="_blank" rel="follow" title="База патентов СССР">Процессор</a>

Предыдущий патент: Устройство для контроля принимаемой информации

Следующий патент: Устройство для предварительной обработки информации

Случайный патент: Дозатор сыпучих и кусковых материалов