Устройство для приема информации в системах передачи данных с решающей обратной связью

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

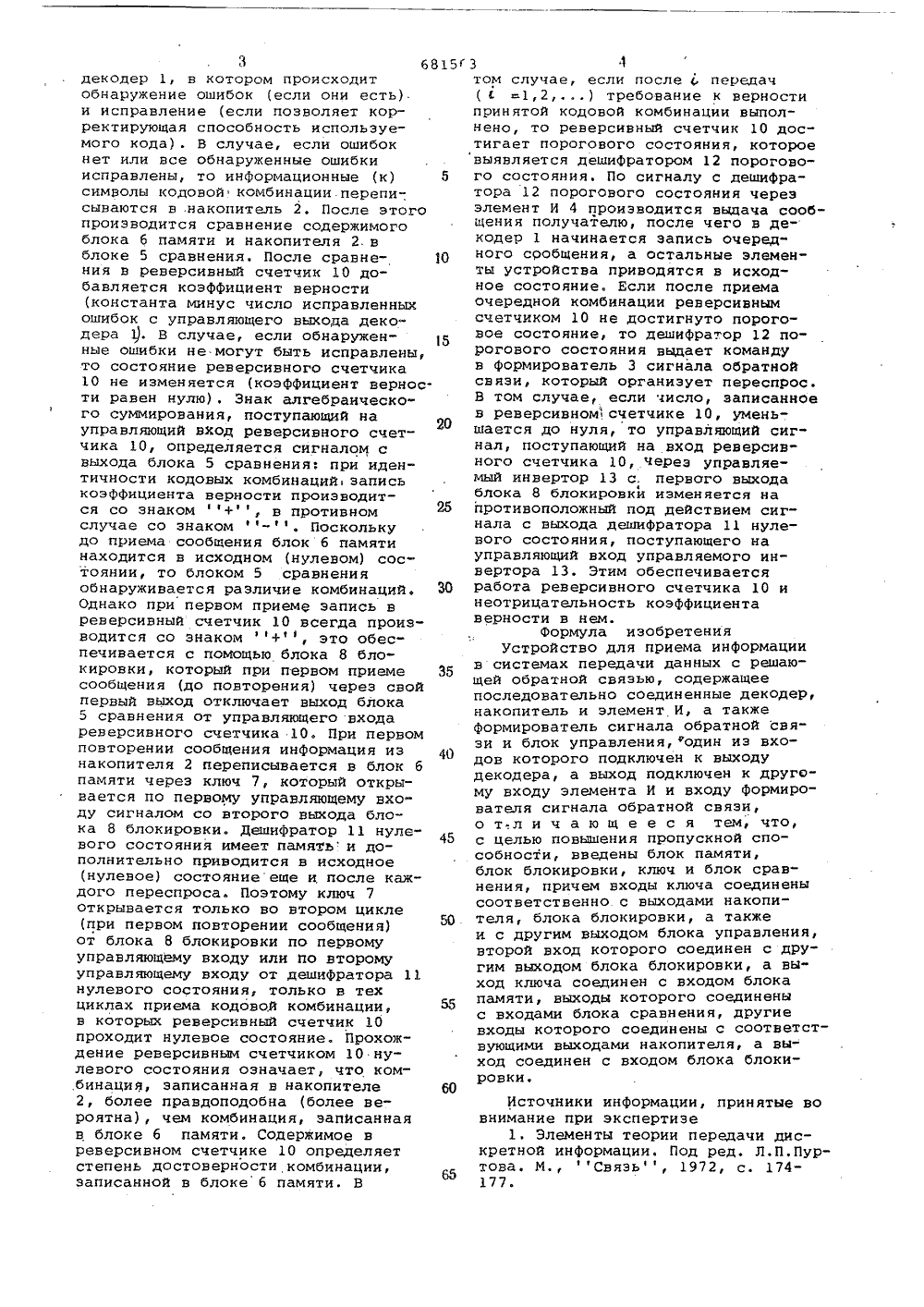

(11681563 Союз СоветскихСоциалистическихРеспублик ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(22) Заявлено 130378(21) 2590516/18-09с присоединением заявки Йо(23) Приоритет Н 04 В 1/060 Н 04 Ь 1/12 Государственный кои итет СССР по делаи нзобретеннй н открытяй(72) Авторы изОбретения А. М. Плотников и А. В. Бормисов Ленинградский ордена Ленина электротехнический институт им. В. И. Ульянова (Ленина)(54) УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ В СИСТЕМАХ ПЕРЕДАЧИ ДАННЬК С РЕШЖОЩЕЙ ОБРАТНОЙ СВЯЗЫО. Изобретение относится к радиотехнике.Известно устройство для приема информации в системах передачи данных с решающей обратной связью, содержащее последовательно соединенные декодер, .накопитель и элемент И, а также формирователь сигнала обратной связи и блок управления, один из входов которого подключен к выходу декодера, а выход подключен к другому входу элемента И и входу формирователя сигнала обратной связи 1).Однако в этом устройстве недостаточная пропускная способностьЦель .изобретения - повышение пропускной способности.Для этого в устройство для приема информации в системах передачи данных с решающей обратной связью, содержащее последовательно соединенные декодер, накопитель и элемент И, а также формирователь сигнала обратной связи и блок управления, один из входов которого подключен к выходу декодера, а выход подключен к другому входу элемента И и входу формирователя сигнала обратной связи, введен блок памяти, блок блокировки,ключ и блок сравнения, причем входыключа соединены соответственно с выходами накопителя, блока блокировки,а также и с другим выходом блокауправления, второй вход которогосоединен с другим выходом блокаблокировки, а выход ключа соединенс входом блока памяти, выходы которого соединены с входами блока сравнения, другие входы которого соединены с соответствующими выходами накопителя, а выход соединен с входомблока блокировки,На чертеже изображена структур 5 ная электрическая схема предлагаемого устройства.Устройство содержит декодер 1,накопитель 2, формирователь 3сигнала обратной связи, элемент20 И 4, блок 5 сравнения, блок 6 памяти, ключ 7, блок 8 блокировки,блок 9 управления, состоящий изреверсивного счетчика 10, дешифратора 11 нулевого состояния, де 25 шифратора 12 порогового состояния,инвертора 13.Устройство работает следующимобразом.Двоичные п-элементные символы30 кодовой комбинации поступают в6815 3 4 20 8декодер 1, в котором происходит обнаружение ошибок (если они есть). и исправление (если позволяет корректирующая способность используемого кода). В случае, если ошибок нет или все обнаруженные ошибки исРанлены, то информационные (к) 5 символы кодовой комбинации переписываются в,накопитель 2. После этого производится сравнение содержимого блока б памяти и накопителя 2, в блоке 5 сравнения. После сравне- Ю ния в реверсивный счетчик 10 добавляется коэффициент верности (константа минус число исправленных ошибок с управляющего выхода деко" дера 1). В случае, если обнаруженные ошибки не могут быть исправлены, то состояние реверсивного счетчика 10 не изменяется (коэффициент вернос. ти равен нулю). Знак алгебраического суммирования, поступающий на управляющий вход реверсивного счетчика 10, определяется сигналом с выхода блока 5 сравнения: при идентичности кодовых комбинаций запись коэффициента верности производится со знаком +, в противном случае со знаком ". Поскольку до приема сообщения блок б памяти находится в исходном (нулевом) состоянии, то блоком 5 сравнения обнаруживается различие комбинаций. 30 Однако при первом приеме запись в ренерсинный счетчик 10 всегда производится со знаком +", это обес" печивается с помощью блока 8 блокировки, который при первом приеме 35 сообщения (до повторения) через свой первый выход отключает выход блока 5 сравнения от управляющего входа реверсивного счетчика 10. При первом повторении сообщения инФормация из 40 накопителя 2 переписывается в блок б памяти через ключ 7, который открывается по первому упранляющему входу сигналом со второго выхода блока 8 блокировки. ДешиФРатор 11 нУле" ного состояния имеет память и дополнительно приводится в исходное (нулевое) состояние еще и, после каждого переспроса. Поэтому ключ 7 открывается только во нтором цикле (при первом повторении сообщения) от блока 8 блокировки по первому управляющему входу или по второму управляющему входу от дешифратора 11 нулевого состояния, только в тех циклах приема кодовой комбинации, 55 в которых ренерсивный счетчик 10 проходит нулевое состояние. Прохождение реверсивным счетчиком 10 нулевого состояния означает, что ком.бинация, записанная н накопителе 60 2, более правдоподобна (более вероятна), чем комбинация, эапйсанная в блоке б памяти. Содержимое в реверсивном счетчике 10 определяет степень достоверности комбинации, б 5 записанной в блоке 6 памяти. В том случае, если после , передач( с 1,2, ,) требование к верностипринятой кодовой комбинации выполнено, то реверсивный счетчик 10 достигает порогового состояния, котороевыявляется дешифратором 12 порогового состояния. По сигналу с дешифратора 12 порогового состояния черезэлемент И 4 производится выдача сообщения получателю, после чего в декодер 1 начинается запись очеред"ного сообщения, а остальные элементы устройства приводятся в исходное состояние, Если после приемаочередной комбинации реверсивнымсчетчиком 10 не достигнуто пороговое состояние, то дешифратор 12 порогового состояния выдает командув формирователь 3 сигнала обратнойсвязи, который организует переспрос.В том случае, если число, записанноев реверсивном. счетчике 10, уменьшается до нуля, то управляющий сиг"нал, поступающий на вход реверсивного счетчика 10, через управляе"мый инвертор 13 с, первого выходабЛока 8 блокировки изменяется напротивоположный под действием сигнала с выхода дешифратора 11 нулевого состояния, поступающего науправляющий вход управляемого инвертора 13, Этим обеспечиваетсяработа реверсивного счетчика 10 инеотрицательность коэффициентаверности в нем.Формула изобретенияУстройство для приема информациин системах передачи данных с решающей обратной связью, содержащеепоследовательно соединенные декодер,накопитель и элемент И, а такжеФормирователь сигнала обратной связи и блок управления, один из входов которого подключен к выходудекодера, а выход подключен к другому входу элемента И и входу формирователя сигнала обратной связи,о тл и ч а ю щ е е с я тем, что,с целью повышения пропускной способности, введены блок памяти,блок блокировки, ключ и блок сравнения, причем входы ключа соединенысоответственно с выходами накопии с другим выходом блока управления, второй вход которого соединен с другим выходом блока блокировки, а выход ключа соединен с входом блока памяти, выходы которого соединены с входами блока сравнения, другие входы которого соединены с соответствующими выходами накопителя, а выход соединен с входом блока блокировки. Источники информации, принятые во внимание при экспертизе1. Элементы теории передачи дискретной информации. Под ред. Л,П,ПУР- тона. М фСвязь, 1972, с. 174- 177.Составитель Г. СероваРедактор Н. Хлудова ТехредЛ,Ьл ерова Корректор С, ПатрушеваЗаказ 5106/52 Тираж 775 ПодписноеЦНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035 Иосква ЖРа ская наб. д. 4 5Филиал 11 ПП Патент, г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

2590516, 13.03.1978

ЛЕНИНГРАДСКИЙ ОРДЕНА ЛЕНИНА ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. УЛЬЯНОВА

ПЛОТНИКОВ АНАТОЛИЙ МИХАЙЛОВИЧ, БОРМИСОВ АНАТОЛИЙ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: H04B 1/06

Метки: данных, информации, обратной, передачи, приема, решающей, связью, системах

Опубликовано: 25.08.1979

Код ссылки

<a href="https://patents.su/3-681563-ustrojjstvo-dlya-priema-informacii-v-sistemakh-peredachi-dannykh-s-reshayushhejj-obratnojj-svyazyu.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для приема информации в системах передачи данных с решающей обратной связью</a>

Предыдущий патент: Делитель частоты импульсов

Следующий патент: Система дистанционного питания необслуживаемых усилительных пунктов

Случайный патент: Устройство для облучения жидкости ультрафиолетовыми лучами