Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 679980

Авторы: Андрущенко, Барбаш, Тимонькин, Ткаченко, Фомин

Текст

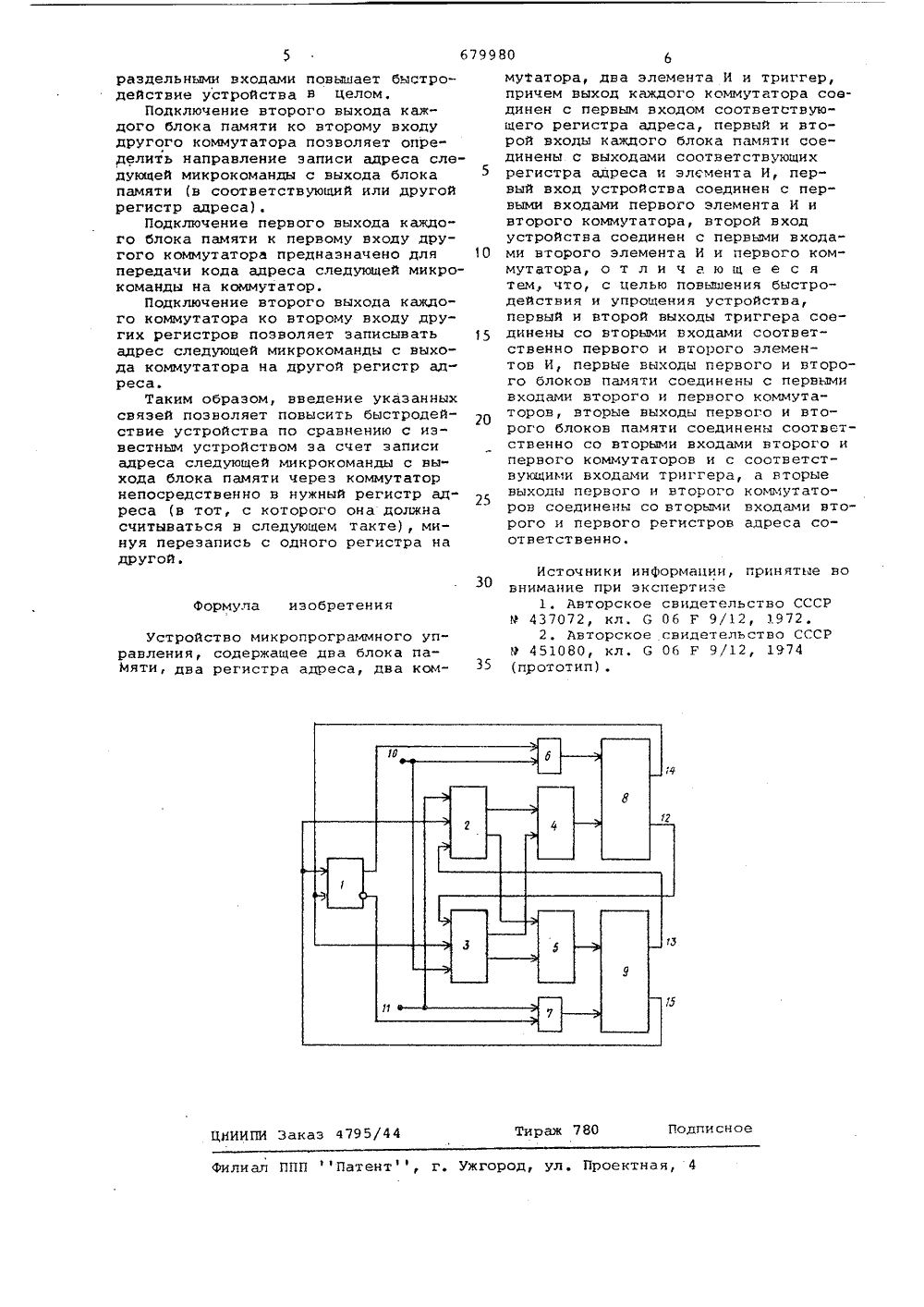

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИ ЕПЛЬСТВУ(51)М. Кл. С 06 Г 9/12 ГосуаарствеинмА комитет СССР по аел ам изобретеииА н открытнА(54) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ Изобретение относится к области вычислительной техники, в частности к устройствам микропрограммного управления, и может быть использовано в системах обработки данных.Известно устройство микропрограммного управления, содержащее запоминающие блоки, два блока проверки условий, два элемента И, регистры адре О са и триггеры блокировки 1),Недостатками устройства являются незначительное быстродействие и повышенные затраты оборудования, 15Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство микропрограммного управления, содержащее два блока памяти, два регистра адреса, два коммутатора, два элемента И и триггер, причем выход каждого ком" мутатора соединен с первым входом .соответствующего регистра адреса, первый и второй входы каждого блока памяти соединены с выходами соотввтствующих регистра адреса и элемента И, каждый вход устройства соединен с первыми входами одного элемента И и другого коммутатора 2,Недостатки такого устройства - сложность и низкое быстродействиеСложность устройства обусловлена использованием в нем двух триггеров со счетным входом. Низкое быстродействие устройства также связано с использованием триггеров со счетным входом, а также с тем, что при необходимости реализации перехода от нечетной (четной) микрокоманды к нечетной (четной) адрес следующей микрокоманды считывается иэ одного бло" ка памяти, записывается в другой регистр адреса и затем через другой коммутатор записывается в регистр адреса, соответствующий тому блоку памяти, с которого была считана данная микрокоманда. При этом полупвриод следования тактовых импульсов по каждому входу устройства не может превышать величины Т 1,определяемой следующим выражением: С -с С Ф С с = С 2 с Чк п сц р кгде Гсц - время считывания в блокепамяти 1п - время записи адреса микрокоманды в регистр адреса 1Структурная схема устройства приведена на чертеже,Устройство микропрограммного управления содержит триггер 1, коммутаторы 2, 3, регистры адреса 4, 5,элементы И б, 7, блоки памяти 8, 9,входы 10, 11. Позициями 12, 13 и14, 15 обозначены соответственно первые и вторые выходы блоков памяти,Устройство работает следующим образом.Триггер 1 осуществляет управлениеработой устройства. Если он находится н единичном (нулевом) состоянии,то открыт элемент И б(7) и разрешается считывание тактовым импульсом,поступающим на вход 10(11), информации с блока памяти 8(9). Предположим, что в исходном состоянии триггер 1 находится в единичном (нулевом) состоянии, а на регистре 4(5) находится адрес микрокоманды, подлвжащей считыванию. Поскольку элемент И (7)6 открыт, то первый тактовый импульс, поступающий с входа устройства 10(11) на первый вход .элемента И б(7), считывает с блока памяти 8(9) микрокоманду. Далее устройство может функционировать в двух режимах, Первый режим соответствует чередованию четных (нечетных) и нечетных (четных) микрокоманд, во втором режиме реали 40 Г - время срабатывания коммутатора.Частота поступления тактовых импульсов Хт на каждый иэ входов устройства не может превышать величины тт,определяемой следующим выражением:сцт 1 2 Т 2(Г ф 2 т +С 1Таким образом, необходимость записи кода адреса следующей микроко" манды сначала в один регистр адреса, а потом перезаписи его через коммутатор в другой регистр адреса и, кроме того, применение триггерон со счетным вхддом, Обладающих более низким быстродействием, чем триггер с раздельным входом, существенно снижает быстродействие такого устройства,Цель изобретения - повышение быстродействия и упрощение устройства,Постанленная цель достигается тем, 20что первый и второй выходы триггера соединены с вторыми входами соответственно первого и второго элементов И, первые ныходы первого и второго блоков памяти соединены с первыми входами второго и первого коммутаторов, вторые выходы первого и второго блоков памяти соединены соотнетстненно с вторыми входами второго и первого коммутаторов и с соответствующи" ми входами триггера, а вторые выходы первого и второго коммутаторов соединены с вторыми нходами первого и второго регистров адреса, 45 50 зуются переходы от нечетных (четных)к нечетньщ (четным) микрокомандам.При работе устройства в первомрежиме со второго выхода 14(15) блока памяти 8(9) считывается каждый раэединичный сигнал, который поступаетна нулевой (единичный) вход триггера 1 и переводит его в нулевое (еди"ничное) состояние, в котором открытэлемент И 7(6) . Одновременно с первого выхода 12(13) блока памяти 8(9)адрес следующей микрокоманды поступает на перный вход коммутатора 3(2),на второй вход которого поступаетсигнал с выхода 14(15) блока памяти 8(9), наличие которого предопределяет запись адреса микрокомандыс первого выхода коммутатора 3(2) через первый вход на регистр адреса5(4), В дальнейшем работа устройстваповторяется аналогично описанному.Во втором режиме устройство функционирует следующим образом. На втоРом выходе 14(15) блока памяти 8(9)сигнал отсутствует. Поэтому триггер 1останется н единичном (нулевом) сос"тоянии, при котором открыт элемент И6(7), Одновременно с первого выхода 12(13) блока памяти 8(9) адрес следующей микрокоманды поступает напервый нход коммутатора 3(4). Отсутствие сигнала на втором входе коммутатора 3(4) предопределяет записьадреса микрокоманды со второго выхода коммутатора 3(2) через второй входна регистр адреса 4(5). С приходомтактового импульса на вход 11 считывается микрокоманда с блока памяти8(9) . Если после этой считываемой микрокоманды необходимо вновь реализовать второй режим, то процесс понторяется аналогично описанному,Полупериод следования тактовыхимпульсов Г по каждому входу устройства не превышает неличины 2; определяемой следующим выражением:2 =С +С +Г2 счЧастота поступления тактовых импульсов Й. на каждый из входов устройства не может превышать величины Е 2,определяемой следующим выражени" 14Т 2 2 Г Йсц+ (Юк)Использование нового элемента -триггера с раздельными входами познОляет упРОстить устройствО по сравнению с известным устройством.Подключение единичного входа триггера к выходу одного блока памяти,нулевого - к выходу другого блока памяти, нулевого выхода ко входу одного элемента И, а единичного - ковходу другого элемента И позволяетиспользовать триггер для управленияработой устройства. Поскольку триггер с раздельными входами обладаетболее нысоким быстродействием, чемтриггер со счетным входом, то введение в схему одного триггера с679980 Формула изобретения Тираж 780Подписное ЦНИИПИ Заказ 4795/44 Филиал ППППатент , г. Ужгород, ул, Проектная, 4 раздельными входами повышает быстродействие устройства в целом,Подключение второго выхода каждого блока памяти ко второму входу другого коммутатора позволяет определить направление записи адреса следующей микрокоманды с выхода блока памяти (в соответствующий или другой регистр адреса).Подключение первого выхода каждого блока памяти к первому входу другого коммутатора предназначено для 10 передачи кода адреса следующей микро- команды на коммутатор.Подключение второго выхода каждого коммутатора ко второму входу других регистров позволяет записывать 15 адрес следующей микрокоманды с выхода коммутатора на другой регистр адреса.Таким образом, введение указанных связей позволяет повысить быстродействие устройства по сравнению с известным устройством за счет записи адреса следующей микрокоманды с выхода блока памяти через коммутатор непосредственно в нужный регистр адреса (в тот, с которого она должна считываться в следующем такте), минуя перезапись с одного регистра на другой. Устройство микропрограммного управления, содержащее два блока памяти два регистра адреса, два коммутатора, два элемента И и триггер,причем выход каждого коммутатора соединен с первым входом соответствующего регистра адреса, первый и второй входы каждого блока памяти соединены с выходами соответствующихрегистра адреса и элемента И, первый вход устройства соединен с первыми входами первого элемента И ивторого коммутатора, второй входустройства соединен с первыми входами второго элемента И и первого коммутатора, о т л и ч а ю щ е е с ятем, что, с целью повышения быстродействия и упрощения устройства,первый и второй выходы триггера соединены со вторыми входами соответственно первого и второго элементов И, первые выходы первого и второго блоков памяти соединены с первымивходами второго и первого коммутаторов, вторые выходы первого и второго блоков памяти соединены соответственно со вторыми входами второго ипервого коммутаторов и с соответствующими входами триггера, а вторыевыходы первого и второго коммутаторов соединены со вторыми входами второго и первого регистров адреса соответственно. Источники информации, принятые вовнимание при экспертизе1. Авторское свидетельство СССРР 437072, кл. С 06 Р 9/12, 1972.2, Авторское свидетельство СССРР 451080, кл. С 06 Р 9/12, 1974

СмотретьЗаявка

2479592, 26.04.1977

ПРЕДПРИЯТИЕ ПЯ М-5156

АНДРУЩЕНКО АНАТОЛИЙ ГРИГОРЬЕВИЧ, БАРБАШ ИВАН ПАНКРАТОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ФОМИН НИКОЛАЙ ФЕДОРОВИЧ

МПК / Метки

МПК: G06F 9/12

Метки: микропрограммного

Опубликовано: 15.08.1979

Код ссылки

<a href="https://patents.su/3-679980-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Устройство для деления частоты следования импульсов на неправильную дробь

Следующий патент: Устройство переменного приоритета

Случайный патент: Устройство для ограничения поворота статора преобразователя круговых перемещений