Вычислительная система

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 615483

Авторы: Антимиров, Коробейщикова

Текст

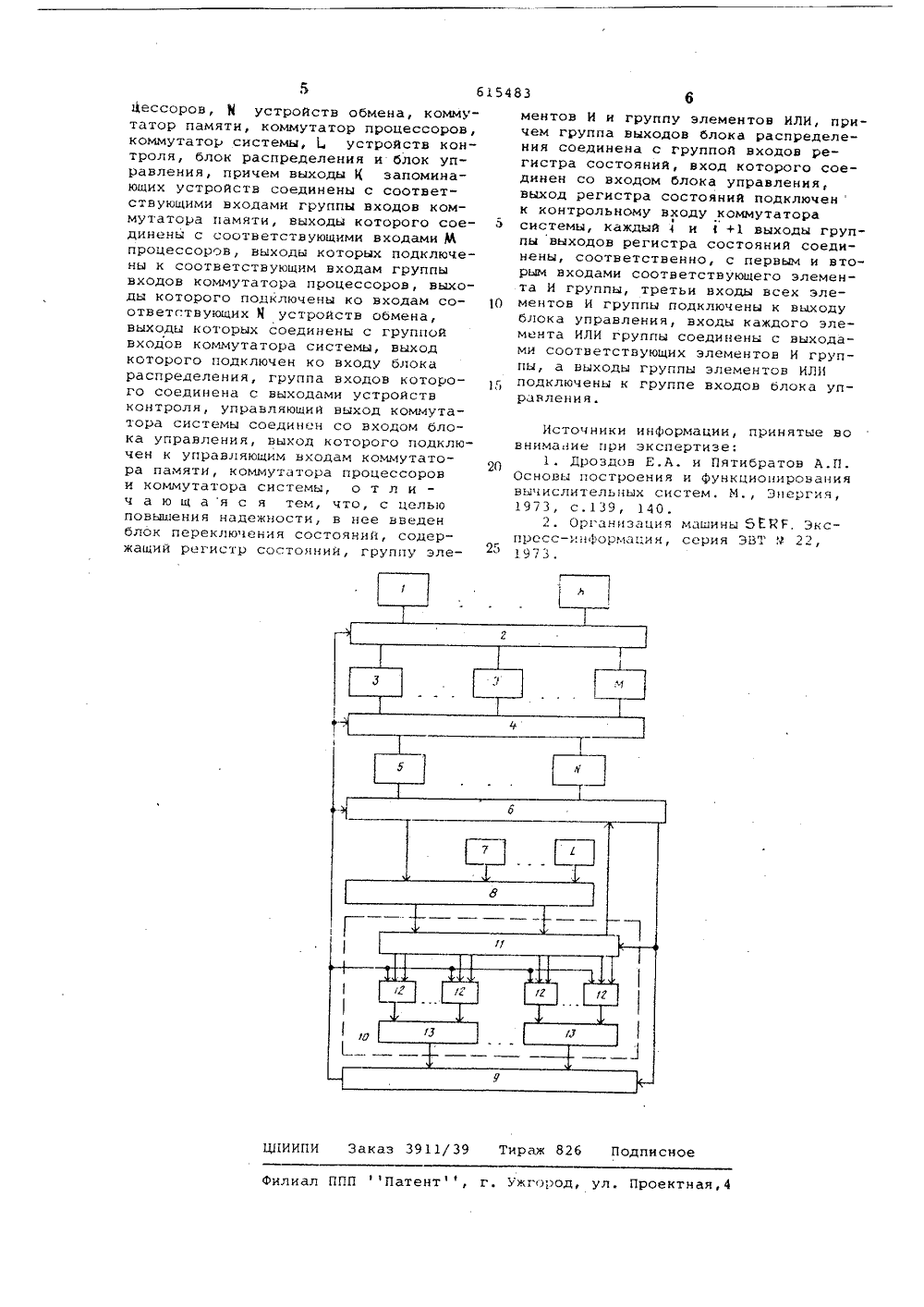

Союз Советскик Социалистическик Республик(3) 615483 К АВТОРСКОМУ СВИДЕТЕЛЬСТ ополнительное авт. свид-в 51) М. Ка С 06 Р 15/1) Заявлен 1,74 (21) 1988284/18 ием заявкис присоед (23) Приор осудврстгенный комнот овета Министров СССР оо делам инобрегенийи открытий 0778, Бюллетень26 3) Опубликова 1;14 (088. 8)) Лата опубликования описания 190678(71) Заявите 4) ВЫЧИСЛИТЕЛЬНАЯ СИС 1 ЕМЛ Известны вычислительные. системы, содержащие блоки запоминающих устройств, процессоров и устройств обмена, связанные между собой через коммутаторы 11,В этих системах возможно изменение путей передачи информации между блоками путем реконфигурации с помощью коммутаторов. В известных системах отсутствует возможность автоматической перестройки структуры при возникновении неисправностей.Этт снижает надежность работы. Наиболге близкой к изобретению по технической сущности является вычислительная система, содержащая К запоминающих устройств, М процессоров, Я устройств обмена, коммутатор памяти, коммутатор процессоров, коммутатор системы, Ь устройств контроля, блок расйределения и блок управления, при- ф чем выходы К запоминающих устройств соединены с соответствующими входами группы входов коммутатора памяти, выходы которого соединены с соответствующими входами М процессоров, выходы которых подключены к соответствующим входам группы входов коммутатора процессоров, выходы которых подключены ко входам соответствующих М устройств обмена, выходы которых соединены с группой входов коммутатора системы, выход которого подключен ко входу блока распределения, группа .входов которого соединена с выходами устройств контроля, управ-. ляющий выход коммутатора системы соединен со входом блока управления, выход которого подключен к управляющим входам коммутатора памяти, коммутатора процессоров и .коммутатора системы 21. Эта известная система характеризуется потерей работоспособности при отказе. управляющего процессора,несмотря на то, что в системе есть исправные процессоры. Отказ наступает потому, что в систе" ме отсутствует воэможность автоматической реконфигурации, обеспечивающей отключение отказавшего процессора и назначение вместо него управляющим одного иэ исправных. Все это снижает надежнрсть работы системы.Йель изобретения в .повышение на дежности. В описываемой системе это достигается тем, что в .нее введен блок переключения состояний, содер-. жащий регистр состояний, группу элементов И и группу элементов ИЛИ. Кроме того, группа выходов блока распределения соединена с группой входов регистра состояний, вход которого соединен со входом блока управления, выход регистра состояний подклюнен к контрольному входу коммутаторасистемы. У .группы выходов рЕгистрасостояний каждыйи 1 + 1 выходысоединены, соответственно, с первым и вторым входами соответствующегоэлемента И группы, при этом третьивходы всех элементов И группы подключены к выходу блока управления, вхо ды каждого элемента ИЛИ группы соединены с выходами соответствующихэлементов И группы, а выходы группыэлементов ИЛИ подключены к группе входов блока управления. 15На чертеже представлена блок-схема описываемой вычислительной системы.Она содержит К запоминающих устройств 1, связанных через коммутатор памяти 2 с М процессорами 3, ко торые, в свою очередь, связаны через коммутатор процессоров 4 с Ч устройствами обмена 5. Выходы устройств обмена подключены к коммутатору 8 системы. Система содержит Ь устройств контроля 7, блок распределения 8, блок управления 9, а также блок переключения состояний 10, в состав которого входят регистр состояний 11, группа элементов И 12: и группа элементов ИЛИ 13. Выход коммутатора б полк.ю.ен ко входу блока распределенкч 8, остальные входы которого подключены к выходам устройств контроля /. Управляющий выход коммутатора 6 соединен со входом блока управления 9. Выход блока управления подключен к управляющим входам коммутатора памяти 2, коммутатора процессоров 4 и коммутатора 6. Группа выходов блока распределения 8 соединена с группой 40 входов регистра состояний 11, вход которого объединен со входом блока управления 9. Выход регистра состояний 11 подключен к контрольному входу коммутатора 6. У группы выходов 45 регистра состояний 11 каждыйи+1 выходы соединены, соответственно, с первым и вторым входами соответствующего элемента И 12 группы. Третьи входы всех элементов И 12 под-, 50 ключены к выходу блока управления 9, а выходы элементов И 12 группы соединены со входами соответствующего элемента ИЛИ 13 группы. Выходы элементов ИЛИ подключены к группе вхо дов блока управления 9.При возникновении отказа в каком- либо из устройств вычислительной системы сигнал с соответствующего устройства контроля поступает на вход 0 блока распределения 8. Этот .блок запрещает прохождение сигналов с тех устройств контроля, которые неисправны сами или уже известно, что контролируемые пми устройства неисправны и отключены соответствующим коммутатором. С этой целью управляющий проессор через коммутатор б записывает оответствующий код запрета в блок распределения 8. Сигналы устройства контроля, разрешенные к обработке, фиксируются в регистре состояний 11 и через комбинационные схемы И и ИЛИ поступают на входы блока управления 9, который изменяет код управления соответствующим коммутатором.Каждая группа схем И, объединенных схемой ИЛИ, управляет только одним выходом блока управления 9.Для того, чтобы при возникновении отказа учесть предыдущее состояние всех коммутаторов, сигналы с выхода блока управления заводятся на третьи входы всех схем И 12.Кроме схемного автоматического изменения кода управления коммутаторами, в системе возможна программная реконфигурация. При программной реконФигурации регистр состояний опрашивается процессорами, которые в зависимости от его содержимого вырабатывают коды запрета для блока распределения и коды для блока управления. Управляющий процессор, например Л посылает эти коды, соответственно, в блок распределения 8 и в блок управления 9 через коммутатор процессоров 4, устройства обмена 5 и коммутатор б. По этой же связи может быть записан код и в регистр состояний 11. Так, например, после обработки содержимого регистра состояний управляющих процессор посылает в него нулевой код. Код на выходе блока управления в каждый момент времени однозначно определяет конфигурацию вычислительной системы и тем самым обеспечивается назначение управляющего процессора, т.е. процессора, имеющего доступ к регист" ру состояний, блоку распределения и блоку управления.Смена управляющего процессора при возникновении в нем отказа, зафиксированного устройствами контроля, про" изводится автоматически коммутатором процессоров в соответствии с поступающим на него из блока управления кодом. Например, при отказе 1 .-го процессора подключается 3 +1-й процессор. В том случае, если 3 +1-й процессор неисправенналичие связи выхода блока управлейия со входами схем И обеспечит подключение Х +2-го процессора и т.д.Переключение запоминающих устройств 1 и устройств обмена 5 производится аналогично.Формула изобретенияВычислительная система, содержащая К запоминающих устройств, М про615483 раж 826 Подписное Заказ 3911/39 ИИПИ лиал ППП Па т асессоров, Й устройств обмена, коммутатор памяти, коммутатор процессоров,коммутатор системы, , устройств контроля, блок распределения и блок управления, причем выходы Ц запоминающих устройств соединены с соответствующими входами группы входов коммутатора памяти, выходы которого соединены с соответствующими входами Мпроцессоров, выходы которых подключены к соответствующим входам группывходов коммутатора процессоров, выходы которого подключены ко входам соответствующих Ц устройств обмена,выходы которых соединены с группойвходов коммутатора системы, выходкоторого подключен ко входу блокараспределения, группа входов которого соединена с выходами устройствконтроля, управляющий выход коммутатора системы соединен со входом блока управления, выход которого подключен к управляющим входам коммутатора памяти, коммутатора процессорови коммутатора системы, о т л ич а ю щ а я с я тем, что, с цельюповышения надежности, в нее введенблок переключения состояний, содержащий регистр состоянии, группу элементов И и группу элементов ИЛИ, причем группа выходов блока распределения соединена с группой входов регистра состояний, вход которого соединен со входом блока управления,выход регистра состояний подключенк контрольному входу коммутатора6 системы, каждыйи ( +1 выходы группы выходов регистра состояний соединены, соответственно, с первым и вторым входами соответствующего элемента И группы, третьи входы всех эле 0 ментов И группы подключены к выходублока управления, входы каждого элемента ИЛИ группы соединены с выходами соответствующих элементов И группы, а выходы группы элементов ИЛИподключены к группе входов блока управления,Источники информации, принятые вовнимание при экспертизе:1. Дроздов Е,А. и Пятибратов А.П.Основы построения и Функционированиявычислительных систем. И., Знергия,1973, с.139, 140,2. Организация машины 5 ГКГ, Зкспрссс-ннормация, серия ЗБТ У 22,25 жгород, ул. Проектная,4

СмотретьЗаявка

1988284, 07.01.1974

ОРДЕНА ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ, ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ПРЕДПРИЯТИЕ ПЯ В-2969

АНТИМИРОВ ВЛАДИМИР МИХАЙЛОВИЧ, КОРОБЕЙЩИКОВА ТАТЬЯНА ВАСИЛЬЕВНА

МПК / Метки

МПК: G06F 15/16

Метки: вычислительная

Опубликовано: 15.07.1978

Код ссылки

<a href="https://patents.su/3-615483-vychislitelnaya-sistema.html" target="_blank" rel="follow" title="База патентов СССР">Вычислительная система</a>

Предыдущий патент: Устройство для контроля двоичнодесятичного дешифратора

Следующий патент: Устройство для подсчета количества и стоимости оцененных объектов

Случайный патент: Опора для трубопровода