Приемник аналоговых сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 572936

Авторы: Мироновский, Слаев

Текст

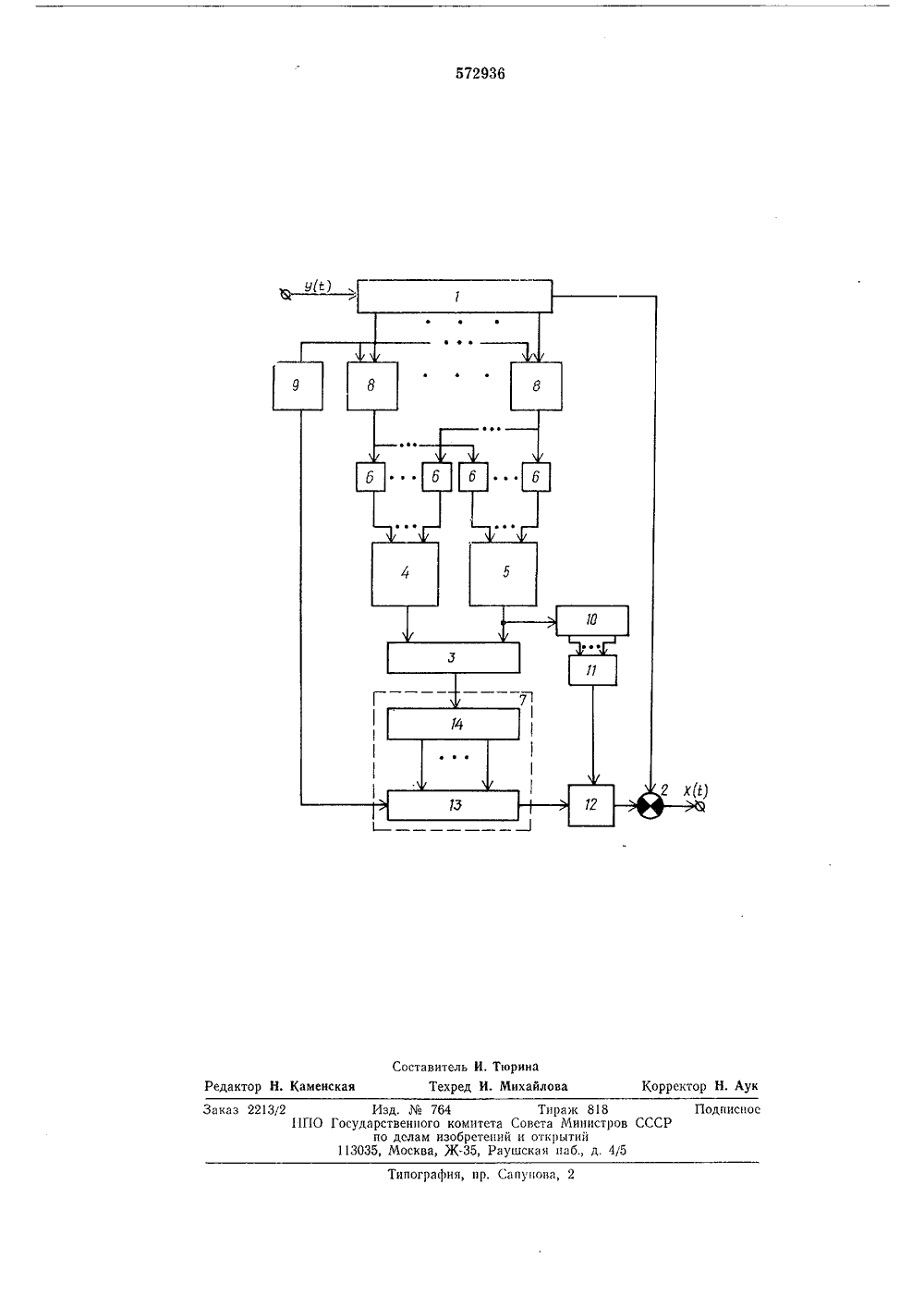

О П И С А Н И Е ц 572936ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Сова Советских Социалистических Республик) М. Кл.з Н 04 В 1/10 присоединением заявки М Государственный комитет Совета Министров СССР(088.8) елам изобретении и открытий ата опубликования описания 04.10,77 2) Авторы изобретеп(71) Заявител 54) ПРИЕМНИК АНАЛОГОВЫХ СИГНАЛОВ повышение точности Изобретение касается передачи информациии может использоваться для приема аналоговых сигналов.Известно устройство для преобразованиясигнала, содержащее линию задержки, отводы которой через вентили, управляемые блоком синхронизации, весовые умножители, сумматоры и блок деления соединены с дешифратором 11.Однако известное устройство обладает невысокой надежностью, обусловленной сложностью его аппаратурной реализации,Наиболее близким техническим решением кданному изобретению является приемник аналоговых сигналов, содержащий на выходе 15блок вычитания, одним из вхоДов соединенный с выходом многоотводной линии задержки, вход которой является входом приемника,а также последовательно соединенные блокделения, входы которого через первый и второй сумматоры подключены к соответствующим выходам двух групп весовых умножителей, и блок коррекции 12.Однако известный приемник имеет помехина выходе во время пауз в передаваемом сигнале.Цель изобретения -компенсации помех,Для этого в предлагаемом приемнике аналоговых сигналов между каждым из отводов Зо многоотводной линии задержки и входом соответствующего весового умножителя включе. ны вентили, управляемые блоком синхронизации, выход второго сумматора через дополнительную многоотводную линию задержки с дополнительным сумматором на выходе подключен к управляющему входу дополнительного вентиля, включенного между выходом блока коррекции и вторым входом блока вычитания, при этом блок коррекции выполнен в виде счетчика и дешифратора, выходы которого соединены с входами установки исходного состояния счетчика, а выход блока синхронизации дополнительно соединен со счетным входом блока коррекции.На чертеже представлена структурная электрическая схема предложенного приемника,Приемник содержит многоотводную линию задержки 1, вход которой является входом приемника, а выход соединен с первым входом блока вычитания 2, последовательно соединенные блок деления 3, входы которого через первый 4 и второй 5 сумматоры подключены к соответствующим выходам двух групп весовых умножителей б, и блок коррекции 7,Между каждым из отводов многоотводной линии задержки 1 и входом соответствующего весового умножителя б включены вентили 8, управляемые блоком синхронизации 9, Выход второго сумматора 5 через дополнительнуюмцогоогводцую линию задержки 10 с дополнительным сумматором 11 на выходе подключен к управляющему входу дополнительного вентиля 12, включенного между выходами блока коррекции 7 и вторым входом блока вычитания 2, п 1 лц этом блок коррекции 7 выполнен в виде счетчика 13 и дсшифратора 14, выходы которого соединены с входами установки исходного состояния счетчика 13, а выход блока синхронизации 9 дополнительно соединен со счстным входом блока коррекции 7.Г 1 риемник работает следующим образом.11 рицятый сигнал у (1) продолжительности Т, состоящий пз участков, два из которых явлгцотся избьлточными, поступает ца вход мцогоотводцой линии задержки 1. С (и+2) отводов мцогоотводцой лцццп задержки 1 сигналы подаются ца сигнальные входы вентилей 8, 1 элок синхронизации 9 открывает этц вентили 8 ца время Т/(и+2) в конце интервала Т. Участки сигнала у с выходов вентилей 8 через весовые умцожитсли 6 поступают на входы первого 4 и второго 5 сумматоров. Таким образом, ца выходе первого 4 и второго 5 сумматоров образуются два сигнала рассогласования длительности Т/(п+2), равной длительности одного участка, представляющие собой взвешенную с различными весовымп коэффициентами сумму (и+2) участков принятого сигнала у(1). Коэффициенты весовых умножителей 6 подбираются так, чтобы сигнал рассогласования с выхода второго сумматора 5 повторял форму напряжения помехи, а сиплал с выхода первого сумматора 4 был больше его в число раз, равное номеру участка сигнала, который поражен помехой.Сигналы рассогласования с выходов первого 4 и второго 5 сумматоров подаются на блок деления 3, с выхода которого напряжение, пропорциональное номеру участка, пораженного помехой, проходит на вход блока коррекции 7, а именно на дешифратор 14. Дешифратор 14 вырабатывает управляющий сигнал на одном из своих выходов с номером, соответствующим номеру участка, пораженного помехой. Этот сигнал подается на соответствующий вход установки исходного состояния счетчика 13, на счетный вход которого поступают с выхода блока синхронизации 9 импульсы с периодом следования Т/(а+2), На выходе счетчика 13 образуется сигнал, открывающий дополнительный вентиль 12 на время, соответствующее прохождению через блок вычитания 2 участка сигнала у(1), пораженного помехой. Сигнал рассогласовашгя с выхода второгосумматора 5, повторяющий форму напряжения помехи, поступает на вход дополнительной мцогоотводной линии задержки 10. С ее 5 (п -2) отводов, время задержки между которымц составляет Т/(а+2), многократно повлорсццый сигнал рассогласования через дополнительный сумматор 11 поступает на сигнальный вход дополнительного вентиля 12, с 10 выхода которого напряжение помехи поступает на второй вход блока вычитания 2. Таким образом, на выходе блока вычитания 2 получается сигнал х(1), который отличается от сигнала у(1) тем, что помеха в последнем 15 скомценсировапа.1 аким образом предлагаемое изобретениепозволяет повысить точность компенсации помех и тсм самым повысить точность цсрсдачц сигнала.20с 1)ор мула изобретения Приемник аналоговых сигналов, содержащий на выходе блок вычитания, одним из вхо дов соединенный с выходом многоотводнойлинии задержки, вход которой является входом приемника, а также последовательно соединенные блок деления, входы которого через первый и второй сумматоры подключены З 0 к соответствующим выходам двух групп весовых умножителей, и блок коррекции, о т л ичающийся тем, что, с целью повышения точности компенсации помех, между каждым из отводов мцогоотводной линии задержки и З 5 входом соответствующего весового умножителя включены вентили, управляемые блоком синхронизации, выход второго сумматора через дополнительную многоотводную линию задержки с дополнительным сумматором на вы ходе подключен к управляющему входу дополнительного вентиля, включенного между выходом блока коррекции и вторым входом блока вычитания, при этом блок коррекции выполнен в виде счетчика и дешифратора, вы ходы которого соединены с входами установкиисходного состояния счетчика, а выход блока синхронизации дополнительно соединен со счетным входом блока коррекции,Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР Мо 477549,кл, Н 04 В 1/10, 1973. 2. Авторское свидетельство СССР Мо 433526,55 кл. 6 08 С 19/16, 1972,572936 Подписное Заказ 22132 Изд, Мо 764 Тираж 818 11 ПО Государственного комитета Совета Министров СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5

СмотретьЗаявка

1968655, 10.10.1973

ПРЕДПРИЯТИЕ ПЯ А-1742, ЛЕНИНГРАДСКИЙ ИНСТИТУТ АВИАЦИОННОГО ПРИБОРОСТРОЕНИЯ

МИРОНОВСКИЙ ЛЕОНИД АЛЕКСЕЕВИЧ, СЛАЕВ ВАЛЕРИЙ АБДУЛЛОВИЧ

МПК / Метки

МПК: H04B 1/10

Метки: аналоговых, приемник, сигналов

Опубликовано: 15.09.1977

Код ссылки

<a href="https://patents.su/3-572936-priemnik-analogovykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Приемник аналоговых сигналов</a>

Предыдущий патент: Счетчик импульсов

Следующий патент: Устройство уплотнения группы ортогональных сигналов

Случайный патент: Рабочее оборудование одноковшового экскаватора