Интегратор потоков многоразрядных приращений

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 548869

Авторы: Золотовский, Коробков

Текст

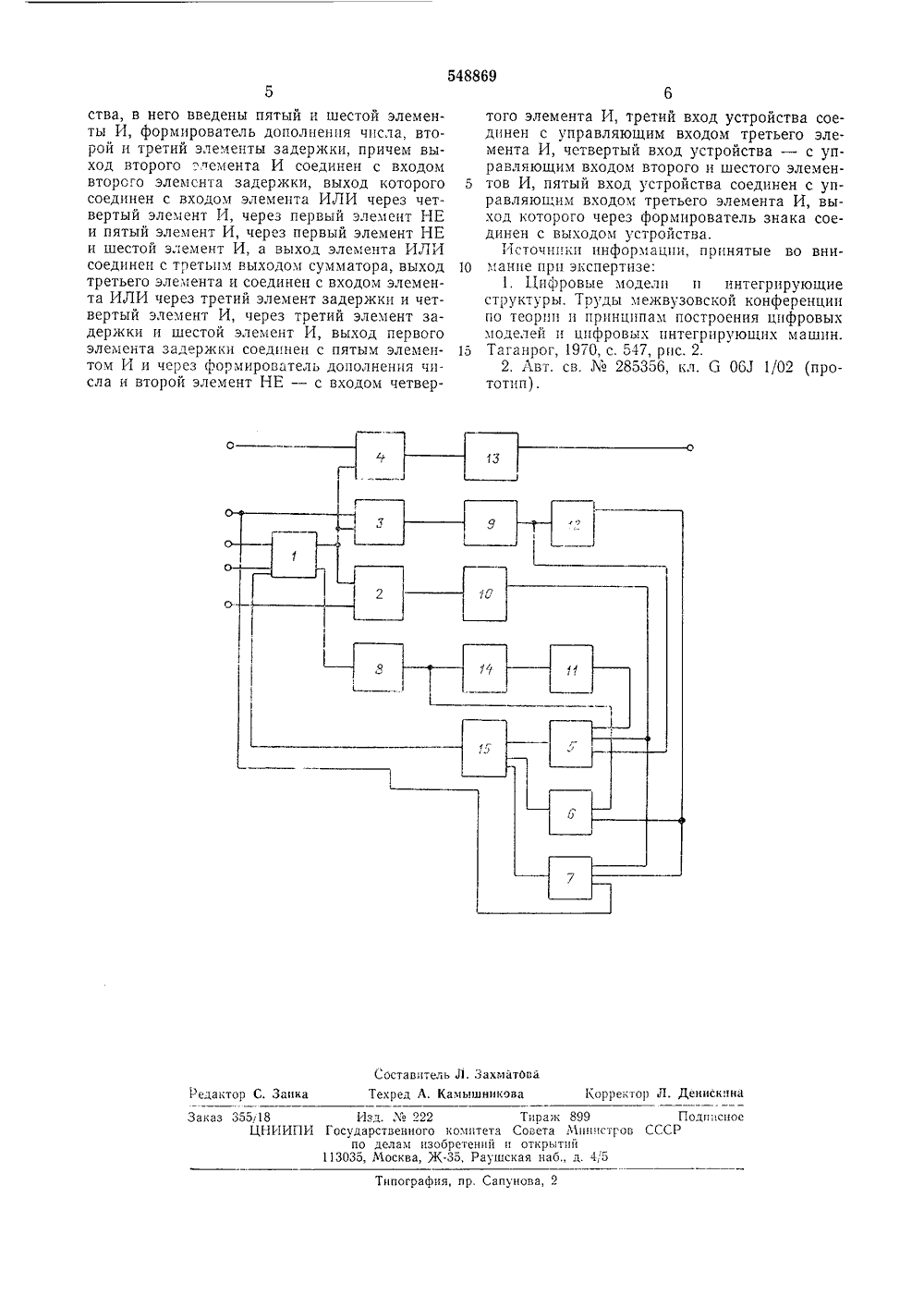

ссс 548869 Союз Советских Социалистических Республик61) Дополнительное к авт. свид-ву22) Заявлено 03.01.75 (21) 2091230/24 63 1/02 51) М. Кл ссоединением заявки М Государственный комитес(23) ПриоритетОпубликовано 28.02.7Дата опубликования Совета Мини в СССРетенийй(53) УДК 681,325(088.8 Бюллетеньписания 15.03.7 о делам на откры 2) Авторьс изобретени обков и В. Е, Золотовский(71) Заявитель лмыков хническии инстит Цель изобретения заключается в упрощениисумматора потоков приращений и повышенииточности его работы. тво может быть исвычислптельной теховых интегрирующих Предлагаемое устройспользовано в цифровойнике, в частности в цифрмашинах.Известно устройство 1, содержащее два сумматора, сдвигающий регистр, схемы анализа приращений, блок памяти, блоки изменения знака приращения, элементы И, ИЛИ.Недостатками этого устройства являются большой объем оборудования и динамическая погрешность метода,Наиболее близким техническим решением является устройство 2, содержащее сумматор, первый и второй входы которого соединены с первым и вторым входом устройства, первый выход - с входами первого, второго и третьего элементов И, а второй выход - с входом первого элемента задержки, четвертый элеме И, формссрователь эаа, два элемента НЕ, элемент ИЛИ.Недостатками этого устройства являются большой расход оборудования; суммирование потоков приращений сопровождается динамической погрешностью, которая тем больше, чем выше суммарная скорость потоков приращений на входе сумматора; средние скорости входных приращений необходимо ограничивать таким образом, чтобы средняя суммарная скорость входных потоков приращений не превышала максимальную. Поставленная цель достигается тем, что вустройство введены пятый и шестой элементы И, формирователь дополнения числа, второй и третий элементы задержки, причем выход второго элемента И соединен с входом второгоИ элемента задержки, выход которого соединенс входом элемента ИЛ 11 через четвертый элемент И, через первый элемент НЕ и пятый элемент И, чеоез первый элемент НЕ и шестой элемент И, а выход элемента ИЛ 11 соединен с третьим выходом сумматора. Выход третьего элемента И соединен с входом элемента ИЛИ через третий элемент задержки и четвертый элемент И, через третий элемент задержки и шестой элемент И, выход первого элемента задержки соединен с пятым элементом И и через формирователь дополнения числа и второй элемент НЕ - с входом четвертого элемента И, третий вход устройства соединен с управляющим входом третьего элемеьста И, 25 четвертый вход устройства - с управляющимвходом второго и шестого элементов И. Пятый вход устройства соедсснен с управляющим входом третьего элемента И, выход которого через формирователь знака соединен с выхо дом устройства. 54) ИНТЕГРАТОР ПОТОКОВ МНОГОРАЗРЯДНЫХ ПРИРАЩЕНИЙФункциональная схема предложенного устройства приведена на чертеже, где сумматор 1, элементы И 2 - 7, элементы задержки 8 - 10, элементы НЕ 11, 12, формирователь знака 13, формирователь дополнения числа 14, элемент ИЛИ 15.Рассмотрим работу устройства.Приращение ЛУ, формируемое ца выходе устройства, имеет тот же формат, что ц входные приращения (т значащих разрядов и один знаковый) . Однако вес кванта выходного приращения увеличен вдвое по сравнению с весом кванта входных приращений, следова- тельно( -т. ) 12 где ЛХ ц ЛУ - входные приращения.Благодаря этому алгоритм работы описываемого устройства имеет следующий вцд. При сложении входных приращений ЛХ и ЛУ формируется т+2 разрядное слово, содержащее т+2 значащий разряд и один знаковый, Полученное слово в устройстве квантуется по уровню 2 ЛХ, где ЛХ - квант входных приращений, В результате квантования т старших значащих разрядов и один знаковый разряд через схему формирования знака поступают на выход устройства, как приращение ЛЛ,Младший значащий разряд совместно со знаком представляют собой остаток квантования ц запоминаются на один шаг интегрирования в устройстве. В следующем шаге интегрирования при формировании приращения ЛЛ остаток квантирования складывается с очередными приращениями ЛХ и ЛУ.В символической форме алгоритм работы устройства примет вцд 55 ао 65 Лг,= Р:,.(ЛХ,+И,+5 дгпос 1 5, = Р:".,(Х, + Л , + 5 1) 5,=РРХ,+Л 1,+5 ) где (ЛХ,+ЛУ;+5) - алгебраическая сумма входных приращений ЛХ;, Лупоступающих на вход устройства в 1-и шаге интегрирования, и остатка квантования 5; сформированного в предыдущем шаге интегрирования; гпос 15; - модуль остатка квантования в 1-м шаге; 31 дп 5; - знак остатка квантования в 1-м шаге; Р в- функция расчленения, позволяющая выделить часть числа с разряда 1 по разряд т включительно.Рассмотрим как реализуется приведенный алгоритм в описываемом устройстве.Сформированная в сумматоре сумма ЛХ;4-ЛУ;+5;, поступает на входы элементов 2, 3, 4. Элемент 4 реализует первое уравнение системы (1), На второй вход элемента 4 поступает управляющий сигнал, выделяющий приращение ЛЛ; (т. е, отсекающцй младший разряд суммы). Через формирователь знака 13 приращение ЛУ, поступает на выход устройства. 510 15 90 25 зо 35 40 45 50 Элемент И 2 реализует второе уравнение системы (1), На его второй вход поступает управляющий сигнал, пропускающий на элемент задержки 10 только младший разряд суммы. Лналогично элемент И 3 под воздействием управляющего сигнала пропускает на элемент задержки 9 знак остатка квантования. Элементы задержки 9, 10 хранят остаток квантования до начала следующего шага ццтс рцрованпя. К началу следующего шага ос.аток квантования возникает на выходах элементов задержки 9, 10 и присутствует там в течение всего следующего шага интегрирования. Если остаток квантования равен нулю, открыт элемент И 6, цепь переноса сумматора замкнута как обычно и на его выходе сформируется сумма ЛХ+ЛК.Если остаток квантования равен +ЛХ, откроются элементы И 6, И 7, Через элемент И 7 в младший разряд суммы поступит дополнительная единица, т. е. сформируется величина ЛХ+Л У+ЛХ.Если остаток квантования равен - ЛХ, откроется элемент И 5 и на вход переноса поступит проинвертированное дополнение переноса. Но Инв(допА) =А - 2 - дгде Инв(доп А) - инверсия дополнения величины А; 2 - " - единица младшего разряда.Следовательно на вход сумматора поступит перенос, уменьшенный на одну единицу младшего разряда, в результате в сумматоре сформируется величина.Построение сумматора многоразрядных приращений описанным способом позволяет заметным образом сократить расход оборудования, так как отпадает необходимость во втором сумматоре, регистре сдвига, схеме анализа приращения, сокращается число логических схем.Известные в настоящее время двухвходовые сумматоры потоков многоразрядных приращений требуют порядка 400 логических схем. Для построения описанного устройства необходимо менее 60 логических схем, следовательно расход оборудования сократится в 6 - 7 раз.Так как в описанном устройстве рассогласование отсутствует, динамическая ошибка окажется равной нулю.Скорости суммцруемых потоков приращений могут быть любыми, никаких ограничений на ццх не накладывается. Ф ор мула изобретенияИнтегратор потоков многоразрядных приращений, содержащий сумматор, первый и второй входы которого соединены с первым и вторым входом устройства, первый выход - с входами первого, второго и третьего элементов И, а второй выход - с входом первого элемента задержки, четвертый элемент И, формирователь знака, два элемента НЕ, элемент ИЛИ, отличающийся тем, что, с целью повышения точности и упрощения устрой548869 Составитель 11. ЗахматбваТехред А. Камышникова Корректор Л. Денискина Редактор С. Заика 355(18 Из ь222 Тираж 899 Подписное ЦНИИПИ Государственного комитета Совета Мипист 1 ов СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская паб., д. 4 5Заказ Типография, пр. Сапунова, 2 ства, в него введены пятый и шестой элементы И, формирователь дополнения числа, второй и третий элементы задержки, причем выход второго элемента И соединен с входом второго элемснта задержки, выход которого соединен с входом элемента ИЛИ через четвертый элемент И, через первый элемент НЕ и пятый элемент И, через первый элемент НЕ и шестой элемент И, а выход элемента ИЛИ соединен с третьим выходом сумматора, выход третьего элемента и соединен с входом элемента ИЛИ через третий элемент задержки и четвертый элемент И, через третий элемент задержки и шестой элемент И, выход первого элемента задержки соединен с пятым элементом И и через формирователь дополнения числа и второй элемент НЕ - с входом четвертого элемента И, третий вход устройства соединен с управляющим входом третьего элемента И, четвертый вход устройства - с управляющим входом второго и шестого элемен тов И, пятый вход устройства соединен с управляюгцим входом третьего элемента И, выход которого через формирователь знака соединен с выходом устройства.Источники информации, принятые во вни мание при экспертизе:1. Цифровые модели и интегрирующиеструктуры. Труды межвузовской конференции по теории и принцнпам построения цифровых моделей и цифровых интегрирующих машин.15 Таганрог, 1970, с, 547, рис. 2.2. Авт, св. М 285356, кл. 6 065 1/02 (прототип).

СмотретьЗаявка

2091230, 03.01.1975

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМЕНИ В. Д. КАЛМЫКОВА

КОРОБКОВ РОАЛЬД ВАЛЕНТИНОВИЧ, ЗОЛОТОВСКИЙ ВИКТОР ЕВДОКИМОВИЧ

МПК / Метки

МПК: G06J 1/02

Метки: интегратор, многоразрядных, потоков, приращений

Опубликовано: 28.02.1977

Код ссылки

<a href="https://patents.su/3-548869-integrator-potokov-mnogorazryadnykh-prirashhenijj.html" target="_blank" rel="follow" title="База патентов СССР">Интегратор потоков многоразрядных приращений</a>

Предыдущий патент: Устройство для классификации электрических сигналов по форме

Следующий патент: Многовходовой сумматор потоков тернарных приращений

Случайный патент: Устройство для проветривания метанообильных выработок большой протяженности