Вычислительная система для решения линейных дифференциальных уравнений

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

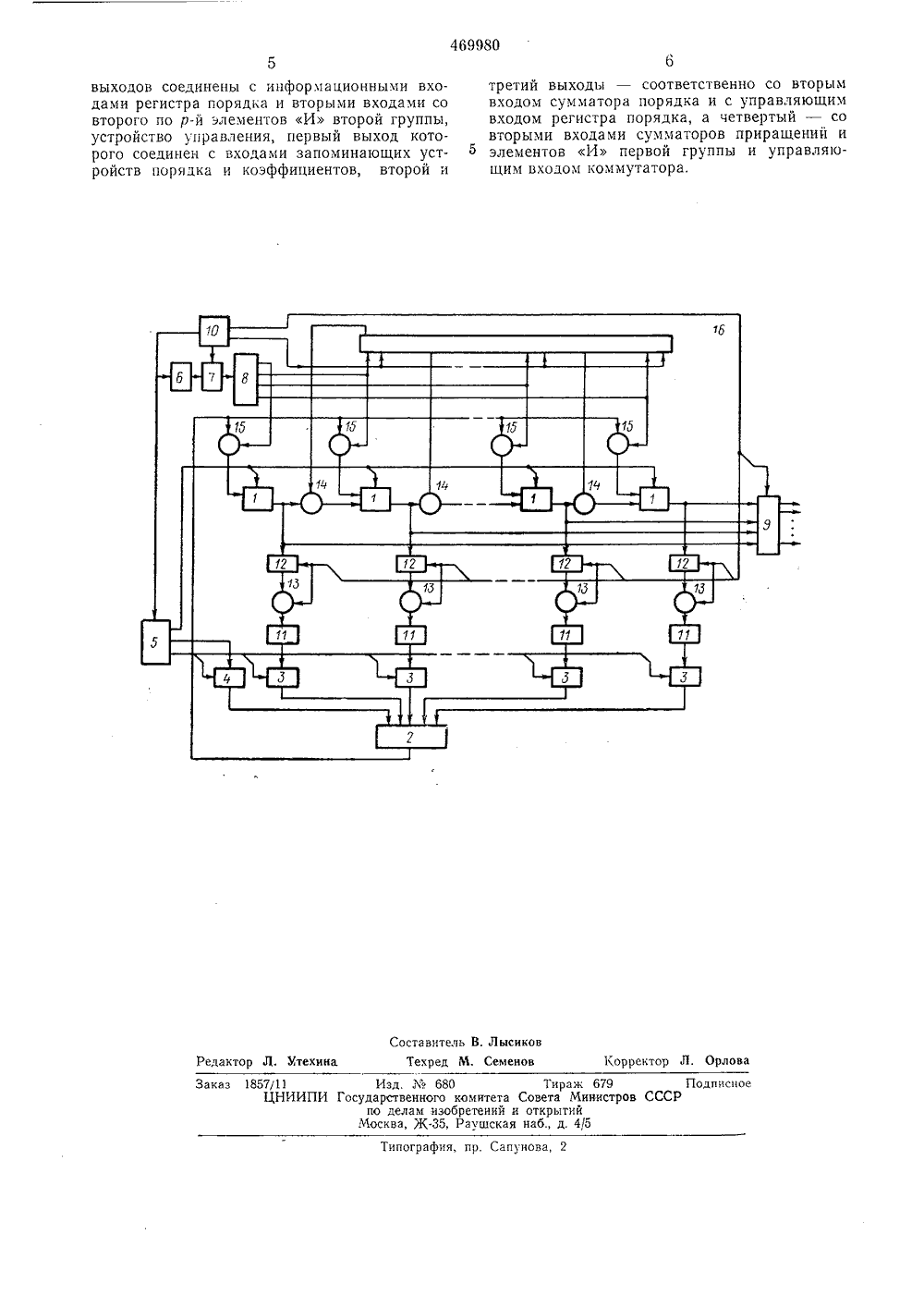

О П И"(: А Н И Е(11) 469980ИЗОБРЕТЕНИЯ Союз Советских Социалистических Республик(23). ПриоритетОпубликовано 05.05.75, Бюллетень1Дата опубликования описания 30.07.5 61 1,0 Государственный комитет Совета Ьинистроо СССР по делам изобретенийи открытий( 13)К 681 323 (088 8 72) Авторы изобретени В. Г 1, Во.он и Л, 1. Козлов рдена Ленина институт кибернетики АН Украинской С(1 тель 4) ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ РЕЖДЕНИЯ ЛИНЕЙНЫХ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ бласти вычисл Изобретение относится к 1 ельной техники.Известны вычислительные щения линейных дифферен ний, содержащие устройство ций, р устройств умножени интеграторов, (р + 1) вход первые р входов которого по дам устройств умножения (р+1)-й вход подключен к ва умножения функций. системы для рециальных уравнеумножения функя переменных, р овый сумматор, дключены к выхопеременных, а выходу устройстЦелью изобретения является расширение функциональных возможностей устройства.С этой целью предложенная система содер жит регистры приращений, выходы которых соединены с первыми входами устройств умножения переменных, первую группу элементов И, выходы которых соединены с входами регистров приращений, сумматоры, прнра шений, первые входы которых подключены к выходам интеграторов, а выходы соединены с первыми входами элементов И первой группы, коммутатор, информационные входы которого подключены к выходам интеграторов, 25 а выходы соединены с выходами системы, запоминающее устройство коэффициентов, первый выход которого соединен с первым входом устройства умножения функций, второй - со вторыми входами устройств умножения 30 функций и переменных, а третий - с первыми входами интеграторов, вторую группу элементов И, первые входы которых подключены к выходу (р+ 1)-входового сумматора, а выходы к вторым входам интеграторов, третью группу элементов И, первые входы которых подключены к выходам с первого по (р - 1)-й интеграторов, а выходы соединены с третьими входами со 2-го по р-й интеграторов, запоминающее устройство порядков, сумматор порядка, первый вход которого подключен к выходу запоминающего устройства порядка, регистр порядка, выходы которого соединены со вторыми входами элементов И третьей группы, дешифратор порядка, вход которого подключен к выходу сумматора порядка, первый выход ко второму входу первого элемента И второй группы, а остальные (р - 1) выходов соединены с информационными входами регистра порядка и вторыми входами со второго по р-й элементов И второй группы, устройство управления, первый выход которого соединен с входами запоминающих устройств порядка и коэффициентов, второй и третий - соответственно со вторым входом сумматора порядка и с управляющим входом регистра порядка, а четвертый - со вторыми входамп сумматоров приращений и элементов И первой группы и управляющим входом коммутатора, 4699805 1 О 15 20 3Вычислительная система представлена на чертеже.Она содержит интеграторы 1, (р+1)-входовый сумматор 2, устройства умножения переменных 3, устройство умножения функций 4, запоминающее устройство коэффициентов 5, запоминающее устройство порядка 6, сумматор порядка , дешифратор порядка 8, коммутатор 9, устройство управления 10, регистры приращений 11, сумматоры приращений 12, элементы И 13 - 15 и регистр порядка 16,Вычислительная система работает следующим образом,Вычислительная система позволяет решать одновременно несколько дифференциальных уравнений любого порядка или систему дифференциальных уравнений любого порядка.1(аждая цепочка содержит такое число интеграторов 1, каков порядок соответствующего ей дифференциального уравнения. Связи между отдельными цепочками интеграторов 1 разомкнуты, а в цепочках выход предыдущего интегратора 1 соединен с первым входом последующего интегратора 1,Из запоминающего устройства коэффициентов 6 на входы интеграторов 1 поступают значения начальных условий, На входы устройств умножения переменных 3 и вход устройства умножения функций 4 из запоминающего устройства коэффициентов 5 поступают коды коэффициентов первого уравнения системы. С регистров приращений 11 на входы устройств умножения переменных 3 поступают коды приращений зависимых переменных. На вход устройства умножения функций 4 из запоминающего устройства коэффициентов 5 поступает значение приращения функции. Тогда на выходе сумматора 2 получается значение, соответствующее величине правой часги первой строки системы уравнений. Это значение поступает на вход интегратора 1 первой цепочки интеграторов через первый элемент И 15, который открывается при помощи сигнала, поступающего с дешифратора 8. Аналогично вычисляются последующие строки системы уравнений, С выходов интеграторов 1 приращения переменных поступают на входы сумматоров приращений 12, где они накапливаются, Затем суммарные значения приращений переменных заносятся в регистры приращений 11 через элементы И 13, которые открываются под воздействием сигналов устройства управления 10, а сумматоры приращений 12 под воздействием сигналов устройства управления 10 сбрасываются в нулевое состояние.Процесс вычислений, описанный выше, повторяется многократно, так что на выходах интеграторов 1 получаются значения приращений искомых переменных, которые выдаются на выходы коммутатора 9 под воздействием сигнала, поступающего с устройства управления 10.При одновременном решении нескольких независимых между собой дифференциальных 25 30 35 40 45 50 55 60 65 уравнений вычисление правых частей каждого уравнения проводится последовательно. Последовательность подключения выхода сумматора 2 ко входам интеграторов 1 той или иной цепочки интеграторов определяется сигналами, поступающими с дешифратора 8. Выходы интеграторов 1, соединенные с входами коммутатора 9, в соответствии с решаемой системой уравнений, подключаются к выходам коммутатора 9 под воздействием сигнала, поступающего с устройства управления 10.Последовательность выдачи кодов порядков из запоминающего устройства порядка 6 на вход сумматора лорядкаи последовательность выдачи кодов коэффициентов и приращений функций из запоминающего устройства коэффициентов 5 на входы устройств умножения переменных 3 определяется устройством управления 10,Предмет изобретенияВычислительная система для решения линейных дифференциальных уравнений, содержащая устройство умножения функций, р устройств умножения переменных, р интеграторов, (р+1)-входовый сумматор, первые р входов которого подключены к выходам устройств умножения переменных, а (р + 1) -й вход подключен к выходу устройства умножения функций, отличающаяся тем, что, с целью расширения функциональных возможностей системы, она содержит регистры приращений, выходы которых соединены с первыми входами устройств умножения переменных, первую группу элементов И, выходы которых соединены с входами регистров приращений, сумматоры приращений, первые входы которых подключены к выходам интеграторов, а выходы соединены с первыми входами элементов И первой группы, коммутатор, информационные входы которого подключены к выходам интеграторов, а выходы соединены с выходами системы, запоминающее устройство коэффициентов, первый выход которого соединен с первым входом устройства умножения функций, которой - со вторыми входами устройств умножения функций и переменных, а третий - с первыми входами интеграторов, вторую группу элементов И, первые входы которых подключены к выходу (р + 1) -входового сумматора, а выходы с вторым входом интеграторов, третью группу элементов И, первые входы которых подключены к выходам с первого по (р - 1) -й интеграторов, а выходы соединены с третьими входами со второго по р-й интеграторов, запоминающее устройство порядка, сумматор порядка, первый вход которого подключен к выходу запоминающего устройства порядка, регистр порядка, выходы которого соединены со вторыми входами элементов И третьей группы, дешифратор порядка, вход которого подключен к выходу сумматора порядка, первый выход - ко второму входу первого элемента И второй группы, а остальные (р - 1)469980 третий выходы - соответственно со вторым входом сумматора порядка и с управляющим входом регистра порядка, а четвертый - со вторыми входами сумматоров приращений и элементов И первой группы и управляющим входом коммутатора. Составитель В. Лысиков едактор Л,. Утехина Техред М. Семенов корректор Л. ОрлИзд. М 680сударственного комитета по делам изобретений Москва, Ж.35, Раушска Заказ 1857/11ЦНИИПИ ПодписноеСССР отрафип, пр. Сапунова, 2 выходов соединены с и 11 формационными входами регистра порядка и вторыми входами со второго по р-й элементов И второй руины, устройство управления, первый выход которого соединен с входами запоминающих устройств порядка и коэффициентов, второй и Тираж 679Совета Министроткрытийнаб., д. 4/5

СмотретьЗаявка

1852742, 02.12.1972

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ АН УКРАИНСКОЙ ССР

БОЮН ВИТАЛИЙ ПЕТРОВИЧ, КОЗЛОВ ЛЕОНИД ГРИГОРЬЕВИЧ

МПК / Метки

МПК: G06J 1/02

Метки: вычислительная, дифференциальных, линейных, решения, уравнений

Опубликовано: 05.05.1975

Код ссылки

<a href="https://patents.su/3-469980-vychislitelnaya-sistema-dlya-resheniya-linejjnykh-differencialnykh-uravnenijj.html" target="_blank" rel="follow" title="База патентов СССР">Вычислительная система для решения линейных дифференциальных уравнений</a>

Предыдущий патент: Устройство для моделирования газотурбинного двигателя

Следующий патент: Устройство для отображения графической информации

Случайный патент: Регулируемый насос