Устройство для деления чисел, представленных в число импульсных кодах

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

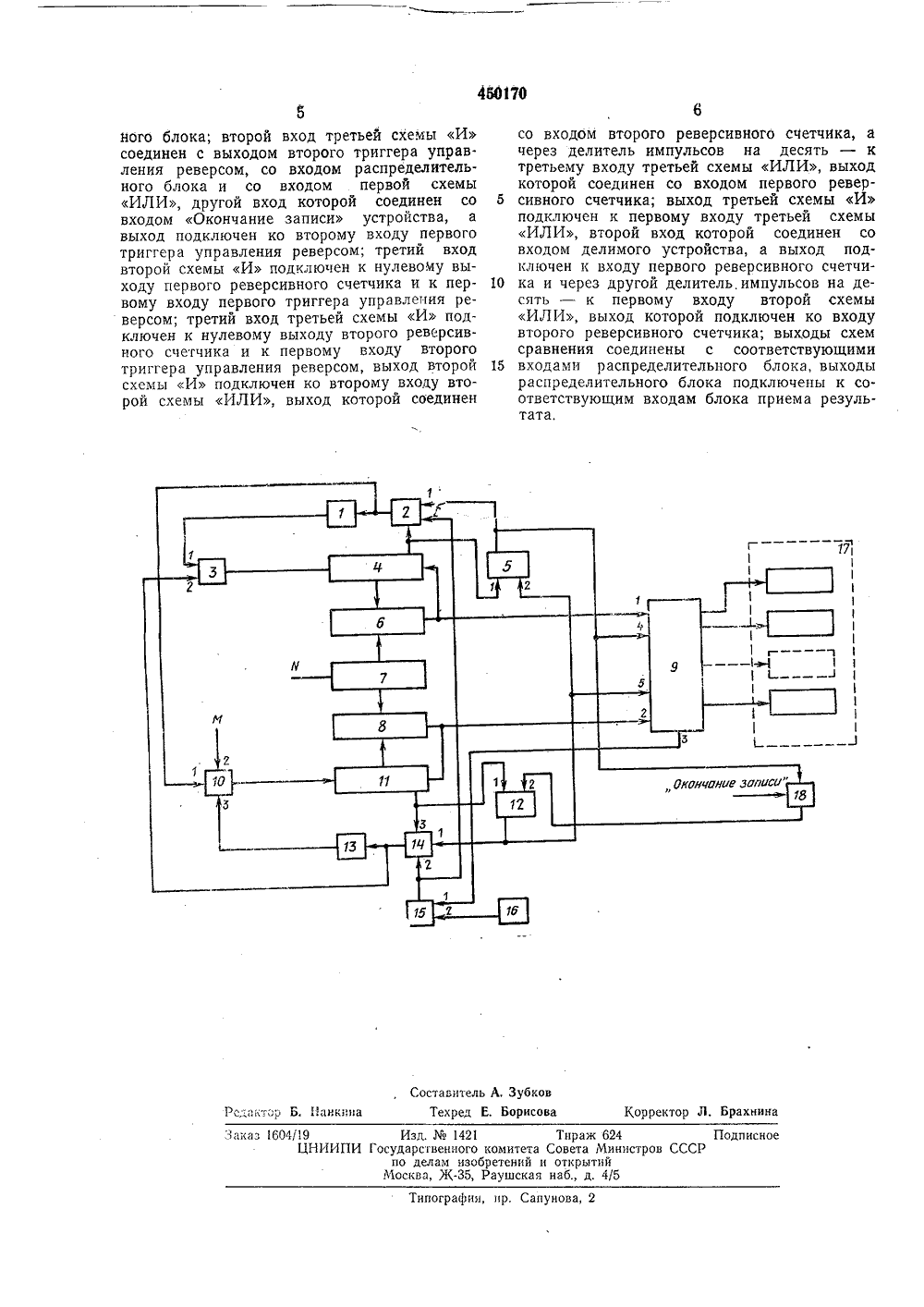

(и 40 УО ОПИСАЙИ Е ИЗОБРЕТЕНИЯ ааааа боватскиа Гациалистических Республик(32) ПриоритетОпубликовано 15,11.74, Бюллетень42Дата опубликования описания 10.07.75 61 7/39 51) М Государственный комитет Совета Министров СССР по делам изобретенийи открытий 53) УДК 681.3 08(54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯЕДСТАВЛЕННЫХ В ЧИСЛО-ИМПУЛЬ ИСЕЛ,ЫХ КОДАХ Изобретение относится к электроизмерительной технике и предназначено для деления чисел, представленных в число-импульсных кодах, в частности, может быть использовано в устройствах обработки информации автоматических систем контроля и управления.Известно устройство для деления чисел, представленных в число-импульсных кодах, содержащее два реверсивных счетчика, выходы которых подключены ко входам соответствующих схем сравнения, другие входы которых соединены с выходами счетчика делителя, а выходы подключены к нулевым входам соответствующих реверсивных счетчиков, два делителя импульсов на десять, тактовый генератор, распределительный блок, блок приема результата, два триггера управления реверсом, логические схемы И, ИЛИ.Недостатком известного устройства является то, что время вычисления прямо пропорционально требуемой точности получения пезультата.С целью повышения быстродействия устройства выход тактового генератора подключен ко входу первой схемы И, другой вход которой соединен с выходом распределительного блока, а выход подключен к первым входам второй и третьей схем И, второй вход второй схемы И соединен с выходом первого триггера управления реверсом, со вторым входом второго триггера управления реверсом и входом распределительного блока; второй вход третьей схемы И соединен с вы ходом второго три 1 гера управления реверсом, со входом распределительного блока и со входом первой схемы ИЛИ, другой вход которой соединен со входом Окончание записи устройства, а выход подключен 0 ко втором) входу первого триггера управления реверсом; третий вход второй схемы И подключен к нулевому выходу первого реверсивного счетчика и к первому входу первого триггера управления реверсом; третий вход 5 третьей схемы И подключен к нулевомувыходу второго реверсивного счетчика и к первому входу второго триггера управления реверсом, выход второй схемы И подключен ко второму входу второй схемы ИЛИ, 0 выход которой соединен со входом второгореверсивного счетчика, а через делитель импульсов на десять - к третьему входу третьей схемы ИЛИ, выход которой соединен со входом первого реверсивного счетчи ка; выход третьей схемы И подключен кпервому входу третьей схемы ИЛИ, второй вход которой соединен со входом делимого устройства, а выход подключен к входу первого реверсивного счетчика и через другой 0 делитель импульсов на десять - к первомувходу второй схемы ИЛИ, выход которой подключен ко входу второго реверсивного счетчика; выходы схем сравнения соединены с соответствующими входами распределительного блока, выходы распределительного блока подключены к соответствующим входам блока приема результата.Сущность изобретения заключается в том, что в устройстве не числитель умножается на число, кратное десяти, для повышения точности операции деления, а остаток от деления числителя на знаменатель, что дает существенный выигрыш в быстродействии.На чертеже изображена блок-схема изобретения, где:1 - делитель импульсов на десять; 2 - логическая схема И; 3 - логическая схема ИЛИ; 4 - реверсивный счетчик; 5 - триггер управления реверсом; 6 - схема сравнения; 7 - счетчик делителя; 8 - схема сравнения; 9 - распределительный блок; 10 - логическая схема ИЛИ; 11 - реверсивный счетчик; 12 - триггер управления реверсом;13 - делитель импульсов на десять; 14 - логическая схема И; 15 - логическая схема И; 16 - тактовый генератор; 17 - блок приема результата; 18 - логическая схема ИЛИ.Работа устройства заключается в следующем,В исходном состоянии реверсивные счетчики 4, 11 обнулены и находятся в режиме суммирования. На схему И 15 поступает сигнал разрешения с выхода 3 распределительного блока 9. Схемы И 2, 14 закрыты по первым входам.На вход двоичного счетчика 7 поступает число-импульсный код делителя У. После записи делителя на вход схемы ИЛИ 10 поступает число-импульсный код делимого М, Двоичный счетчик 7, схема сравнения 8 и реверсивный счетчик 11 образуют пересчетную схему с коэффициентом пересчета 1: Л. С выхода схемы сравнения 8 снимается целочисленное значение результата деленияМУ= и заносится через распределительМный блок 9 в декады целой части блока приема результата. После окончания поступления число-импульсного кода делимого М вырабатывается импульс Окончание записи, который перебрасывает триггер 12 управления реверсом, в результате чего реверсивный счетчик 11 переключается в режим вычитания и схема И 14 открывается по первому входу. На третий вход схемы И 14 поступает сигнал разрешения при наличии в счетчике 11 остатка от деления. При отсутствии остатка деление прекращается,При наличии остатка импульсы с выхода схемы И 14 поступают на вход реверсивного счетчика 4 и через делитель 13 импульсов на десять - на вход реверсивного счетчика 11. С приходом в счетчик 11 количества импульсов, численно равного остатку Ь5 10 15 20 25 30 35 40 Предмет изобретенияУстройство для деления чисел, представленных в число-импульсных кодах, содержащее два реверсивных счетчика, выходы которых подключены ко входам соответствующих схем сравнения, другие входы которых соединены с выходами счетчика делителя, а выходы подключены к нулевым входам соответствующих реверсивных счетчиков, два делителя импульсов на десять, тактовый генератор, распределительный блок, блок приема результата, два триггера управления реверсом, логические схемы И, ИЛИ, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия, выход тактового генератора подключен ко входу первой схемы И, другой вход которой соединен с выходом распределительного блока, а выход подключен к первым входам второй и третьей схем И, второй вход второй схемы И соединен с выходом первого триггера управления реверсом, со вторым входом второго триггера управления реверсом и входом распределитель 45 50 55 60 65 схема И 14 закрывается по третьему входу, а триггер 12 перебрасывается в исходное состояние.Во время умножения остатка Ь, на десять счетчик , схема сравнения 6 и реверсивный счетчик 4 работают как пересчетная схема с коэффициентом пересчета 1: У. Результат10 Д 1от деления остатка Ь, У,= поступаетМс выхода схемы сравнения 6 на вход распределительного блока 9, с выхода которого заносится в соответствующую декаду дробной части блока приема результата. Переброс триггера 12 воздействует на триггер 5 и вызывает переключение его в противоположное исходному состояние, в результате чего реверсивный счетчик 4 переключается в режим вычитания и схема И 2 открывается по первому входу. При наличии остатка от деления в счетчике 4 на третий вход схемы И 2 подается сигнал разрешения, и импульсы с выхода схемы И 2 поступают на вход реверсивного счетчика 11 и через делитель 1 импульсов на десять - на вход реверсивного счетчика 4, Пусть остаток от де 10 д 1ления У= равен Ь Число Ь;К 10Ипоступает на вход пересчетной схемы (пози 10 Д 2 ции 7, 8, 11). Результат от деления У - с выхода схемы сравнения 8 поступает через распределительный блок 9 в более младшую декаду дробной части блока приема результата. С приходом в счетчик 4 количества импульсов, равного остатку Ь, схема И 2 закрывается, а триггер 5 перебрасывается в исходное состояние, что вызывает переключение триггера 12 и при наличии остатка Ьз начинается следующий цикл деления. Процесс деления прекращается с приходом сигнала запрета на вход схемы И 15.Составитель А. Зубков Техред Е, Борисова Корректор Д. Брахи аказ 16 9ЦН Изд.1421 Тираж 624ПИ Государственного комитета Совета Миниспо делам изобретений и открытийМосква, Ж, Раушскан наб., д, 4/5 ПодписиСССР пографин, пр. Сапунов ного блока; второй вход третьей схемы И соединен с выходом второго триггера управления реверсом, со входом распределительного блока и со входом . первой схемы ИЛИ, другой вход которой соединен со входом Окончание записи устройства, а выход подключен ко второму входу первого триггера управления реверсом; третий вход второй схемы И подключен к нулевому выходу первого реверсивного счетчика и к первому входу первого триггера управления реверсом; третий вход третьей схемы И подключен к нулевому выходу второго реверсивного счетчика и к первому входу второго триггера управления реверсом, выход второй схемы И подключен ко второму входу второй схемы ИЛИ, выход которой соединен со входом второго реверсивного счетчика, а через делитель импульсов на десять - к третьему входу третьей схемы ИЛИ, выход которой соединен со входом первого ревер сивного счетчика; выход третьей схемы Иподключен к первому входу третьей схемы ИЛИ, второй вход которой соединен со входом делимого устройства, а выход подключен к входу первого реверсивного счетчи ка и через другой делитель, импульсов на десять - к первому входу второй схемы ИЛИ, выход которой подключен ко входу второго реверсивного счетчика; выходы схем сравнения соединены с соответствующими 15 входами распределительного блока, выходыраспределительного блока подключены к соответствующим входам блока приема результата.

СмотретьЗаявка

1868268, 08.01.1973

ПРЕДПРИЯТИЕ ПЯ В-8751

ГРИБОК Н. И, ОБУХАНИЧ Р. -А. В

МПК / Метки

МПК: G06F 7/39

Метки: деления, импульсных, кодах, представленных, чисел, число

Опубликовано: 15.11.1974

Код ссылки

<a href="https://patents.su/3-450170-ustrojjstvo-dlya-deleniya-chisel-predstavlennykh-v-chislo-impulsnykh-kodakh.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для деления чисел, представленных в число импульсных кодах</a>

Предыдущий патент: Устройство для умножения

Следующий патент: Устройство для вычисления коэффициентов многочлена

Случайный патент: Волокнистая масса для изготовления теплоизоляционного материала