Дешифратор-•, pi i ц4и. 4l. 41, . », j i

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

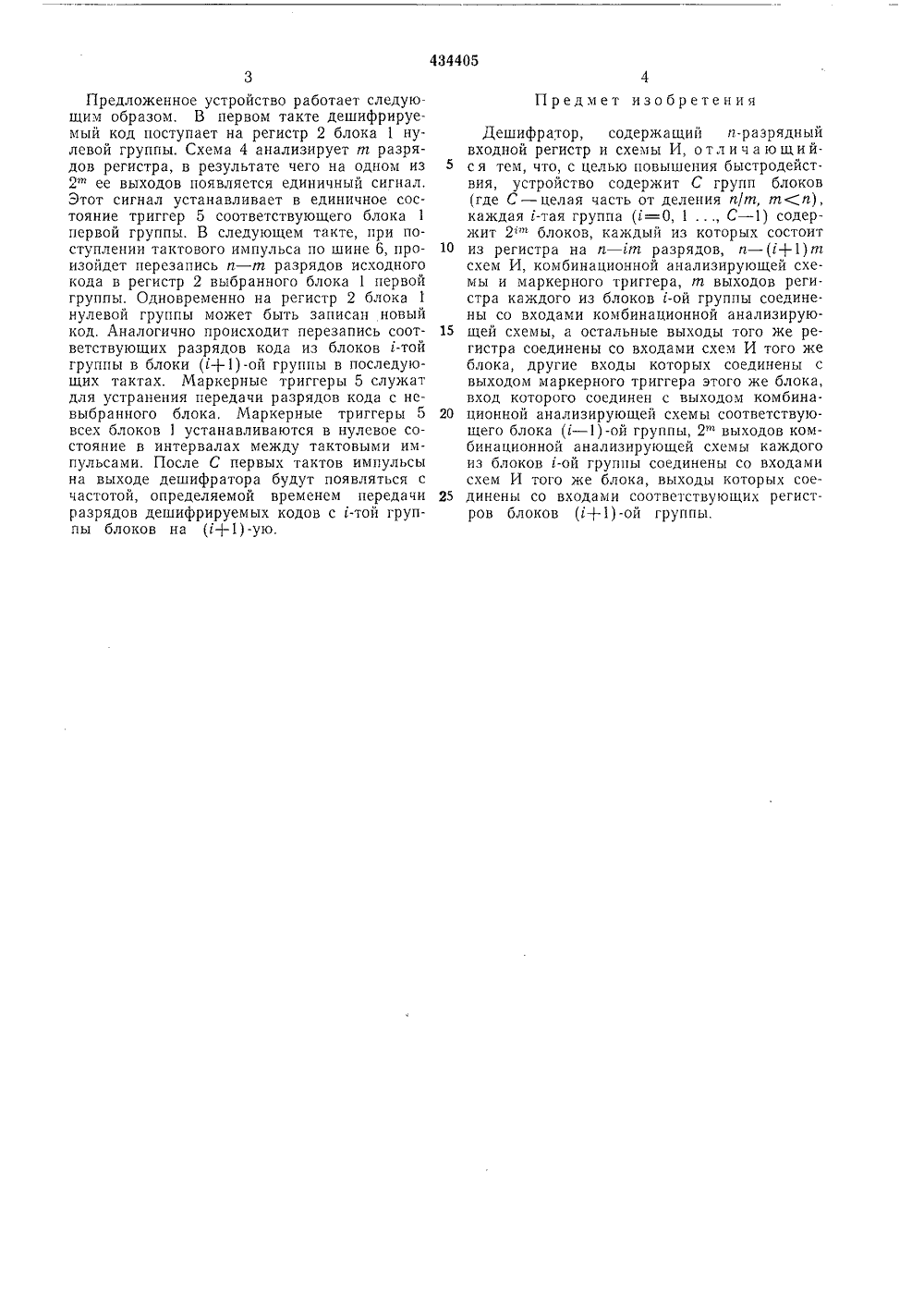

О П И С А Н И Е (и) 434405ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советских Социалистических Республик(51) М. Кл, 6 06 5/02 Государственный комитет Совета Министров СССР по делам изобретений и открытий(72) Авторы изобретения В. Ю. Десятун, В, И. Корнейчук, В, Л. Тарасенко и А. К, Тесленко Киевский ордена Ленина политехнический институт имени 50-летия Великой Октябрьской социалистической революции(71) Заявитель ИфРАТО 5 И того жесо входамиков (+1)На фиг.на фиг. 2 -тора. ласти вычислиено для испольройствах больгх соединень гистров бло лока, выходы которь соответствующих ре ой группы.изображена схема деш схема одного пз блоков ратора; шифраИзобретение относится к оотельной техники и предназначзования в запоминающих устшой емкости.Известны дешифратор ы, состоящие из 5 и-разрядного входного регистра и схем И.Быстродсйствие гаких дешифра горов определяется временем прохождения сигнала через самую длинную цепочку схем И.Цель изобретения - повышение быстродей ствия.Это достигается тем, что устройство содержит С групп блоков (где С - целая часть от деления и/т, т(п), каждая г-тая группа . (г=0, 1, 2, , С - 1) содержит 21 щ блоков, 15 каждый из которых состоит из регистра на г - гт разрядов, п - (г+1)т 1 2 схем И, комбинационноп анализирующей схемы и маркер- ного триггера, т выходов регистра каждого из блоков г-ой группы соединены со входами 20 комбинационной анализирующей схемы, а остальные выходы того же регистра соединены со входами схем И того же блока, другие входы которых соединены с выходом маркер- ного триггера этого же блока, вход которого 25 соединен с выходом комбинационной анализирующей схемы соответствующего блока (г - 1) -ой группы, 2 выходов комбинационной анализирующей схемы каждого из блоков г-ой группы соединены со входами схем 30 3,сшпфратор сос 1 оит пз С групп блоков 1 (где С - целая часть от деления г/т, т(п), Каждая г-тая группа (=0, 1 , С - 1) содержит 2 п блоков. Каждый блок г-той группы (см. фиг. 2) состоит из регистра 2 на и - гт разрядов, 2" п - (+1)т 1 схем И 3, комбинационной анализирующей схемы 4 и маркерного триггера 5. При этом т выходов регистра 2 соединены со входами схемы 4. Каждый из остальных выходов регистра 2 соединен с 2" схемами И 3. Каждый из выходов схемы 4 соединен со входами схем И 3, к которым подключены различные выходы регистра 2. Схемы И 3 соединены также с выходом маркерного триггера 5 и с тактовой шиной 6 дешифратора. Выходы схем И 3 каждого блока 1 =той группы подключены на входы регистров 2 2" блоков (г+1)-ой группы,Входы маркерных триггеров 4 каждого из 2" блоков 1 г-той группы соединены с 2 выходами схемы 4 одного из блоков 1 (г - 1)-ой группы.Предложенное устройство работает следующим образом. В первом такте дешифрируемый код поступает на регистр 2 блока 1 нулевой группы. Схема 4 анализирует т разрядов регистра, в результате чего на одном из 2 ее выходов появляется единичный сигнал. Этот сигнал устанавливает в единичное состояние триггер 5 соответствующего блока 1 первой группы. В следующем такте, при поступлении тактового импульса по шине 6, произойдет перезапись а - т разрядов исходного кода в регистр 2 выбранного блока 1 первой группы, Одновременно на регистр 2 блока 1 нулевой группы может быть записан новый код, Аналогично происходит перезапись соответствующих разрядов кода из блоков -той группы в блоки (+1)-ой группы в последующих тактах. Маркерные триггеры 5 служат для устранения передачи разрядов кода с не- выбранного блока, Маркер ные триггеры 5 всех блоков 1 устанавливаются в нулевое состояние в интервалах между тактовыми импульсами, После С первых тактов импульсы на выходе дешифратора будут появляться с частотой, определяемой временем передачи разрядов дешифрируемых кодов с -той группы блоков на (+1) -ую. Предмет изобретения Дешифратор, содержащий л-разрядныйвходной регистр и схемы И, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия, устройство содержит С групп блоков 1 где С - целая часть от деления пт, т(п), каждая -тая группа (=0, 1 , С - 1) содержит 2 блоков, каждый из которых состоит 10 из регистра на л - т разрядов, о - (+1)тсхем И, комбинационной анализирующей схемы и маркерного триггера, т выходов регистра каждого из блоков -ой группы соединены со входами комбинационной анализирую щей схемы, а остальные выходы того же регистра соединены со входами схем И того же блока, другие входы которых соединены с выходом маркерного триггера этого же блока, вход которого соединен с выходом комбина ционной анализирующей схемы соответствующего блока ( - 1) -ой группы, 2 выходов комбинационной анализирующей схемы каждого из блоков -ой группы соединены со входами схем И того же блока, выходы которых сое динены со входами соответствующих регистров блоков (+1) -ой группы.

СмотретьЗаявка

1736516, 10.01.1972

имени лети Великой Окт брьской социалистической революции

В. Ю. Дес тун, В. И. Корнейчук, В. П. Тарасенко, А. К. Тесленко

МПК / Метки

МПК: H03M 7/22

Метки: дешифратор, ц4и

Опубликовано: 30.06.1974

Код ссылки

<a href="https://patents.su/3-434405-deshifrator-pi-i-c4i-4l-41-j-i.html" target="_blank" rel="follow" title="База патентов СССР">Дешифратор-•, pi i ц4и. 4l. 41, . », j i</a>

Предыдущий патент: Преобразователь двоичного кода в двоично-десятичный

Следующий патент: Вычислительное устройство

Случайный патент: Устройство для измерения коэффициента передачи дифференциальных усилителей