Генератор случайных бинарных последовательностей, ., . -., . if-n7oplshunafj

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 428543

Авторы: Берштейн, Киевский, Романкевич

Текст

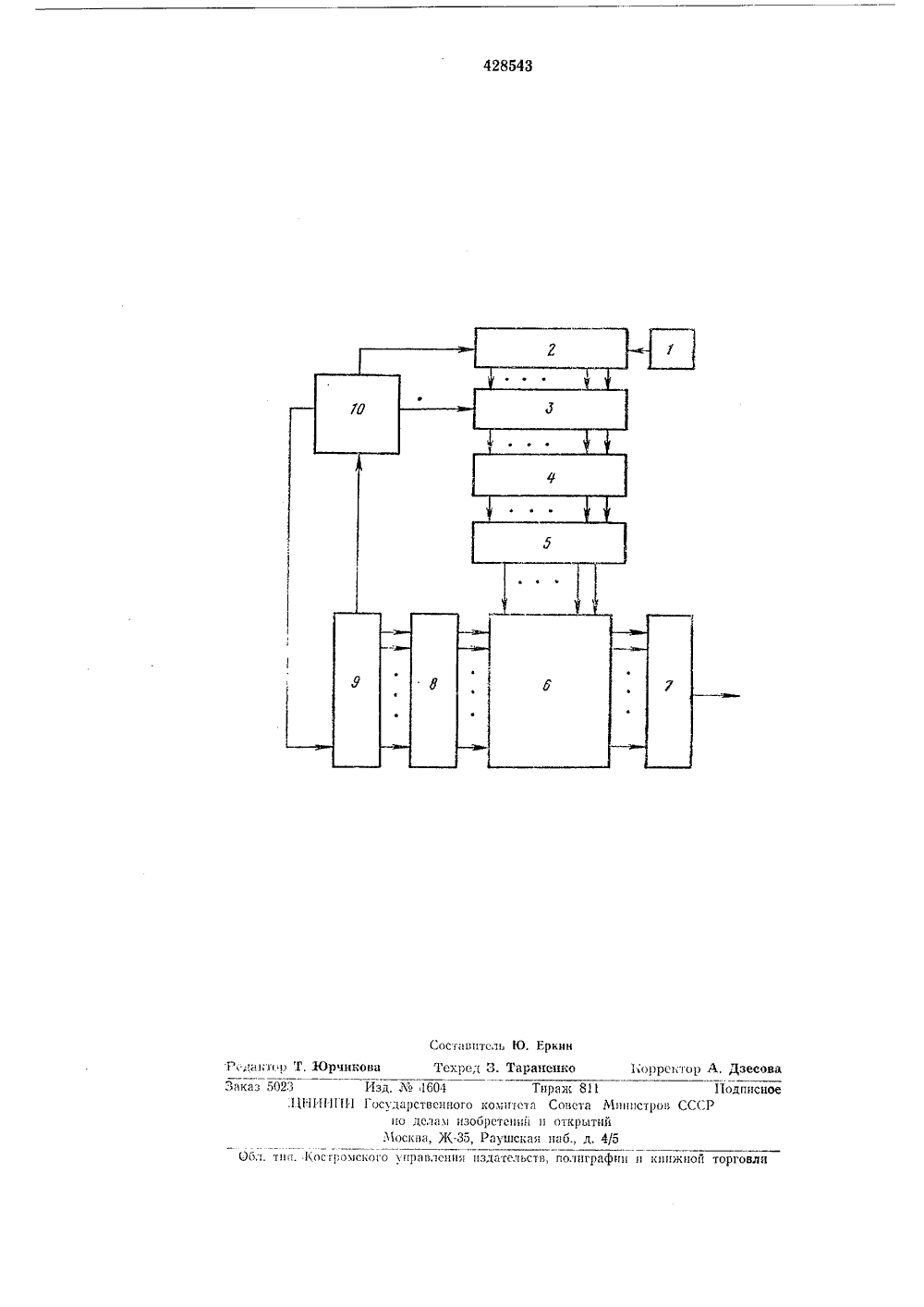

щ 428543 ОЛ ИСАНИ Е ИЗОБРЕТЕН ИЯ К АВТОРСКОМУ СВИДОИЬСТВУ Союз СоветскихСоциалистическихРеспублик(32) Приоритет -51) М.Кл. Н 031 5/156 Гесударствееый кемитеСевета Министров СССРпа делам изобретеиийи рткра 5 тий Опубликовано 15,05.74, БюллетеньДата опубликования описания 29,1.75 53) УДК 621,373 (08(71) Заявитель Киевский ордена Ленина политехнический институ Великой Октябрьской социалистической рев. 50-летияии у 5 ощим ооразом. чего цикла в регистаковые цоследоваов (символов), приа; вероятность едовательцость оды дешифратор4.(а следовательно, от длины реалмзуец той точности, с елнровать задаццый1.слц де 5 пцфратор Изобретецие отцосится к автоматике и вычислительной технике и может быть использовано в ЭВЛ.Известен генератор случайных бинарных последовательностей, содержащий генератор случайцых сигпалов, регистр сдвига, регистр памяти, блок схем совпадения, схему разделения, блок управления. Этот генератор имеетсложную структуру.Цель цзобретецня - уцрощецие генератора1 О случай цык бинарцык последовательцостей. Для этого выходы регистра памяти подсоедицецы к дешифратору, выходы которого соединены с входами сменной коммутационной матрицы. Выкоды матрицы подключены к одной группе входов блока схем совпадеция, выходы которого соединены с вкодами схемы разделения, а другая группа его входов - с выходами универсальцого мцогополюсцика. Входы цоследиего цодкл 5 очецы к выходам счетчика. 2 о Выходы блока управления соединены с управляющими входами регистра сдвига, регистра памяти и счетчика, вход блока уцравлешгя подключен к коапшдцым выходам счетчика.На чертеже приведена блок-схема предлагаемого генератора, который содержит генератор 1 случайцык сигцалов, вырабатываю 1цшй сигпалы с вероятностью Р=;, связан- з цый с регистром 2 сдвша, выходы которого подключены к вкодам регистра 5 памяти. Выходы регистра памяти подсоединены к входам дешифратора 4, который через сменную коммутационную матрицу б связац с блоком б схем совпадения. Выходы блока б через схему 7 разделения связаны с вкодом генератора 1. Вторые входы схем совпадеция блока б связаиы с выкодами универсального мцогоцолюсцика 8, к входам которого подключены разряды счетчика 9. Один цз выкодов этого счетчика соединен с входом блока 10 управления, выходы которого соединены с вкодамц счетчика 9, регистра сдвига и регистра цаи ятп. Работает генератор следВ начале каждого раборак 2 и д записаны одинтельцости двоичных сигналчем для каждого символа Р,а; =1)=;, - . Эта же п регистра 3 подается и вк Количество этих входов длина регистра) зависит мык последовательностей которой необходимо мод закон цк распределения,имеет пг+2" входов, то при любой входной последовательности на одном из 2" 2" выходов дешпфратора появляет 1 ся сигнал 1 с вероятностью Р= - . Эти2 а . 2 пвыходы подключены к входам матрицы 5, которая содержит 2-" многовходовых схем разделения (ровно столько, сколько существует последовательностей 2" . К каждой схеме разделения подключено такое количество выходовй; дешифратора, чтобы вероятность появления единицы на одном из этих выходов Рс =с 2 щ 2(1=1 2 22 л ) была равна заданной вероятности прохождения соответствующей последовательности. Это равенство может осуществляться приближенп - 2 п но с погрешностью Л= - 2 " 2 " . От 2сюда видно, что число т определяется точностью работы генератора,Матрица б определяет закон распределения выходных последовательностей. Меняя ее, можно настроить генератор па любой закон распределения. На одном из выходов матрицы появляется сигнал. Каждый из выходов матрицы подсоединен к одноъгу из входов схем совпадения блока б, К вторым входам схем совпадения блока б подключены выходы универсального многополюсника 8, на которых реализуются все булевы функции от гг переменных. Все возможные наборы переменных воспело:;ательно подаются на вход универсального многополюсннка с гг-разрядного счетчика 9. Количество этих наборов 2 " определяет длину реализуемой последователь.ности. Так как в течение одного цикла.работы генератора открыта только"одна, из.-схем совпадения блока б, то на выкод через,схему 7 разделения подается одна из-.последовагельностей, т, е, булевых функцйй;. уегализуемых универсальным многополюсником. Одновременно с пересчетом счетчика У занелняется регистр 2, Его содержимое переписывается затем в регистр 3, и начинается новый цикл работы генератора Далее все процессы повторяются.Предмет изобретенияГенератор случайных бинарных последовательностей, содержащий генератор случайных сигналов, регистр сдвига, регистр памяти, 20 блок схем совпадения, схему разделения,блок управления, отличающийся тем, что, с целью его упрощения, выходы регистра памяти.подсоединены к дешифраторувыходы которого соединены с входами сменной коммута ционной матрицы, ее выходы подключены кодной группе входов блока схем совпадения, выходы которого соединены с входами схемы разделения, а другая группа входов - с вы ходами универсального многополюсника, вхо ды которого подключены к выходам счетчикавыходы блока управления соединены с управ ляющнмп входами регистра сдвига, регистра памяти и счетчика, вход - - с командными вы.ходамн счетчика.,.1) 1ИзД. ЛеГосударе 04 ДПЕС ио дсМосква Об)л. Ти 1, (ОсЕромскоГО правлеп 1) издательств, по,ееГрафеи и нипккпой торГОВл синОГО колитета ал) изобретеш)йЖ.ЗО, Раушска) раж 811Совета Министров СССоткрытийпаб., д. 4/5

СмотретьЗаявка

1782367, 10.05.1972

А. М. Романкевич, М. С. Берштейн, Киевский ордена Ленина политехнический институт лети Великой Окт брьской социалистической революции

МПК / Метки

МПК: H03K 5/156

Метки: if-n7oplshunafj, бинарных, генератор, последовательностей, случайных

Опубликовано: 15.05.1974

Код ссылки

<a href="https://patents.su/3-428543-generator-sluchajjnykh-binarnykh-posledovatelnostejj-if-n7oplshunafj.html" target="_blank" rel="follow" title="База патентов СССР">Генератор случайных бинарных последовательностей, ., . -., . if-n7oplshunafj</a>

Предыдущий патент: Устройство задержки

Следующий патент: Устройство для временного сжатия входного сигнала

Случайный патент: Устройство для проверки исправности комплектов релейной защиты