Устройство для ввода и хранения данных для аналоговых вычислителей

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 378870

Автор: Вител

Текст

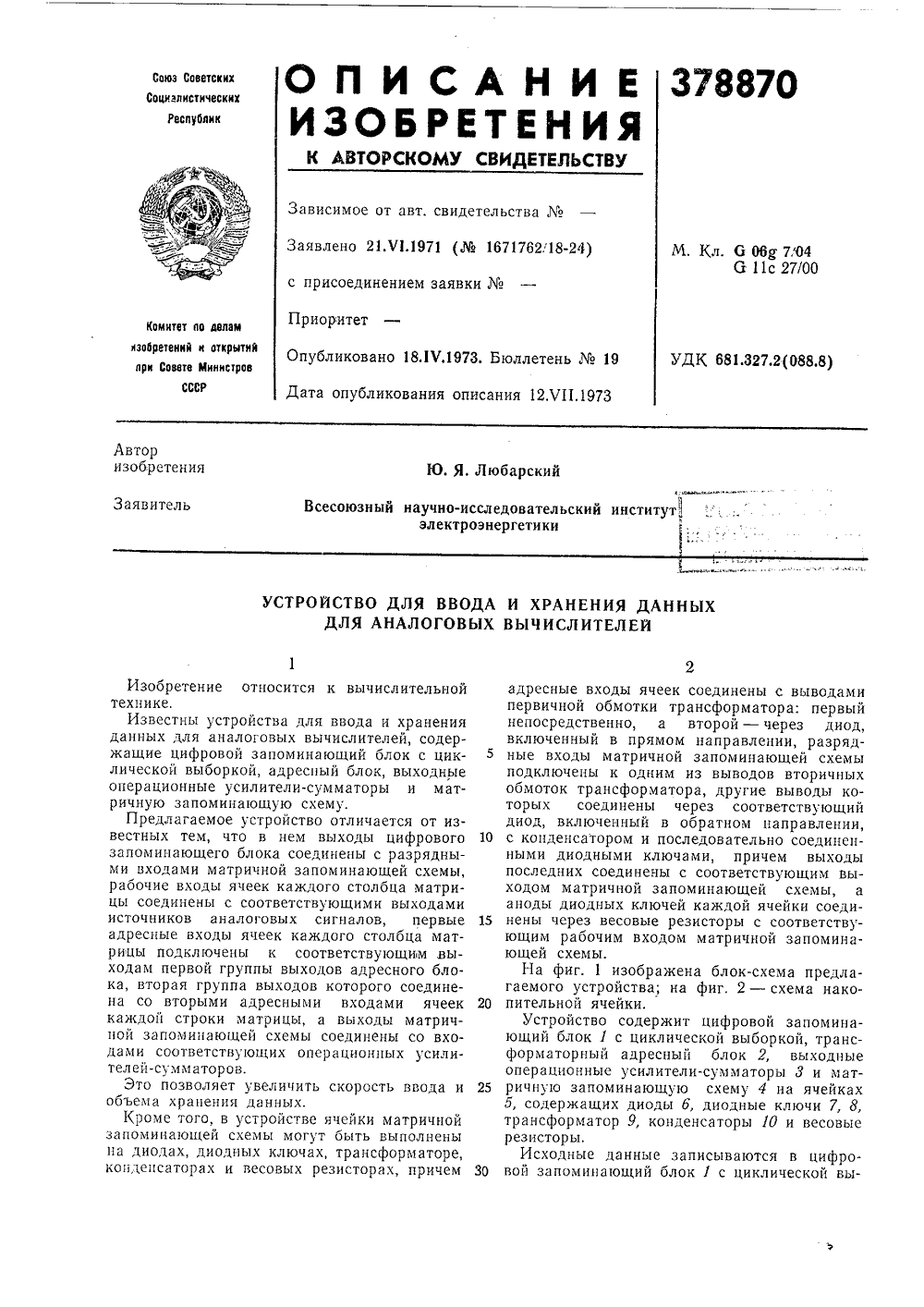

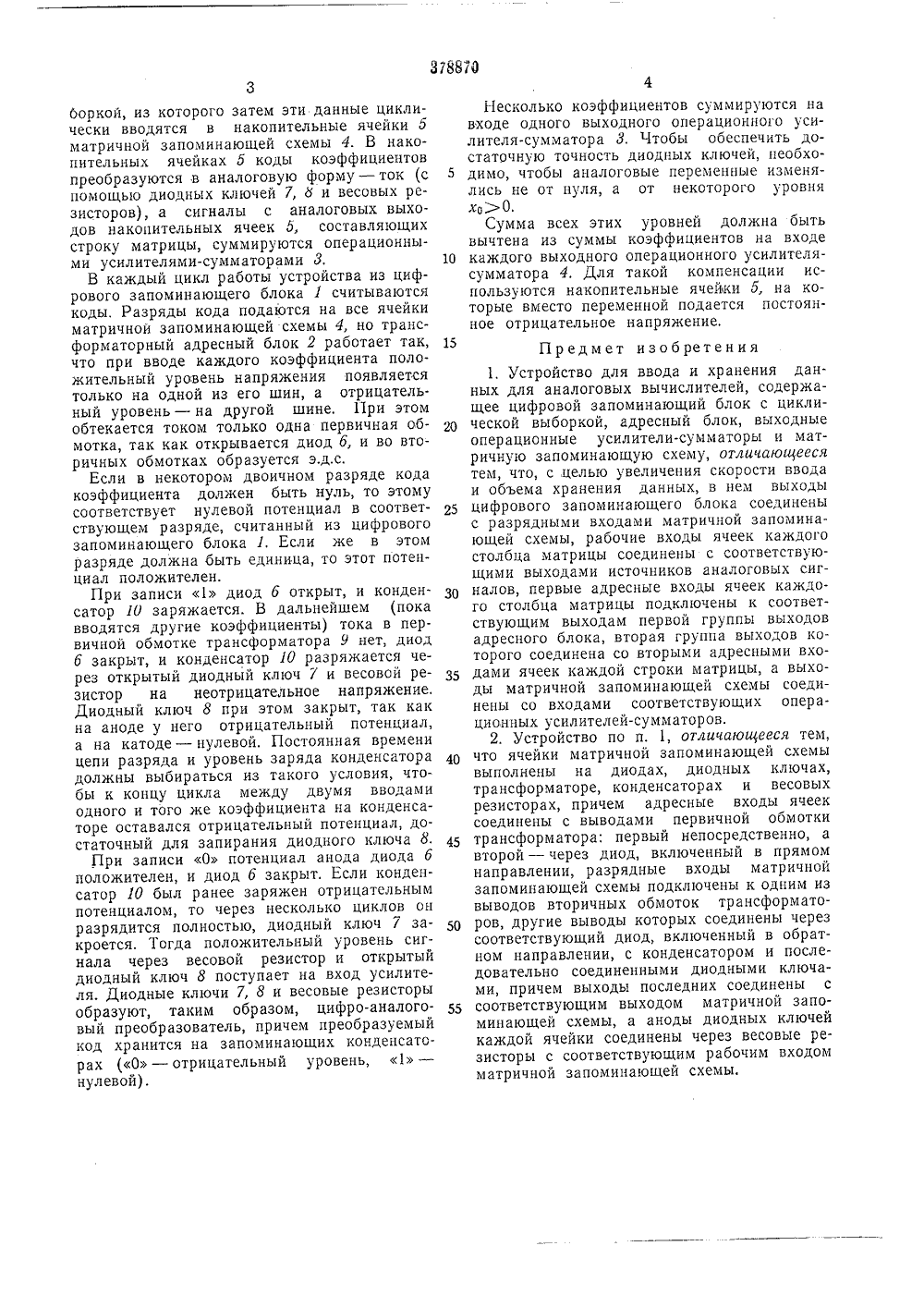

328820 Союз Советских Социалистических Реслубликприсоединением заявкириоритетпубликовано 18 17.1973, Бюллетень19ата опубликования описания 12,И 1.1973 Комитет ло делам изобретений и открытий лри Совете Министров СССРДК 681.327,2(088.8) Авторизобретен Любарский сесоюзный научно-исследовательскэлектроэнергетики вител ТРОЙСТВО ДЛЯ ВВОДА И ХРАН ДЛЯ АНАЛОГОВЫХ ВЫЧИСЛ ИЯ ДАННЬЕЛЕЙ 2 7, 8, овые Изобретение относится к вычислительной технике.Известны устройства для ввода и хранения данных для аналоговых вычислителей, содержащие цифровой запоминающий блок с циклической выборкой, адресный блок, выходные операционные усилители-сумматоры и матричную запоминающую схему.Предлагаемое устройство отличается от известных тем, что в нем выходы цифрового запоминающего блока соединены с разрядными входами матричной запоминающей схемы, рабочие входы ячеек каждого столбца матрицы соединены с соответствующими выходами источников аналоговых сигналов, первые адресные входы ячеек каждого столбца матрицы подключены к соответствующим выходам первой группы выходов адресного блока, вторая группа выходов которого соединена со вторыми адресными входами ячеек каждой строки матрицы, а выходы матричной запоминающей схемы соединены со входами соответствующих операционных усилителей-сумматоров.Это позволяет увеличить скорость ввода и объема хранения данных.Кроме того, в устройстве ячейки матричной запоминающей схемы могут быть выполнены па диодах, диодных ключах, трансформаторе, конденсаторах и весовых резисторах, причем адресные входы ячеек соединены с выводами первичной обмотки трансформатора: первый непосредственно, а второй - через диод, включенный в прямом направлении, разряд ные входы матричной запоминающей схемыподключены к одним из выводов вторичных обмоток трансформатора, другие выводы которых соединены через соответствующий диод, включенный в обратном направлении, 10 с конденсатором и последовательно соединенными диодными ключами, причем выходы последних соединены с соответствующим выходом матричной запоминающей схемы, а аноды диодных ключей каждой ячейки соеди иены через весовые резисторы с соответствующим рабочим входом матричной запоминающей схемы.На фиг. 1 изображена блок-схема предлагаемого устройства; на фиг, 2 - схема нако пительной ячейки.Устройство содержит цифровой запоминающий блок 1 с циклической выборкой, трансформаторный адресный блок 2, выходные операционные усилители-сумматоры 3 и мат ричную запоминающую схему 4 на ячейкахб, содержащих диоды б, диодные ключи трансформатор 9, конденсаторы 10 и вес резисторы.Исходные данные записываются в цифро вой запоминающий блок 1 с циклической вы10 15 20 25 30 35 40 45 50 55 Ьоркой, из которого затем эти данные циклически вводятся в накопительные ячейки 5 матричной запоминающей схемы 4. В накопительных ячейках 5 коды коэффициентов преобразуются в аналоговую форму - ток (с помощью диодных ключей 7, 8 и весовых резисторов), а сигналы с аналоговых выходов накопительных ячеек 5, составляющих строку матрицы, суммируются операционными усилителями-сумматорами 3.В каждый цикл работы устройства из цифрового запоминающего блока 1 считываются коды, Разряды кода подаются на все ячейки матричной запоминающей схемы 4, но трансформаторный адресный блок 2 работает так, что при вводе каждого коэффициента положительный уровень напряжения появляется только на одной из его шин, а отрицательный уровень - на другой шине. При этом обтекается током только одна первичная обмотка, так как открывается диод б, и во вторичных обмотках образуется э,д.с.Если в некотором двоичном разряде кодакоэффициента должен быть нуль, то этому соответствует нулевой потенциал в соответствующем разряде, считанный из цифрового запоминающего блока 1, Если же в этом разряде должна быть единица, то этот потенциал положителен.При записи 1 диод б открыт, и конденсатор 10 заряжается. В дальнейшем (пока вводятся другие коэффициенты) тока в первичной обмотке трансформатора 9 нет, диод б закрыт, и конденсатор 10 разряжается через открытый диодный ключ 7 и весовой резистор на неотрицательное напряжение, Диодный ключ 8 при этом закрыт, так как на аноде у него отрицательный потенциал, а на катоде - нулевой. Постоянная времени цепи разряда и уровень заряда конденсатора должны выбираться из такого условия, чтобы к концу цикла между двумя вводами одного и того же коэффициента на конденсаторе оставался отрицательный потенциал, достаточный для запирания диодного ключа 8.При записи 0 потенциал анода диода бположителен, и диод б закрыт. Если конденсатор 10 был ранее заряжен отрицательным потенциалом, то через несколько циклов он разрядится полностью, диодный ключ 7 закроется. Тогда положительный уровень сигнала через весовой резистор и открытый диодный ключ 8 поступает на вход усилителя. Диодные ключи 7, 8 и весовые резисторы образуют, таким образом, цифро-аналоговый преобразователь, причем преобразуемый код хранится на запоминающих конденсаторах (О - отрицательный уровень, 1 - нулевой). Несколько коэффициентов суммируются на входе одного выходного операционного усилителя-сумматора 3, Чтобы обеспечить достаточную точность диодных ключей, необходимо, чтобы аналоговые переменные изменялись не от нуля, а от некоторого уровня хо) О.Сумма всех этих уровней должна быть вычтена из суммы коэффициентов на входе каждого выходного операционного усилителя- сумматора 4. Для такой компенсации используются накопительные ячейки 5, на которые вместо переменной подается постоянное отрицательное напряжение,Предмет изобретения1, Устройство для ввода и хранения данных для аналоговых вычислителей, содержащее цифровой запоминающий блок с циклической выборкой, адресный блок, выходные операционные усилители-сумматоры и матричную запоминающую схему, отличающееся тем, что, с целью увеличения скорости ввода и объема хранения данных, в нем выходы цифрового запоминающего блока соединены с разрядными входами матричной запоминающей схемы, рабочие входы ячеек каждого столбца матрицы соединены с соответствующими выходами источников аналоговых сигналов, первые адресные входы ячеек каждого столбца матрицы подключены к соответствующим выходам первой группы выходов адресного блока, вторая группа выходов которого соединена со вторыми адресными входами ячеек каждой строки матрицы, а выходы матричной запоминающей схемы соединены со входами соответствующих операционных усилителей-сумматоров.2, Устройство по п. 1, отличающееся тем, что ячейки матричной запоминающей схемы выполнены на диодах, диодных ключах, трансформаторе, конденсаторах и весовых резисторах, причем адресные входы ячеек соединены с выводами первичной обмотки трансформатора: первый непосредственно, а второй - через диод, включенный в прямом направлении, разрядные входы матричной запоминающей схемы подключены к одним из выводов вторичных обмоток трансформаторов, другие выводы которых соединены через соответствующий диод, включенный в обратном направлении, с конденсатором и последовательно соединенными диодными ключами, причем выходы последних соединены с соответствующим выходом матричной запоминающей схемы, а аноды диодных ключей каждой ячейки соединены через весовые резисторы с соответствующим рабочим входом матричной запоминающей схемы.378870 иг. 7 Составитель Ю. Козловва Техред Л. Богданова Корректор С. Сатагуло актор 3, Твердохл Типография, пр. Сапунова аказ 1883/11 Изд.436 Тираж 647 ЦНИИПИ Комитета по делам изобретений и открытий при Совет Москва, Ж, Раушская наб., д. 4/5

СмотретьЗаявка

1671762

Всесоюзный научно исследовательский институт электроэнергетики

витель Ю. Я. Любарский

МПК / Метки

МПК: G11C 27/00

Метки: аналоговых, ввода, вычислителей, данных, хранения

Опубликовано: 01.01.1973

Код ссылки

<a href="https://patents.su/3-378870-ustrojjstvo-dlya-vvoda-i-khraneniya-dannykh-dlya-analogovykh-vychislitelejj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для ввода и хранения данных для аналоговых вычислителей</a>

Предыдущий патент: Блок регулируемого запаздывания

Следующий патент: Интегратор тока

Случайный патент: Устройство для штабелирования изделий