Программный распределитель импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 343261

Авторы: Максимов, Олейниченко, Своеступов

Текст

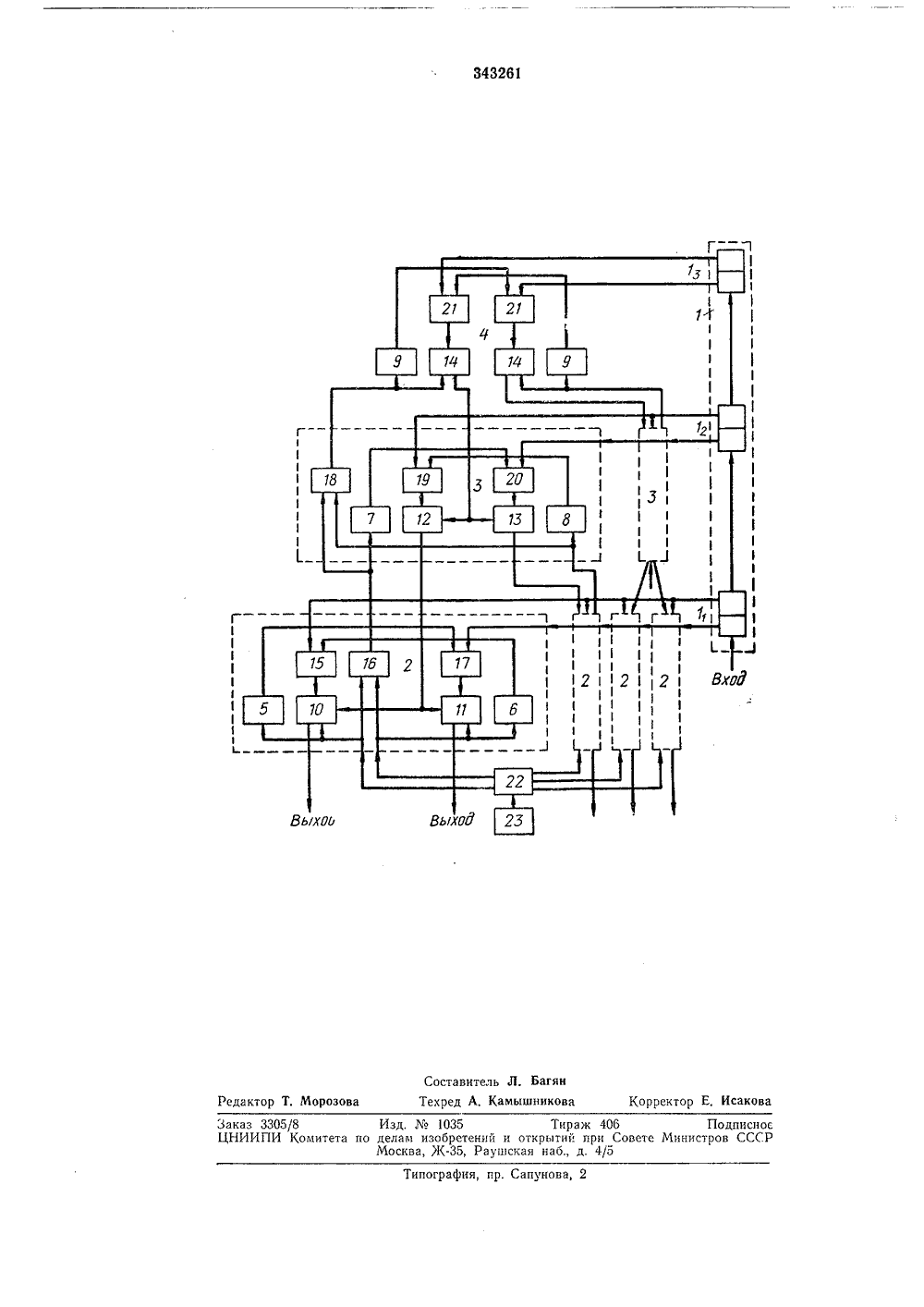

Союз Соевтскию Социалистическит РеслубликЗависимое от авт. свидетельствал. б 061 1/О явлено 26,Л.1969 ( 1341524/26 ритет Комитет оо делам аобретеиий и открытий ори Совете Мкиистров СССР. Максим Заявител ОГРАММНЫЙ РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ области тел ано в комм ельной и из им- чен- ежс присоединением заявкиИзобретение относится к еь рии и может быть использов ти ющих устройствах вычислит мертельной техники.Известны программные распределители 5 пульсов, содержащие счетчик и подклю ные к нему логические ячейки, связанные м ду собой по пиромидальной схеме,Однако в известных устройствах длительность выходных импульсов заранее определя ется схемой и может быть изменена только способом смены частоты следования входных импульсов.С целью управления длительностью выходных импульсов при постоянной частоте их 15 следования в предлагаемом устройстве логические ячейки выполнены на логических схемах НЕ, ИЛИ и И, причем каждая из схем НЕ, включенных на двух входах логической ячейки, подключена своим выходом ко 20 входу ИЛИ, на другой вход которой подключен выход прямого (обратного) кода соответствующего разряда счетчика, выходы обеих схем ИЛИ подключены ко входам двух схем И, другие входы которых объе динены и соединены с выходом одной из схем И логической ячейки предыдущей ступени пирамиды, кроме того, входы каждой логической ячейки объединены другой схемой ИЛИ, выход которой подключен к анало- З 0 гичному входу логической ячейки предыдущей ступени пирамиды, а ко входам логических ячеек, образующих основание пирамиды, под. ключены выходы блока программ.На чертеже представлена функциональная блок-схема предлагаемого устройства.Устройство содержит счетчик 1 на триггерах 1 - 1 з, к которому подключены логические ячейки 2 - 4, связанные между собой по пирамидальной схеме и содержащие логические схемы НЕ 5 - 9, схемы И 10 - 14 и схемы ИЛИ 15 - 21. Блок программ, включающий ячейки памяти 22 и подключенный к ним распределитель импульсов 23, соединен непосредственно со схемами логической ячейки 2 (первая ступень пирамидальной схемы) и через схемы ИЛИ 1 б и 18 - с остальными ступенями пирамидальной схемы.При возникновении на всех выходах устройства импульсов одинаковой длительности с ячейки памяти 22 блока программ подан высокий потенциал на схемы НЕ 5 и б, схемы И 10 и 11 и схему ИЛИ 15 всех ячеек 2 первой ступени, а также на схемы НЕ 7 и 8 и схему ИЛИ 18 всех ячеек 3 второй ступени и на схему НЕ 9 и схему И 14 ячейки 4 третьей ступени, На логические схемы второй и третьей ступени высокий потенциал подается через соответствующие схемы ИЛИ 1 б и 18. В результате действия высо5 1 О 15 го г 5 зо 35 40 45 кого потенциала схемы И 10, 11 и 14 по одному из входов этих схем закрыт. На выходе схем НЕ 5 - 9 образуется низкий потенциал, который обеспечивает управление работой схем И по входам пирамидальной схемы, связанным с соответствующими выходами триггеров 1, - 1,. Схема И 14 управляется по входу, связанному с выходами триггера 1 З, а схема И 12 и 13 управляется одновременно по входу, связанному с выходами триггера 1, через схемы ИЛИ 19 и 20 соответственно, и по входу, связанному с выходами триггера 1 З через схему И 14, Аналогично управляется схема И 10 и 11 по входам пирамидальной схемы, соединенным с выходами триггеров 1 - 1.На выходах схем И ячеек 2 первой ступени возникают импульсы, разделенные во времени и в пространстве и определяемые совпадением высоких потенциалов по всем трем входам, соединенным с выходами триггеров 1 - 1 з счетчика 1.Для изменения длительности импульсов, получаемых на одном или нескольких выходах схем И 10 и 11, используется блок программ. При увеличении длительности импульса, возникающего на выходе схемы И 11, на схему НЕ Б, схему И 10 и схему ИЛИ 1 б первой ячейки 2 первой ступени подают низкий потенциал, а на схему НЕ б, схему И 11 и схему ИЛИ 1 б - высокий потенциал, при этом изменяется работа только в первой ячейки 2 первой ступени. Во всех остальных ячейках работа схемы проходит аналогично описанной выше. В первой ячейке 2 на выходе схемы И 10 импульсы не возникают, так как один из ее входов всегда находится под низким потенциалом, На входе схемы НЕ б образуется высокий потенциал, который действует через схему ИЛИ 17 на схему И 11 постоянно, независимо от потенциала с выхода триггера 11, Работа схемы И 11 определяется сигналами, поступающими с выхода схемы И 12, которая управляется потенциалами с триггеров 12 и 1 з, Так как длительность импульсов, поступающих на вход, связанный с триггером 1 ь отличается от длительности импульсов, поступающих на вход, связанный с триггером 1 то на выходе схемы И 11 возникают импульсы шире, чем импульсы на других выходах устройства. Частота повторения импульсов останется без изменений. Расширение длительности импульсов с выхода схемы И 11 происходит за счст выключения соседней схемы И 10.Таким образом, задавая определенную программу, можно изменять частоту следования импульсов, отключить те или иные схемы И, изменять длительность выходных импульсов при постоянной частоте их следования и менять порядок возникновения импульсов по входам. Предмет изобре гения Программный распределитель импульсов, содержащий счетчик и подключенные к нему логические ячейки, связанные между собой по пирамидальной схеме, отличающийся тем, что, с целью управления длительностью выходных импульсов при постоянной частоте их следования, логические ячейки выполнены на логических схемах НЕ, ИЛИ и И, причем каждая из схем НЕ, включенных на двух входах логической ячейки, подключена своим выходом ко входу схемы ИЛИ, на другой вход которой подключен выход прямого (обратного) кода соответствующего разряда счетчика, выходы обеих схем ИЛИ подключены ко входам двух схем И, другие входы которых объединены и соединены с выходом одной из схем И логической ячейки предыдущей ступени пирамиды, кроме того, входы каждой логической ячейки объединены другой схемой ИЛИ, выход которой подключен к аналогичному входу логической ячейки предыдущей ступени пирамиды, а ко входам логических ячеек, образующих основание пирамиды, подключены выходы блока программ.343261Составитель Л. Багяи Реда , Морозов хред А. Камышниковрректор Е, Исако каз 3305/8 Изд,1035 Тираж 406 Подписи ос НИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР Москва, Ж, Раушская наб., д. 4/5Типография, пр. Сапунова

СмотретьЗаявка

1341524

С. С. Своеступов, А. К. Олейниченко, Л. В. Максимов

МПК / Метки

МПК: G06F 1/04

Метки: импульсов, программный, распределитель

Опубликовано: 01.01.1972

Код ссылки

<a href="https://patents.su/3-343261-programmnyjj-raspredelitel-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Программный распределитель импульсов</a>

Предыдущий патент: 343260

Следующий патент: Многоканальный коммутатор знакопеременныхсигналов

Случайный патент: Устройство для выделения подвижных объектов на неподвижном фоне