Аналого-цифровой преобразовательbrirrf. ocitj и а и» f “. s i. ii.; -: ; •; -“-j; ixj4-,

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 332567

Автор: Махнанов

Текст

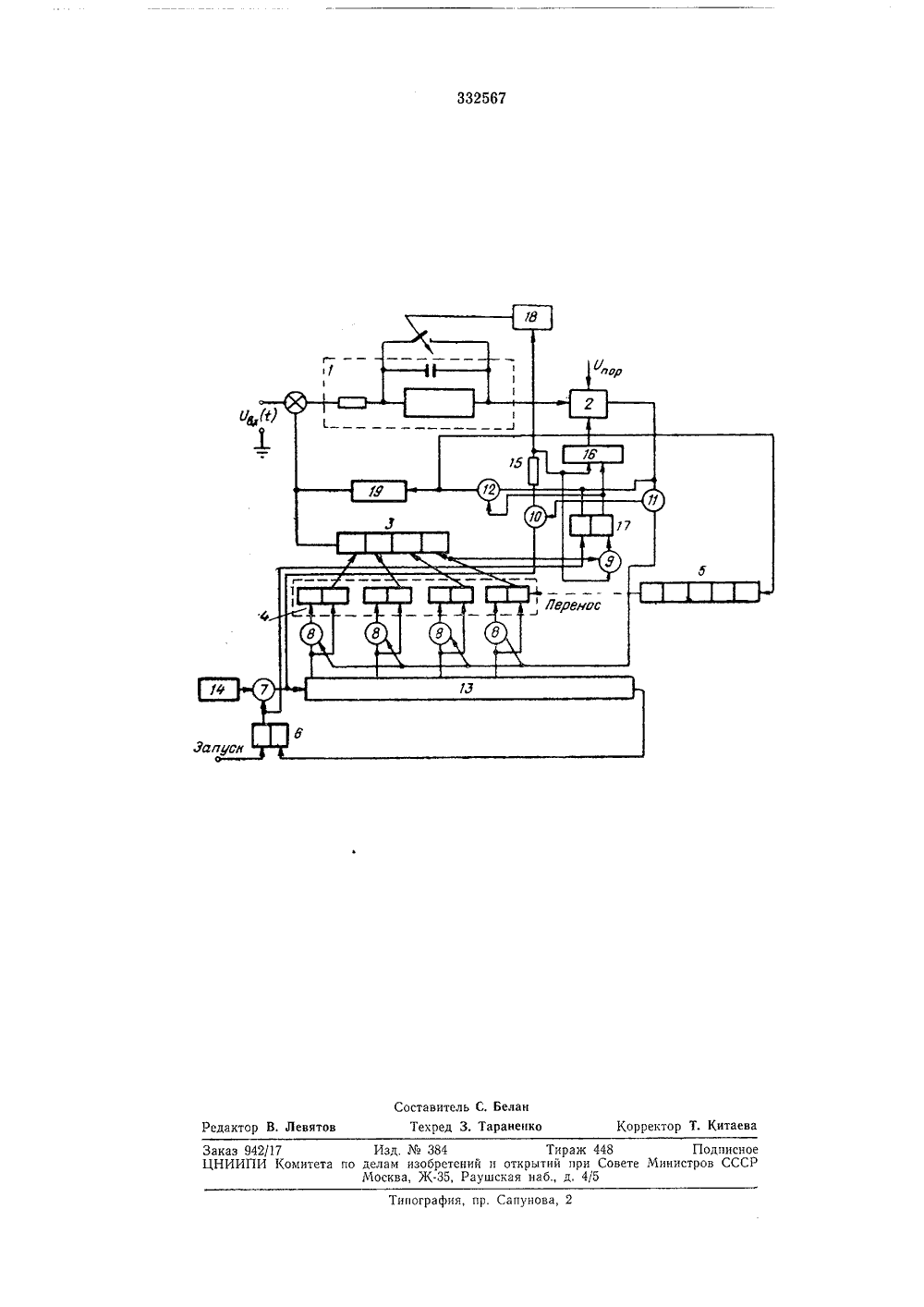

О П И СА Н И Е ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВЙДЕТЕЛЬСТВУ 332567 Союэ Советских Социалистических РеспубликЗависимое от авт. свидетельства-Заявлено 31,Ч 111.1970 ( 1472406/18-24)с присоединением заявкиМ, 1 л. Н 031 с 13/02 Комитет по делам иэобретевий и открытий при Совете Мивистрое СССРПриоритетОпубликованоДата опублик К 681.325(088.8) 4,111,1972. Бюллетень10ання описания 15.1 Ч.1972 Авторизобретени Д. Махнанов Заявител АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛ Изобретение относится к аналого-цифровым преобразователям и может быть использовано в области автоматики и вычислительной техники.Известны аналого-цифровые преобразователи с промежуточным преобразованием аналоговой величины в частоту следования импульсов, основанные на интегрировании аналоговой величины с последующим сравнением с пороговой и формированием импульсов обратной связи постоянной вольт-секундной площади, возвращающим интегратор в исходное состояние.Недостатком известных устройств является малая точность и быстродействие.Целью изобретения является повышение точности и быстродействия устройства.Для достижения цели в устройство введены линия задержки, схема ИЛИ, дополнительные вентили и триггер.На чертеже изображена блок-схема предложенного преобразователя.Устройство содержит интегратор 1, сравнивающее устройство 2, преобразователь кода в напряжение 3, старшие 4 разряды и младшие б разряды выходного регистра, триггер 6, вентили 7 - 12, распределитель И, генератор такговых импульсов 14, линию задержки 15, схему ИЛИ 16, триггер 17, одновибратор 18, узел обратной связи 19. 2Устройство работает следующим образом.По команде Запуск с помощью триггераб открывается вентиль 7, через который на распределительное устройство 13 от генерато ра тактовых импульсов 14 начинают поступать импульсы. Распределитель формируе г последовательность тактов работы преобразователя. В первом такте в преобразователе 8 включена старшая компенсирующая аналоговая величина У,= - У.х ., Проинтегриро 1к - 2 актахванная блоком 1 разность преобразуемого и компенсирующего напряжений поступает на сравнивающее устройство 2. Через время, 15 определяемое линией задержки 15, но цепи:вентиль 10, линия задержки 16, схема ИЛИ 16 - очередной тактовый импульс (в данном случае первый) поступает на сравнивающее устройство 2, производят импульсный опрос 20 этого устройства. Если проинтегрированнаяразность к этому моменту меньше пороговой величины У,р, поданной на другой вход сравнивающего устройства 2, производится выключение триггера старшего разряда (че рез открытый триггером вентиль 11 и вентиль8 старшего разряда регистра 4). Если проннтегрированная разность больше пороговой величины, первое компенсирующее напряжение остается включенным.30 После импульсного опроса производитсяустановка интегратора в исходное состояние с помощью одновибратора 18, время выдержки (длительность генерируемого одновибратором импульса) должно быть достаточным, чтобы переходные процессы в интеграторе установились до начала следующфего такта работы устройства, после чего вторым тактовым импульсом включается компенсирующее напряжение, соответствующее следующему разряду преобразователя 3, Через время т в результате импульсного опроса определяется второй разряд и т. д.При включении последнего разряда регистра 4 (последнего из старших разрядов, количество которых выбирается в зависимости от величины допустимой, известной в априоре амплитуды помехи и может подбираться непосредственно перед измерением очередного входного сигнала) открывается вентиль 10. Однако из-за задержки во времени установки распределителя в этом такте импульс через еще незакрытый вентиль 10 поступает на линию задержки и через время т производит опрос сравнивающего устройства 2. В зависимости от сигнала сравнивающего устройства производится выключение соответствующего этому разряду компенсирующего напряжения либо оно остается включенным, Этот же импульс опроса через открытый к этому времени вентиль 9 переключает триггер 17, выходным сигналом которого закрывает вентили 10 и 11 и открывает вентиль 12. Одновременно сигналом триггера 17 через схему ИЛИ 1 б сравнивающее устройство 2 переводится в режим непрерывной работы, после чего проинтегрированная блоком 1 разность между преобразуемым и суммой компенсирующих напряжений включенных разрядов преобразователя 3 сравнивается с пороговым напряжением, и в момент равенства сравнивающим устройством 2 вырабатывается импульс, который через открытый вентиль 12 запускает узел 19, формирующий импульсы эталонной вольт-секундной площади, и поступает на владшие разряды б выходного регистра. Распределитель 13 вместе с генератором тактовых импульсов 14, вентилем 7 и триггером б в этом случае служит как временной задат. чик в известных преобразователях напряжения в частоту следования импульсов 1, а именно для задания интервала измерения Т,. Через время Т, триггер б возвращается в исходное состояние, вентиль 7 закрывается, 5 10 процесс преобразования заканчивается.В предлагаемом преобразователе за счет того, что преобразователем напряжения в частоту следования импульсов преобразуется только часть входного напряжения уменьшаются требования к точности, а также снижается верхний предел по выходной частоте, значительно упрощается сам интегратор и сравнивающее устройство с узлом обратной связи,Предмет изобретени яАналого-цифровой преобразователь, содер жащий интегратор, выход которого подключенко входу сравнивающего устройства, узел обратной связи, преобразователь код - напряжение, выходной регистр, генератор тактовых импульсов, подключенный через вентиль к 20 распределителю, триггеры, вентили, одновибратор, отличающийся тем, что, с целью повышения точности в него введены линия за.- держки, схема ИЛИ, дополнительные вентили и триггер, причем выходы распредели теля через вентили подключены к входамтриггеров старших разрядов выходного регистра, управляющих преобразователем коднапряжение, выход которого соединен с выходом узла обратной связи, выход последнего З 0 триггера старших разрядов выходного регистра через первый дополнительный вентиль подключен ко входу дополнительного тригге.ра, второй выход последнего триггера старшего разряда выходного регистра подключен З 5 к первому входу второго дополнительноговентиля, второй вход которого соединен со входом распределителя, третий вход с одним выходом дополнительного триггера и управляющим входом вентиля, включенного между 40 выходом сравнивающего устройства и вентилями, управляющими триггерами старших разрядов выходного регистра, выход второго дополнительного вентиля через линию задержки соединен со входом запуска одновибрато ра, с другим входом первого дополнительноговентиля и с одним входом схемы ИЛИ, другой вход которой подключен к другому выходу дополнительного триггера и к управляющему входу вентиля, включенного между 50 входом узла обратной связи и выходом сравнивающего устройства, выход схемы ИЛИ. соединен со входом опроса сравнивающего устройства.332567Составитель С. Белан Редактор В. Левитов Техред 3. ТараненкоКорректор Т. Китаева Заказ 942/17 Изд. Мо 384 Тираж 448 Подписное ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР Москва, Я(-35, Раушская наб., д. 4/5Типография, пр. Сапунова, 2

СмотретьЗаявка

1472406

В. Д. Махнанов

МПК / Метки

МПК: H03M 1/60

Метки: ixj4, ocitj, »j—, аналого-цифровой, преобразовательbrirrf

Опубликовано: 01.01.1972

Код ссылки

<a href="https://patents.su/3-332567-analogo-cifrovojj-preobrazovatelbrirrf-ocitj-i-a-i-f-s-i-ii-j-ixj4.html" target="_blank" rel="follow" title="База патентов СССР">Аналого-цифровой преобразовательbrirrf. ocitj и а и» f “. s i. ii.; -: ; •; -“-j; ixj4-,</a>

Предыдущий патент: Двухпороговое устройство

Следующий патент: Устройство для корректировки декодирующейматрицы

Случайный патент: Устройство для управления независимым инвертором