Дискриминатор-формирователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 330533

Автор: Сдатчиков

Текст

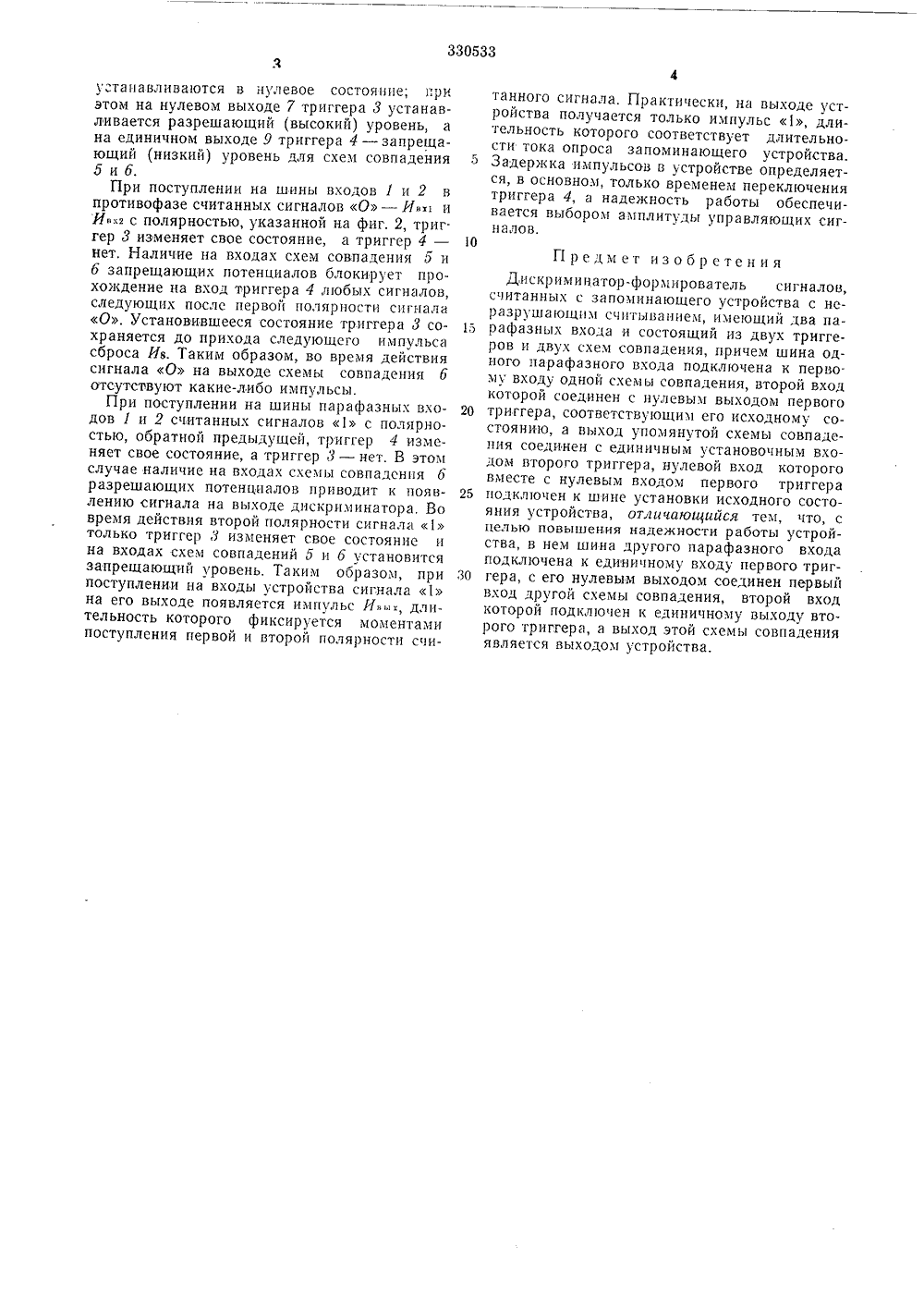

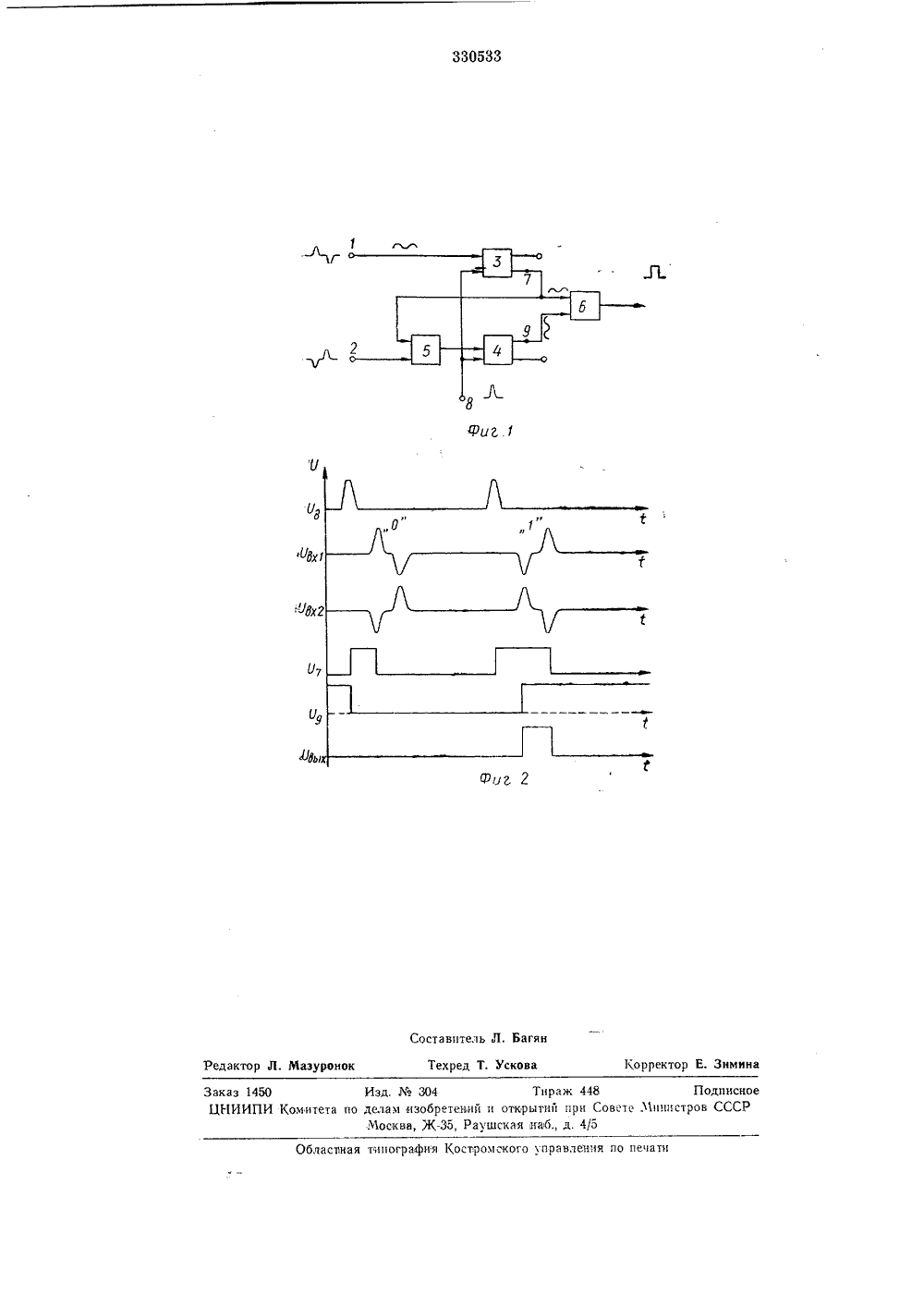

ОП ИСАН ИЕИЗОЫ ЧТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Соввтскив Социалистичвскив Республикки Ло присоединением за Комитет по делам аосретений н открыти орн Совете Министров СССРите ри Опубликовано 241 ень х"е 8 УДК 621.374.33 (088,8 2. Бюлл Дата опубликования описания 2.1972 тор В, Сдатчико изобретения тОСА вит ДИСКРИМИНАТОР-ФОРМИРОВАТЕЛЪ рафазного входа подключается к единичному входу первого триггера, с его нулевым выходом соединяется первый вход другой схемы совпадения, второй вход которой подключает ся к единичному выходу второго триггера, авыход этой схемы совпадения является выходом устроиства.На фиг. 1 представлена функциональнаяблок-схема предложенного устройства; на фиг.10 2 - временная диаграмма его работы.Устройство содержит два парафазных входа1 и 2, два триггера 3 и 4 (например, на транзисторах) и две схемы совпадения 5 и 6 (схемы сИ). Шина парафазного входа 2 под ключена к первому входу схемы совпадения5, второй вход которой соединен с нулевым выходом 7 триггера 3. Выход схемы совпадения 5 соединен с единичным установочным входом триггера 4, нулевой вход которого 20 вместе с нулевым входом триггера 3 подключен к шине 8 установки исходного состояния устройства. Шина парафазного входа 1 подключена к единичному входу триггера 3, с нулевым выходом 7 которого соединен первый 25 вход схемы совпадения 6, второй вход которой подключен к единичному выходу 9 триггера 4, а выход схемы совпадения 6 является выходом устройства.Первоначально п30 са Ие, подаваемого Изобретение относится к области вычислительной и дискретной техники, в частности, к устройствам для автоматической селекции и формирования считанных сигналов запоминающих устройств с неразрушающим считыванием, выходные сигналы которых различаются фазами полярностей,Известен дискриминатор-формирователь сигналов, считанных с запоминающего устройства с неразрушающим считыванием, имеющий два парафазных входа и состоящий из двух триггеров и двух схем совпадения, причем шина одного парафазного входа подключена к первому входу одной схемы совпадения, второй вход которой соединен с нулевым выходом первого триггера, соответствующим его исходному состоянию, а выход упомянутой схемы совпадения соединен с единичным установочным входом второго триггера, нулевой вход которого вместе с нулевым входом первого триггера подключен к шине установки исходного состояния устройства,Однако известное устройство требует формирования выходных импульсов по длительности и амплитуде, а изменение питающих напряжений и амплитуд входных сигналов влияет на работоспособность устройства.Цель изобретения - повышение надежности работы устройства.Достигают этого тем, что шина другого пари помощи импульса сброна шину 8, триггеры 3 и 4устанавливаются в нулевое состояние; при этом на нулевом выходе 7 триггера 3 устанавливается разрешающий (высокий) уровень, а на единичном выходе 9 триггера 4 - запрещающий (низкий) уровень для схем совпадения 5 и б.При поступлении на шины входов 1 и 2 в противофазе считанных сигналов О - И.г и И": с полярностью, указанной на фиг, 2, триггер 3 изменяет свое состояние, а триггер 4 - нет. Наличие на входах схем совпадения 5 и 6 запрещающих потенциалов блокирует прохождение на вход триггера 4 любых сигналов, следующих после первой полярности сигнала О. Установившееся состояние триггера 3 сохраняется до прихода следующего импульса сброса Ив. Таким образом, во время действия сигнала О на выходе схемы совпадения б отсутствуют какие-либо импульсы.При поступлении на шины парафазных входов 1 и 2 считанных сигналов 1 с полярностью, обратной предыдущей, триггер 4 изменяет свое состояние, а триггер 3 - нет, В этом случае наличие на входах схемы совпадения 6 разрешающих потенциалов приводит к появлению сигнала на выходе дискриминатора, Во время действия второй полярности сигнала 1 только триггер 3 изменяет свое состояние и на входах схем совпадений 5 и 6 установится запрещающий уровень. Таким образом, при поступлении на входы устройства сигнала 1 на его выходе появляется импульс Ив, х, длительность которого фиксируется моментами поступления первой и второй полярности считанного сигнала. Практически, на выходе устройства получается только импульс 1, длительность которого соответствует длительности тока опроса запоминающего устройства.Задержка импульсов в устройстве определяется, в основном, только временем переключения триггера 4, а надежность работы обеспечивается выбором амплитуды управляющих сигналов.1 ОПредмет изобретенияДискриминатор-формирователь сигналов,считанных с запоминающего устройства с не- разрушающим считыванием, имеющий два па рафазных входа и состоящий из двух триггеров и двух схем совпадения, причем шина одного парафазного входа подключена к первому входу одной схемы совпадения, второй вход которой соединен с нулевым выходом первого 20 триггера, соответствующим его исходному состоянию, а выход упомянутой схемы совпадения соединен с единичным установочным входом второго триггера, нулевой вход которого вместе с нулевым входом первого триггера 25 подключен к шине установки исходного состояния устройства, отличающийся тем, что, с целью повышения надежности работы устройства, в нем шина другого парафазного входа подключена к единичному входу первого триг гера, с его нулевым выходом соединен первьшвход другой схемы совпадения, второй вход которой подключен к единичному выходу второго триггера, а выход этой схемы совпадения является выходом устройства.330533 г Йь 2 Составитель Л, Багя Редактор Л, Мазуронок Техред Т. Ускова корректор Е. Зимин Заказ 1450ЦНИИП Изд.304 Тираж 448 митета по делам изобретений ц открытий при Совете Мищ Москва, Ж, Раушская наб., д. 4/5Обдаспная типография Костромского управления по печати Подписиров СССР

СмотретьЗаявка

1610548

Н. В. Сдатчиков

МПК / Метки

МПК: G11C 11/00, H03K 5/01

Метки: дискриминатор-формирователь

Опубликовано: 01.01.1972

Код ссылки

<a href="https://patents.su/3-330533-diskriminator-formirovatel.html" target="_blank" rel="follow" title="База патентов СССР">Дискриминатор-формирователь</a>

Предыдущий патент: Смеситель импульсных сигналов

Следующий патент: Формирователь импульсов

Случайный патент: Способ исследования деформации при обработке металлов давлением