Преобразователь временных интервалов в параллельный двоичный код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 326730

Автор: Русаков

Текст

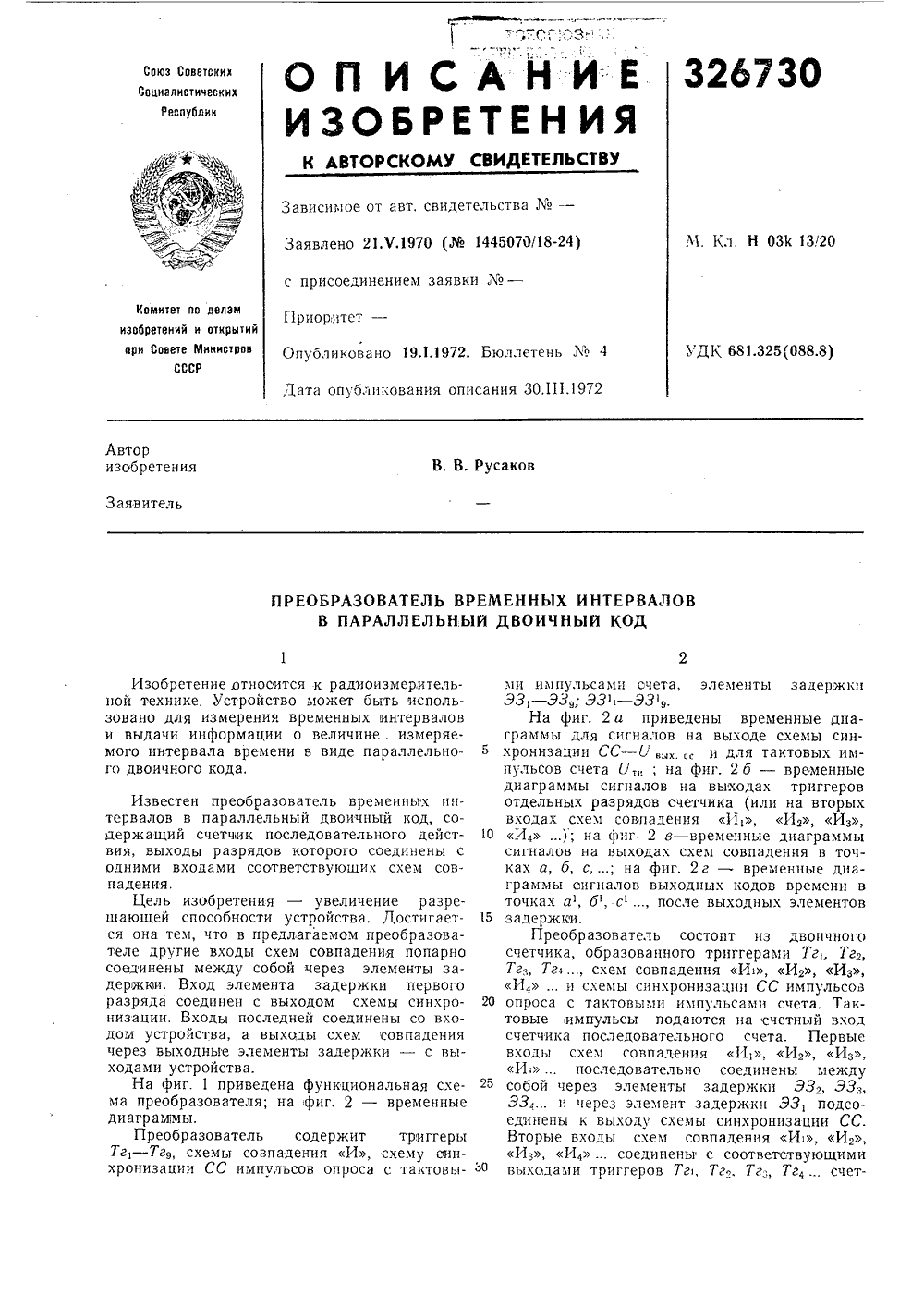

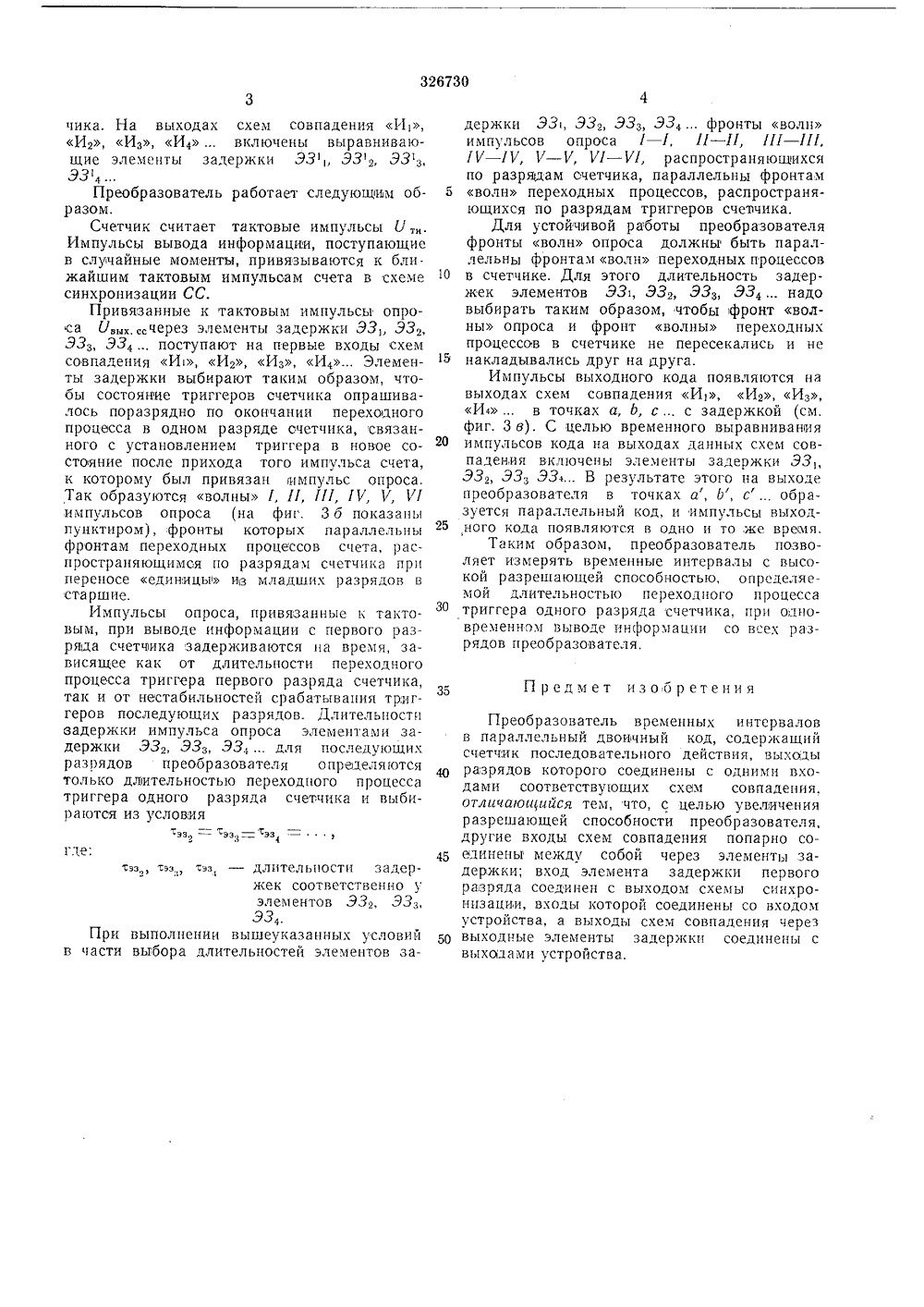

Гс аеЛ " Р;, 1 -.,,ОП ИСАНИ ЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 326730 Союз Советских Социалистических республик.Ч, Кл, Н 031 13/20 Номитет по делам изобретений и открытий при Совете Министров СССРх ДЬ, 681 325(088 8) Авторизобретения В, В, Русаков Заявитель ПРЕОБРАЗОВАТЕЛЪ ВРЕМЕННЫХ ИНТЕРВАЛОВ В ПАРАЛЛЕЛЪНЫЙ ДВОИЧНЫЙ КОДИзобретение относится к радиоизмерительцой технике, Устройство может быть использовано для измерения временных интервалов и выдачи информации о величине. измеряемого интервала времени в виде параллельного двоичного кода. Известен преобразователь времеццьнх интервалов в параллельный двоичный код, содержащий счетчик последовательного действия, выходы разрядов которого соединены с одними входами соответствующих схем совпадения,Цель изобретения - увеличение разрешающей способности устройства, Достигается она тем, что в предлагаемом преобразователе другие входы схем совпадения попарно соединены между собой через элементы задержтаи. Вход элемента задержки первого разряда соединен с выходом схемы синхронизации. Входы последней соединены со входом устройства, а выходы схем совпадения через выходные элементы задержки - с выходами устройства.На фиг. 1 приведена функциональная схема преобразователя; на фиг. 2 - временные диаграммы.Преобразователь содержит триггеры Тг, - Тг схемы совпадения И, схему синхронизации СС импульсов опроса с тактовыми импульсами счета, элементы задероккп ЭЗ, ЭЗ ЭЗт ЭЗ,.На фиг, 2 а приведены временные диаграммы для сигналов на выходе схемы син хронизации СС - С, и для тактовых импульсов счета У; на фиг. 2 б - временные диаграммы сигналов на выходах триггеров отдельных разрядов счетчика (или на вторых входах схем совпадения И 1, Из, Из, 10 И 4 ); на фиг 2 в - временные диаграммысигналов на выходах схем совпадения в точках а, б, с, ; на фиг. 2 г - временные диаграммы сигналов выходных кодов времени в точках а, б, с , после выходных элементов 15 задержки.Преобразователь состоит из двоичногосчетчика, образованного триггерами Тгь Тг Тгз, Тг 4 , схем совпадения И 1, Из, Из, И 4и схемы синхронизации СС импульсов 20 опроса с тактовыми импульсами счета, Тактовые,импульсы подаются ца счетный вход счетчика последовательного счета. Первые входы схем совпадения И И 2, Из, И 4 .последовательно соединены между собой через элементы задержки ЭЗ., ЭЗз, ЭЗл и через элемент задержки ЭЗ, подсоединены к выходу схемы синхронизации СС.Вторые входы схем совпадения И 1, И 2, Из, И,соединены с соответствующими выходами триггеров Тгц Тгз, Тг.; Тг 4счетчика. На выходах схем совпадения И 1, И И, И 4включены выравнивающие элементы задержки ЭЗ ЭЗ ЭЗг,4Преобразователь работает следующим образомм.Счетчик считает тактовые импульсы УУ,. Импульсы вывода информации, поступающие в случайные моменты, привязываются к бли. жайшим тактовым импульсам счета в схеме синхронизации СС.Привязанные к тактовым импульсы опроса Оэ,через элементы задержки ЭЗ ЭЗ ЭЗз, Э 34поступают на первые входы схем совпадения И, Иг, Из, И 4 Элементы задержки выбирают таким образом, чтобы состояние триггеров счетчика опрашивалось поразрядно по окончании переходного процесса в одном разряде счетчика, связанного с установлением триггера в новое состояние после прихода того импульса счета, к которому был привязан импульс опроса, Так образуются волны 1, УУ, ПУ, УЬ, 1, Л импульсов опроса (на фиг. 3 б показаны пунктиром), фронты которых параллельны фронтам переходных процессов счета, распространяющимся по разрядам счетчика при переносе единицы из младших разрядов в старшие.Импульсы опроса, привязанные к тактовым, при выводе информации с первого разряда счетчика задерживаются иа время, зависящее как от длительности переходного процесса триггера первого разряда счетчика, так и от нестабильностей срабатывания триггеров последующих разрядов. Длительности задержки импульса опроса элементами задержки ЭЗг, ЭЗз, Э 34для последующих разрядов преобразователя определяются только длительностью переходного процесса триггера одного разряда счетчика и выбираются из условия баэз эз баэз, - длительности задержек соответственно у элементов ЭЗг, ЭЗ Э 34При выполнении вышеуказанных условий в части выбора длительностей элементов за 5 10 Б 20 25 Зо держки ЭЗь ЭЗг, ЭЗз, Э 34" фронты волн импульсов опроса 1 - 1, П - П, П 1 - 1 П, УР - УГ, 1 - Р, К - Я, распространяющихся по разрядам счетчика, параллельны фронтам волн переходных процессов, распространяющихся по разрядам триггеров счевчика.Для устойчивой работы преобразователя фронты волн опроса должны быть параллельны фронтам волн переходных процессов в счетчике. Для этого длительность задержек элементов ЭЗ, ЭЗг, ЭЗ Э 34надо выбирать таким образом, чтобы фронт волны опроса и фронт волны переходных процессов в счетчике не пересекались и не накладывались друг на друга.Импульсы выходного кода появляются на выходах схем совпадения И, Иг, И И 4в точках а, 6, сс задержкой (см. фиг. 3 в). С целью временного выравнивания импульсов кода на выходах данных схем совпадения включены элементы задержки ЭЗ ЭЗ ЭЗ, ЭЗэ В результате этого на выходе преобразователя в точках а, 6, с , образуется параллельный код, и импульсы выходного кода появляются в одно и то,же время.Таким образом, преобразователь позволяет измерять временные интервалы с высокой разрешающей способностью, определяемой длительностью переходного процесса триггера одного разряда счетчика, при одновременном выводе информации со всех разрядов преобразователя. Предмет изобретения Преобразователь временных интервалов в параллельный двоичный код, содержащий счетчик последовательного действия, выходы разрядов которого соединены с одними входами соответствующих схем совпадения, отличающийся тем, что, с целью увеличения разрешающей способности преобразователя, другие входы схем совпадения попарно соединены между собой через элементы задержки; вход элемента задержки первого разряда соединен с выходом схемы синхронизации, входы которой соединены со входом устройства, а выходы схем совпадения через выходные элементы задержки соединены с выходами устройства.326730 Т(Вьипйпя ои и Ц 1 ХУ 5 р 5 р Составитель М. ЧеренковаБ. Федотов Техред Е. Борисова Корректор А. Василь едак каз 53/270 Изд.88 Тираж 448 ПодписноеНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР Москва, Ж, Раушская наб., д, 4/5 и, Харьк, фил. поет, Патет 1 р 2 р ГЦ ГД7 7 акт 1 ыР имГупьсь СЮ 7 й 7

СмотретьЗаявка

1445070

В. В. Русаков

МПК / Метки

МПК: G04F 10/04, H03M 1/50

Метки: временных, двоичный, интервалов, код, параллельный

Опубликовано: 01.01.1972

Код ссылки

<a href="https://patents.su/3-326730-preobrazovatel-vremennykh-intervalov-v-parallelnyjj-dvoichnyjj-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь временных интервалов в параллельный двоичный код</a>

Предыдущий патент: Кодирующий преобразователь

Следующий патент: Устройство для управления транзисторным переключателем

Случайный патент: Приспособление для уминания волокнистой ленты при наработке ее в таз, например, на чесальных машинах для льна