Устройство для двухпредельного сравнения п-разрядных двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 238889

Автор: Бурмака

Текст

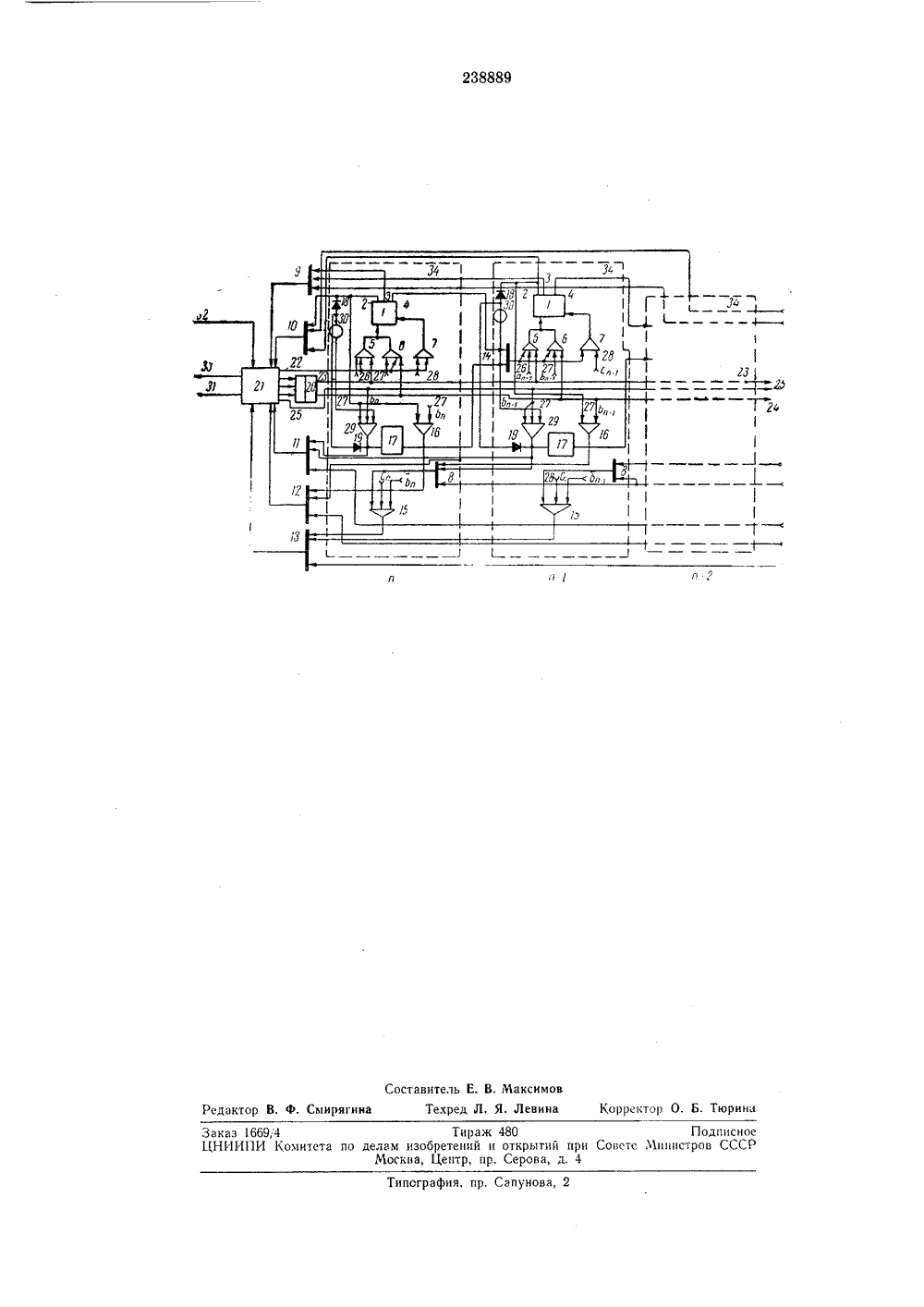

биолиО 1 еьаи)Р О П И С А Н И Е 238889ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советски СоциалистическиРеспублик Зависимое от авт. свидетельства ЛЪ Заявлено 24.И 1.1967 ( 1176455/18-24) 1 л. 42 ш", 7/38 с присоединением заявки Ъ ПриоритетОпубликовано 10.111.1969. Бюллетень Ъо 10 Дата опубликования описания 18 ХП.19 б 9,ЧП 1 6 061ДК 681 325 66(088 8) Комитет по делам изобретений и открытий при Совете Министров СССРАвторизобретения А, А, Бурмака Заявитель УСТРОЙСТВО ДЛЯ ДВУХПГЕДЕЛЬНОГО СРАВНЕНИЯ л-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛПредложенное устройство относится к области вычислительной техники,Известны устройства двухпредельного сравнения чисел, содержащие схемы сравнения, логические схемы, шины ввода чисел, шины опроса, анализаторы, схемы ввода и вывода чисел, запоминающие устройства.Предлагаемое устройство отличается от известных тем, что в нем выходы вентилей ввода чисел верхнего и нижнего пределов сравнения объединены, выходы шин разрешения верхнего и нижнего пределов подключены к противоположным выходам управляющего триггера, а выходы поразрядных шин больше схем сравнения соединены с собирательными схемами первой группы, с первыми входами вторых вентилей поразрядного сравнения, вторые входы которых соединены с шиной ввода числа нижнего предела. Кроме того, эти же шины схем сравнения через диоды и инверторы подключены к первым входам схем ИЛИ-НЕ, выходы которых через интегрирующие цепочки, собирательные схемы подключены к шинам опроса вентилей ввода младших разрядов чисел и через диоды соединены со входами инверторов.Это позволяет повысить быстродействие устройства,На чертеже изображена схема предлагаемого усгройства. Она содержцпг логические семы сравнения1 разрядов двух двоичных чисел, включающие зыходы поразрядных шцц больше 2, меньше 3, равно 1; вентили ввода чисел 5 5 - 7, собирательные семы 8; первую 9, 10 цвторую 11 - 13 группу собирательных схем, третью группу собирательных сем 14; первые 15 и вторые 16 вентили поразрядного сравнения, интегрирующие цепочки 17, диоды 10 18, 19; управляющци триггер 20, анализатор21, шины 22 опроса вентиля ввода разрядов шсел, шины разрешения гвода чисел вер- нцй предел 2,у и нижний предел 21, шину установки нуля 2 о, шины параллельного 15 ввода чисел верхний предел 26, нижнийпредел 27 и сравниваемое число 28 в логические схемы поразрядного сравнения, схемы ИЛИ-НЕ 29, цнверторы 30, шины команд не совпало Л, сравнивай 32, соьцало 20 Зд, логический узел 31.Устройство работает следующим образом.По команде сравнцвай, поступающей пошцнс:12, анализатор 21 формирует сш нал опроса, который опрашивает входные ьентцлц 25 ввода 5 - 7 и-ны разрядов (где и - номе,старшего разряда) чисел.В исходном состоянии цотснццал разрешения с управляющего триггера 20 поступает на вентили 5, поэтому в логическую схему 1 вво дятся значения разрядов чисел вернпй пре20 25 30 35 40 45 50 3дел (а) и сравниваемого числа (С), Схема 1 в зависимости от соотношения ука. занных разрядов формирует один из выходных сигналов; больше 2, меньше 3 или равна 4. При этом сигнал равно служит командой опроса для вентилей ввода 5 - 7 младших разрядов указанных чисел, сигнал меньше через собирательную схему 9 поступает в анализатор 21, а сигнал больше через собирательную схему 10 - в анализатор 21.На второй вход вентиля 1 б по шине 27 параллельного ввода поступает значение и-ого разряда (6) числа нижний предел, Оно же поступает через диод 18 и инвертор 30 на вход схемы ИЛИ-НЕ 29, второй вход которой соединен с шиной установки нуля 25, а третий - с шиной параллельного ввода разряда Ьчис:а нижний предел 27,Если Ь,=1, то на выходе вентиля 1 б формируется сигнал, поступающий через собирательную схему 12 в анализатор 21, который формирует при этом ответ не совпало 31. Если указанный сигнал с выхода вентиля 1 б формируется не в и-пом логическом узле 34, например в и - 1, та он поступает не только в анализатор 21, но и через собирательные схемы 8 на входы вентилей 15 всех старших разрядов, на другие входы которых по шинам параллельного,ввода поступаот значения соответствуощих разрядав чисел нижний предел и сравниваемое число.Если на входах хотя бы одного из опрашиваемых вентилей 15, имеется комбинация значений разрядов такая, что С = 1, Ь =О, где К -(и, то на выходе вентиля 15 при этом формируется сигнал, псступаютций через собирательную схему 13 в анализатор 21, формирующий в данном случае ответ совпало 33.Если значение разряда б(; любого другого -го) числа нижний предел такое, что 6=0, то сигнал больше, поступающий через инвертор 30 на вход схемы ИЛИ-НЕ 29, опрашивает последнюю, и на ее выходе при этом формируется сшнал, поступающий в цепи опроса вентилей 15 (аналогично сигналу с вентилей 1 б) через интегрирующую цепочку 17 (на чертеже дальше связи не указаны), собирательную схему 14 в шину 22 опроса вентилей ввода младших разрядов, через собирательную схему 11 в анализатор 21, а так. же через диод 19 на вход инвертора 30.Если ни один из опрашиваемых вентилей 1 б не вырабатывает выходной сигнал, то анализатор 21 формирует посылку, устанавливающую триггер 20 в состояние, при котором разрешающий потенциал подается по соответствующей шине 24 на вентили б ввода разрядов числа нижний предел, К моменту фиксирования указанного состояния сигнал с выхода интегрирующей цепочки 17 опрашивает вентили ввода младших разрядов 5 - 7, при этом В,"ОгиескоЙ схеле 1 (соответствующего узла 34) сравниваются разряды числа нижний предел и сравниваемое число.Сигналы больше или меньше через собирательные схемы 10 и 9 соотвстствего поступают в анализатор 21, формуощий в первом случае ответ не совпало, а во ьтором совпало. Сигнал равно слукит сигналом опроса вентилей ввода младших разрядов 5 - 7. Предмет изобретения Устройство для двухпредельного сравнения п-разрядных двоичных чисел, содержащее анализатор, соединенный с шиной опроса, с шинами команд, управляющим триггером, первой, второй группами собирательных схем, схемы сравнения с выходами больше, равно и меньше, соединенные с первой и третьей группами собирательных схем и с вентилями ввода чисел, интегрирующие цепочки, соединенные непосредственно с собирательными схемами, первые вентили поразрядного сравнения связаны со второй группой собирательных схем, схемы ИЛИ-НЕ, инверторы, сл.ичаощееея тем, что, с целью повышения быстродействия устройства, в нем выходы вентилей ввода чисел верхнего и нижнего пределов сравнения объединены, выходы шин разрешения верхнего и нижнего преде лов подключены к противоположным выходам управляющего триггера, а выходы поразрядных шпн больше схем сравнения соединены с собирательными схемами первой группы, с первыми входами вторых вентилей поразрядно о сравпспия, вторые входы которых соединены с шиной ввода числа нижнего предела, кроме того, эти же шины схем сравнения через диоды и инверторы подключены к первым входам схем ИЛИ-НЕ, выходы которых через интегрирующие цепочки, собирательные схемы подключены к шинам опроса вентилей ввода младших разрядов чисел и через диоды соединены со входами инверторов,Типография, пр. Сапунова, 2 аказ 166914 Тираж 480 ЦНИИПИ Комитета по дедам изобретений и открытий п Москва, Центр, пр. Серова, д.Подписное Совете Министров СССР

СмотретьЗаявка

1176455

А. А. Бурмака

МПК / Метки

МПК: G06F 7/04

Метки: двоичных, двухпредельного, п-разрядных, сравнения, чисел

Опубликовано: 01.01.1969

Код ссылки

<a href="https://patents.su/3-238889-ustrojjstvo-dlya-dvukhpredelnogo-sravneniya-p-razryadnykh-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для двухпредельного сравнения п-разрядных двоичных чисел</a>

Предыдущий патент: Дешифратор адреса

Следующий патент: Двухтактный сумматор параллельного действия

Случайный патент: Способ борьбы с внезапными выбросами угля и газа