Устройство для умножения двух я-разрядных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 222011

Автор: Левицкий

Текст

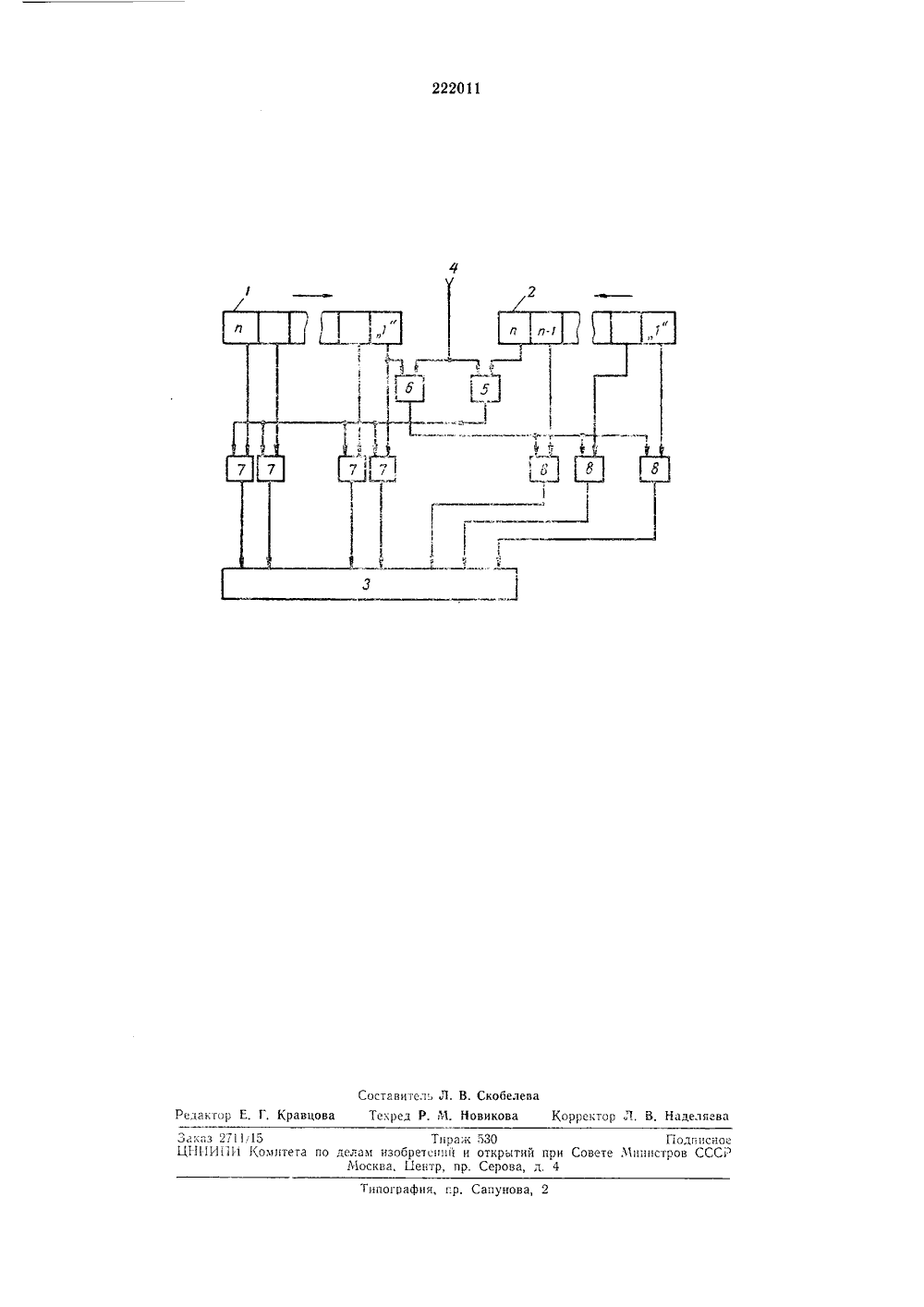

2220 П О П И С А Н И Е ИЗОБРЕТЕНИЯ Слез Советских Социалистических РеспубликЗависимое от авт. свидетельства ХэЗаявлено 20,11,1967 ( 1135766/26-21с присоединением заявки М Кл, 42 гпз, 7(5 МПК 6 061УДК 681.325,57(088 юрят Комитет ло делам изобретений н открытий лрн Совете Министров СССРОпубликовано 17,Ъ 1.1968. Вюллстеиь М 22Дата опубликования описания 26.1 Х.1968 Авторизобретен В. А. Левицки аявитель СТРОЙСТВО ДЛ ОЖЕНИЯ ДВУХ гг-РАЗРЯДНЬ 1 Х ЧИ Известны устроисгва для умножения двухи-разрядных чисел, содержащие регистрымножимого и множителя с цепями сдвига,схемы совпадения и 2 и-разрядный параллельный сумматор.Предложенное устройство отличается от известных тем, что первые входы схем совпадений, формирующих младшие разряды частичных произведений, подключены к единичнымвыходам всех разрядов регистра хгножителя,кроме стар.пего разряда, вторые входы этихсхем совпадений объединены и связаны с единичным выходом младшего разряда регистрамножимого через схему совпадения, второйвход которой подключен к шине тактовых импульсов,Такое соединение позволит упростить конструкцию устройства и повысить его надежность. На чертеже представлена структурная схема предлагаемого устройства. Схема содержит 1 - /г-разрядный регистр множимого с цепями сдвига кода на олин разряд вправо, 2 - и-разрядный регистр множителя с цепями сдвига кода на один разряд влево, 3 - 2 гг-разрядный параллельный двоичный сумматор, 4 в це выдачи (из узла управления) такговых импульсов передачи частичного произведения в сумматор 3, б - схему совпадений, один вход колорой подключен к единичному выходу триггера старшего разряда регистра 2, а другой - к цепи 4, б - схему совпадений, один вход которой подключен к единичному выходу триггера младшего разряда регистра 5 1, а другой - к цепи 4, 7 - и-схем совпадений, первые входы которых подключены к единичным выходам триггеров всех разрядов регистра 1, вторые входы - к выходу схемы совпадений 5, а выходы схем совпадений - к 0 входам старших разрядов (от и-го до 2 гг -1-го) сумматора 3, Ви - 1 схем совпадений, первые входы которых подключены к единичным выходам триггеров всех разрядов регистра 2 (крозге самого старшего), все вторые вхо ды - к выходу схемы совпадений б, а выходы этих схем совпадений - к входам младших (от 1-го до и - 1-го) разрядов суммато 3 Устройство работает следующим образом, 20 После введения в регистры 1 и 2 кодов сомножителей при поступлении по цепи 4 тактового импульса выполняется передача кода регистра 1 в старшие разрялы сумматора 3, если в старшем разряде регистра 2 записана 25 с 1 и передача кода регистра 2 (крокге самого старшего разряда) в младшие разряды сумматора, если в младшем разряде регистра 1 записана 1. Во время выполнения суммирования в сумматоре 3, осуществляются сдви- ЗО ги кода (в регистре 1 - на один разряд впра5 10 15 20 25 30 35 40 во а в регистре 2 - на один разряд влево), При этом в старшем разряде регистра 1 и младшем разряде регистра 2 устанавливаются нули. Далее при приходе по цепи 4 следующих тактовых импульсов описанные операции повторяются либо до тех пор, пока хотя бы в одном из регистров 1 и 2 це окажется код, состоящий из одних нулей, либо и раз,Поскольку после каждого сдвига в регистрах 1 и 2 в оставшихся в цих кодах устанавливается обязательно по одному нулю, которые потом продвигаются по этим регистрам, то максимально возможное число единиц в коде у каждого послслуощему частичного произведения окажется ца два меньше, чем у предыдущего.Объяснение действия устройства основано на замене используемого в известных устройствах ромба (получаемого при выписыват)и всех частичных произведений, ооразуемых в каждом такте, без их суммирования, но с учетом их сдвигов) эквивалентным ему с точки зрения результата треугольником.Пусть, например, осуществляется умножение двух четырехразрядцых двоичных чисел АВС 0 (множимое) и аост (мцожитель).Тогда для известных устройств с направлениями сдвигов в регистрах множимого и множителя, одинаковыми с показанными ца чертеже, ромб имеет вид:Такты1 Аа234 Ва Са баАб Вд Сб Л 6Ас Вс Сс 1.1 сАд Вг 1 Сг 1 ЕМ Треугольник для предлагаемого устройства имеет вид:Такты1 Аа Ва2 А 6 Са Оа Вб бс ВаВ 1 Сб Сс Сд 3 Ас Вс Вд4 АдСледует отметить, что в резульате симметрии треугольника относительно его среднего сголбца фактически безразлично, который цз регистров 1 и 2 (см, чертеж) считать регистром хшожимого и который регистром множителя, при условии, что старшие и разрядов частичных произведений формируются схемами совпадений, цодклоченцыми к тому регистру, у которого прсдусмотрець цепи сдвига кода вправо, а младшие и - 1 разрялов частичных произведений формируются схехамц совпадений, подключенными к разрялам (кро:е самого старшего) того регистра, у котороГо предусОтрсцы цслц сдвига кода влево.Если осуществляется умножение двух гг-разрядных чисел с ОК 1 уГлсцием процзвелсци 51 до гг значащих гифр, то рсдлагасмое у тройство упрощается нуем Исключения из.гицццх п - к разрядов сумматора .5 и п - к схем совпадений 8, фортирующгх самые младшие разряды частичных произведений. Предмет изобретения Устройство для умножения лзух и-разрядцъх чисел, содержащее регистры мцожцмого и множгтеля с цепяхи сдвиГа, схемы совпадения и 2 п-разрядый параллельный сумматОр, ог,гичаюгггееся тем, что, с целью повышения цадежпоси и упрощения конструкции, первые входы схем совпадеццй, формиру;ощих младшие разряды частичных произволений, подклочены к единичным г 5 ыхолам всех разрядов реГист 1 а ъгножителя, кроъге старп 1 ОГО разряда, вторые входы этих схем совпалений объединены и связаны с елццичным выходом младшего разряда регистра мцожимого через схе- мУ совпадецг 51, ВтОРО вход кот 01 ой 110 лключец к шицс тактовых импульсов.-111 ИП 11 Комитета по делам изобретении и открытииМосква, 1.1 ентр, пр. Серова,Подписное те Министров СССР

СмотретьЗаявка

1135766

В. А. Левицкий

МПК / Метки

МПК: G06F 7/52

Метки: двух, умножения, чисел, я-разрядных

Опубликовано: 01.01.1968

Код ссылки

<a href="https://patents.su/3-222011-ustrojjstvo-dlya-umnozheniya-dvukh-ya-razryadnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения двух я-разрядных чисел</a>

Предыдущий патент: Умножитель частоты следования импульсов

Следующий патент: Программирующее и запоминающее устройство

Случайный патент: Способ приготовления эмульгированных вирусных вакцин для животных