Устройство определения разности двух чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 179990

Авторы: Александров, Терешков, Хмелевской

Текст

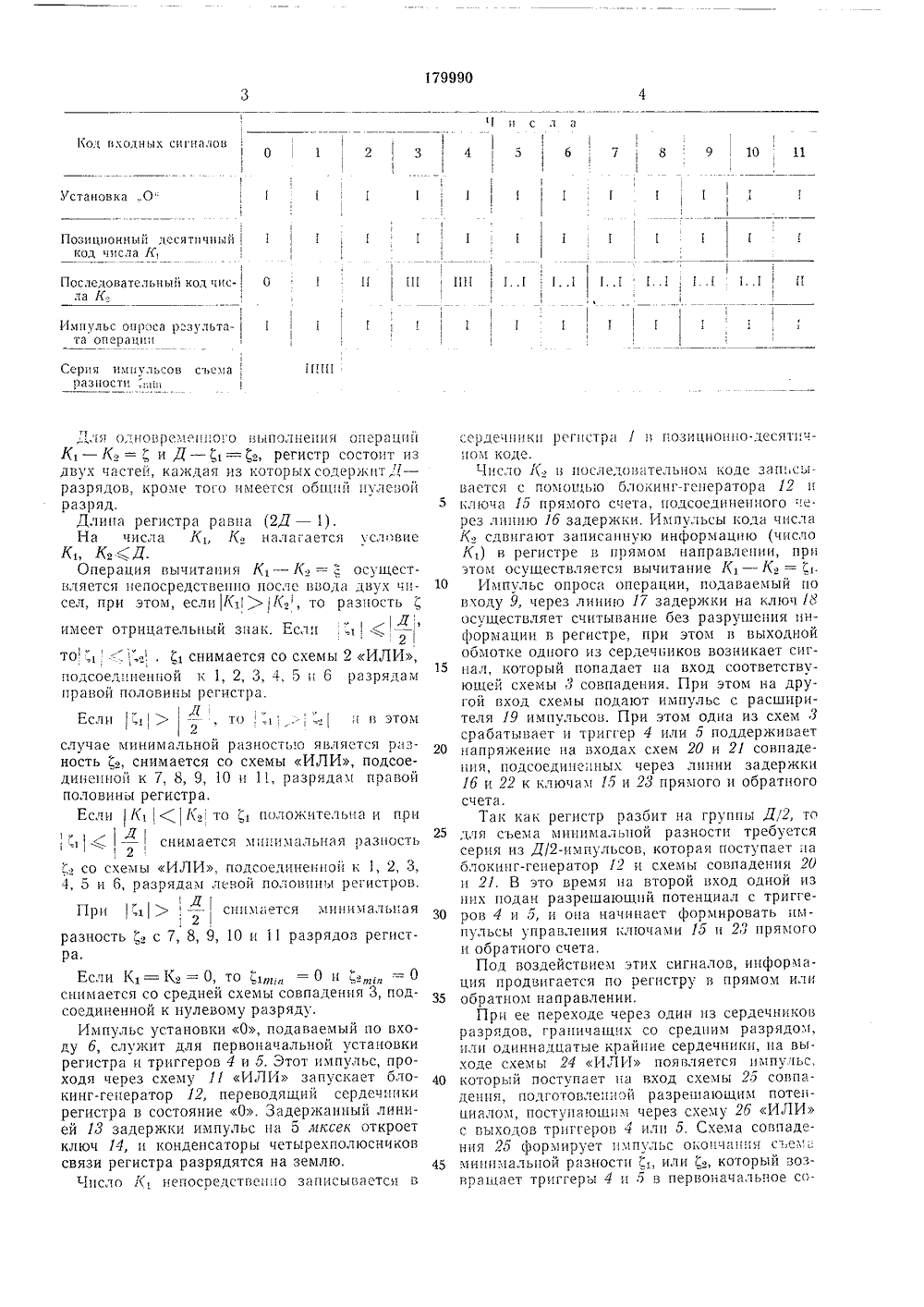

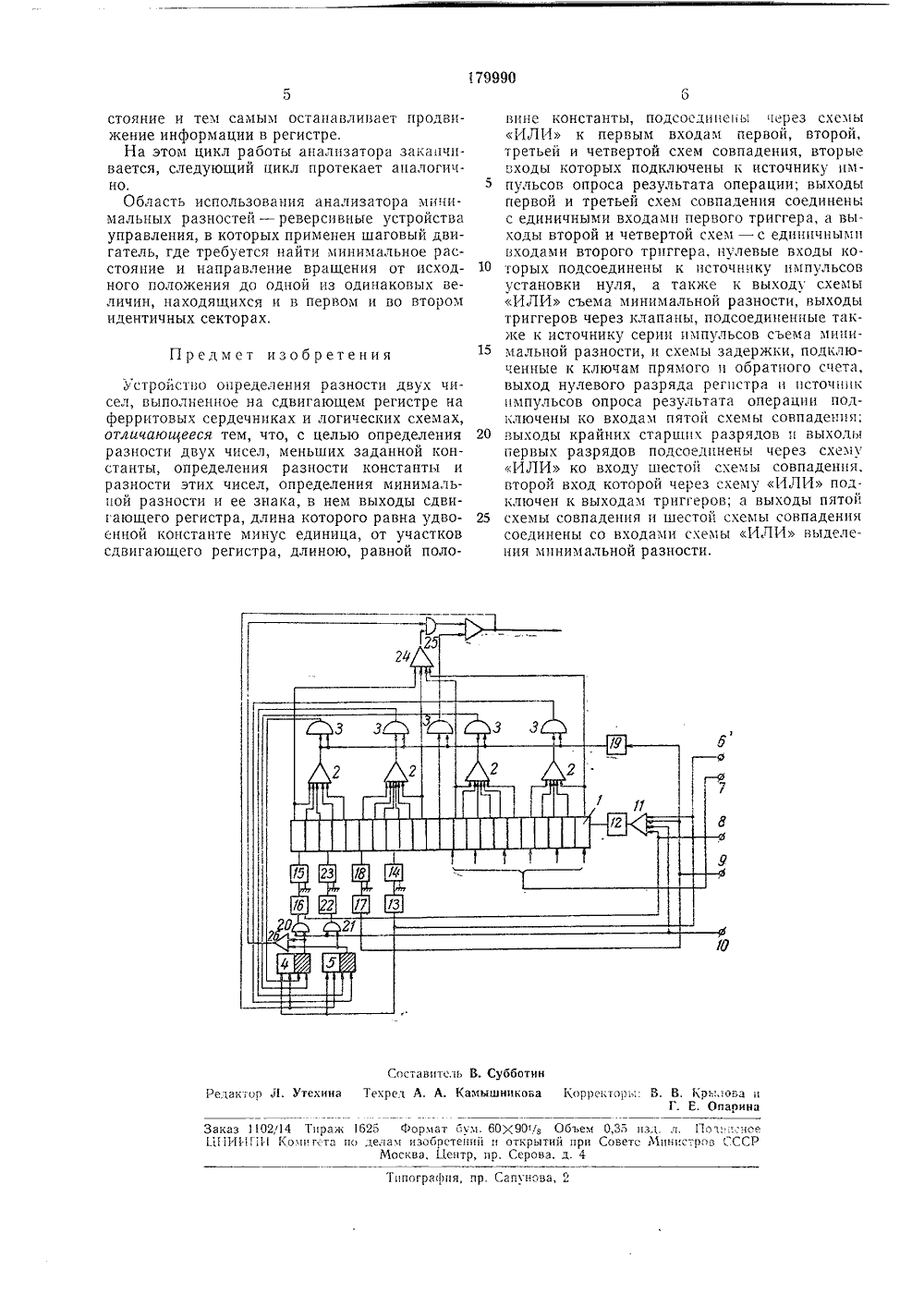

ОПИСАНИЕИЗОБЕЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 37999 Озг зависимое т а Вт, свидетельст явлено 14.Х.1963 1 860853/26-24 ъ 42 пт 14 оз 2 а, 35,Комитет по делам изобретений и открыти.1966. Бюллетень Ло ете МинисСССР Лата опублик ацця описания Авто бов, А. В, Хмелевской ется и аявител РАЗ НОСТ Х ЧИСЕЛ с присоединением заявки Д. С. Терешков, Е. А; Але УСТРОЙСТВО ОПРЕДЕЛЕ Известны устройства определения разности двух чисел, выполненные на сдвцгающем регистре на ферритовых сердечниках.Предложенное устройство отличается тем. что в нем выходы сдвигающего регистра, длина которого равна удвоенной константе минус единица, от участков сдвигающего регистра, длиною, равной половине константы, подсоединены через схемы ИЛИ к первым входам первой, второй, третьей и четвертой схем совпадения, вторые входы которых подключены к источнику импульсов опроса результата операции; выходы первой и третьей схем совпадения соединены с единичными входами первого триггера, а выходы второй и четвертой схем - с единичными входами второго триггера, нулевые входы которых подсоединены к источнику импульсов установки нуля, а также к выходу схемы ИЛИ съема минимальной разности; выходы триггеров через клапаны, ттодсоединенные также к источнику серии импульсов съема минимальной разности, и схемы задержки, подключенные и ключам прямого ц обратного счета, выход нулевого разряда регистра и источник импульсов опроса результата операции подключены ко входам пятой схемы совпадения; выходы крайних старших разрядов и выходы первых разрядов подсоединены через схему ИЛИ ко входу шестой схемы совпадения, второй вход которой через схему ИЛИ подключен к выходамтриггеров; а выходы пятой схемы совпаденияи шестой схемы совпадения соединены со входами схемы ИЛИ выделения минимальной5 разности.Зто позволяет определить разность двух чисел, меньших заданной константы, определитьразность константы и разность этих чисел, определить минимальную разность из этих двух10 разностей, а также определить ее знак.На чертеже представлена блок-схема предлагаемого устройства.Анализатор минимальной разности состоитиз регистра 1 разности, схем 2 ИЛИ и схем15 3 совпадения, объединяющих выходы со всехсердечников регистра в группы минимальныхразностей т; и цтриггеров 4, б управляющих направлением счета в регистре.Анализатор работает от входных сигналов,20 подаваемых по раздельным цепям. По входубподают импульс установки О, по входу 7 -импульс записи числа К, в регистр 1 в позиционно десятичном коде, по входу 8 - сериюимпульсов записи числа Ке в регистр 1 в уни 25 тарном коде; по входу 9 - импульс опросарезультата операции, по входу 10 - серию импульсов съема минимальной разности.Таблица кодов входных сигналов представлена для случая, когда длина регистра 1 ДЗо равна 12 разрядам,179990и с л а 910 , 11 1(о 1 вхолиьсх си па.ов 0 1 23 6 811 1т Установка О" 1 11 1 Позиционный десятичныйкод числа К,11 11 111 1ПП ( 11 О 1 11 Последовательный код чис-, ла К Импульс опроса р зульта-та операцииСерия импульсов съема, разности . ии 11 11 Л 11 ОД 1 ОВРЕМОШ;ОГО ВЫПОЛНЕНИЯ ОПЕРаЦИйК 1 - К = 1; и Д - с",1 -- в, регистр состоит издвух частей, каждая из которых содержит Двразрядов, кроме того имеется общий пулевойразряд,Д:ипа регистра равна 2 Д - 1).На числа Кс, К. налагается словцеКь К 2(Д.Операция вычитания К, - К =-. с осущестссляется непосредственно после ввода двух чисел, при этом, если)Кт ) ( Ке, то разность (имеет отрицательный знак. Если ;-(Я,2то " .-., 1е . т снимается со схемы 2 ИЛИ,подсоединенной и 1, 2, 3, 4, 5 и б разрядамправой половины регистра.ДЕсли ;) -- , то.1,;( 1 в этом2случае минимальной разностьо является разность в, снимается со схемы ИЛИ, подсоединенной к 7, 8, 9, 10 ц 11, разрядам правойполовины регистра.ЕслиК ) К 2 то 1 положительна и пои- снимается минимальная разность. со схемы ИЛИ, подсоединенной к 1, 2, 3,4, 5 и б, разрядам левой половицы регистров.ЯПри .т ) )-снимается мицималыая2разностьс 7, 8, 9, 10 и 11 разрядоз регистра.Если К,=1 в = О, то ",1,Р 1;д =0 и ьалссимается со средней схемы совпадения 3, подсоединенной к нулевому разряду.Импульс установки О, подаваемый по входу б, служит для первоначальной установкирегистра и триггеров 4 и 5. Зтот импульс, проходя через схему 11 ИЛИ запускает блокинг-генератор 12, переводящий сердеч;цкирегистра в состояние О. Задержанны линией 13 задержки импульс ца 5 мксек откроетключ 14, ц конденсаторы четырехполюсниковсвязи регистра разрядятся на землю,Число К непосредственно записывается в верденики рсГцстра11 ГОзициоццо-десятичном коде.Число К, и после,сосительно.; коде засп,сь 1- зется с помощьо бгокспг-генератора 12 1.5 ключа 15 прямого счета, подсоедиепссого через линию 1 б задержки. Импульсы кода числаКв сдвигают записанную информацию (числоКс) в регистре в прямом направлении, приэтом осуществляется вычитание К 1 - К = ".10 Импульс опроса операции, подаваемый повходу 9, через лишпо 17 задерхкки на клю 18осуществляет считывание без разрушения информации в регистре, при этом в выходнойобмотке одного из сердечников возникает сиг 15 цал, который попадает ца вход соответствующей схемы 3 совпадения. При этом на другой вход схемы подают импульс с расширителя 19 импульсов. При этом одна из схем,3срабатывает и триггер 4 или 5 поддерживает20 напряжение ца входах схем 20 и 21 совпадения, подсоедицс ных через линии задержки1 б и 22 к ключам 15 и 23 прямого и обратногосчета.Так как регистр разбит на группы Д/2, то25 для съема минимальной разности требуетсясерия из Д/2-импульсов, которая поступает;аблокицг-гецератор 12 и схемы совпадения 20и 21, В это время ца второй вход одной изнцх подан разрешающий потенциал с тригге 30 ров 4 и 5, и оца начинает формировать цмпульсы управления ключами 15 и 2:.1 прямогоц обратного счета,Под воздействием этих сигналов, информация продвигается по регистру в прямом или35 обратном направлении.При ее переходе через один пз сердечниковразрядов, граничащих со средним разрядом,цли одиннадцатые крайние сердечники, па вы.ходе схемы 24 ИЛИ появляется импульс,40 который поступает ца вход схемы 25 совпадения, подготовлен 1 ой разрешающим потенциалом, поступающим через схему 26 ИЛИс выходов триггеров 4 или 5. Схема совпадения 25 формирует импульс окончания съем.45 минимальной разности с 1, или , который возвращает триггеры 4 и 5 в первоначальное со79990 Предмет изобретения Составитсдь В. Субботин Редактор . Утехина Техред А, А. Камышникова Корректоры: В. В, Крыл.ова и Г. Е, ОпаринаЗаказ 102/14 Тираж 1625 Формат оум. 60 Х 9018 Объем 0,35 изд. гь Поги .сисе1 д 11 ИИГ 111 Комитета по дедам изобретений н открытий при Совете Министров СССРМосква, Центр, пр. Серова, д. 4 Тппограйия, пр. Сапиова, 2 стояние и тем саъых останавливает продвнкение информации в регистре.На этом цикл работы анализатора заканчивается, следующий цикл протекает аналогично.Область использования анализатора минимальных разностей - реверсивные устройства управления, в которых применен шаговый двигатель, где требуется найти минимальное расстояние и направление вращения от исходного положения до одной из одинаковых величин, находящихся и в первом и во втором идентичных секторах,устройство определения разности двух чисел, выполненное на сдвигающем регистре на ферритовых сердечниках и логических схемах, отличающееся тем, что, с целью определения разности двух чисел, меньших заданной константы, определения разности константы и разности этих чисел, определения минимальой разности и ее знака, в нем выходы сдвигающего регистра, длина которого равна удвоенной константе минус единица, от участков сдвигающего регистра, длиною, равной половине константы, подсоедиеы через схемы ИЛИ к первым входам первой, второй, третьей и четвертой схем совпадения, вторые входы которых подключены к источнику им пульсов опроса результата операции; выходыпервой и третьей схем совпадения соединены с единичными входами первого триггера, а выходы второй и четвертой схем - с единичными входами второго триггера, нулевые входы ко торых подсоединены к источнику импульсовустановки нуля, а также и выходу схемы ИЛИ съема минимальной разности, выходы триггеров через клапаны, подсоединенные также к источнику серии импульсов съема миниТ 5 мальной разности, и схемы задержки, подключенные к ключам прямого н обратного счета, выход нулевого разряда регистра н источнк импульсов опроса результата операции подключены ко входам пятой схемы совпадения;20 выходы крайних старших разрядов и выходыпервых разрядов подсоединены через схему ИЛИ ко входу шестой схемы совпадения, второй вход которой через схему ИЛИ подключен к выходам триггеров; а выходы пятой 25 схемы совпадения и шестой схемы совпадениясоединены со входами схемы ИЛИ выделения минимальной разности.

СмотретьЗаявка

860853

Д. С. Терешков, Е. А. Александров, А. В. Хмелевской

МПК / Метки

МПК: G06F 7/50

Опубликовано: 01.01.1966

Код ссылки

<a href="https://patents.su/3-179990-ustrojjstvo-opredeleniya-raznosti-dvukh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство определения разности двух чисел</a>

Предыдущий патент: Устройство для моделирования динамическихпроцессов

Следующий патент: Устройство группового ввода информации с перфокарт в электронную вычислительнуюмашину

Случайный патент: Способ определения количества песка вбетоне