Устройство для параллельного счета количества единиц в двоичном п-разрядном коде

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

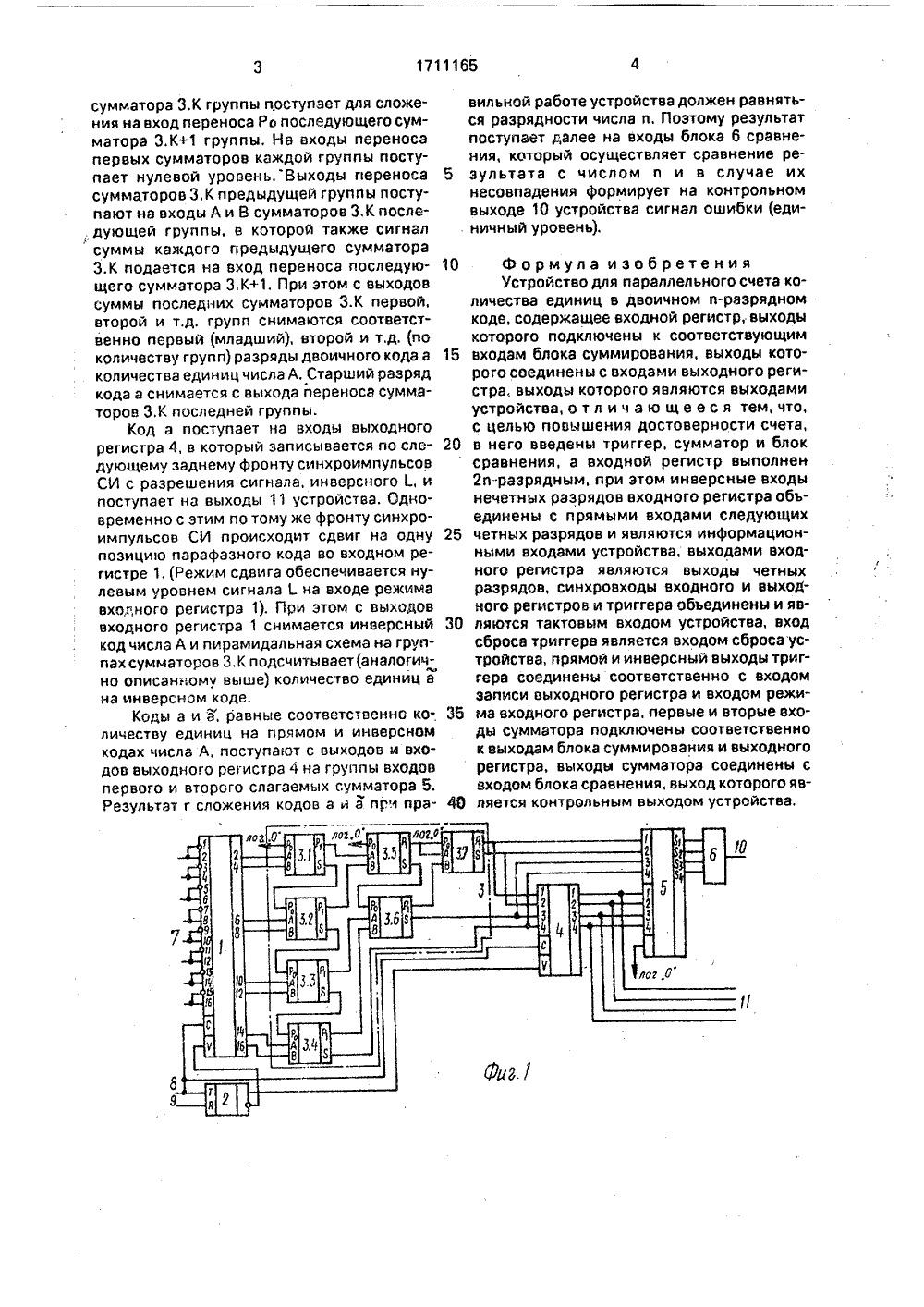

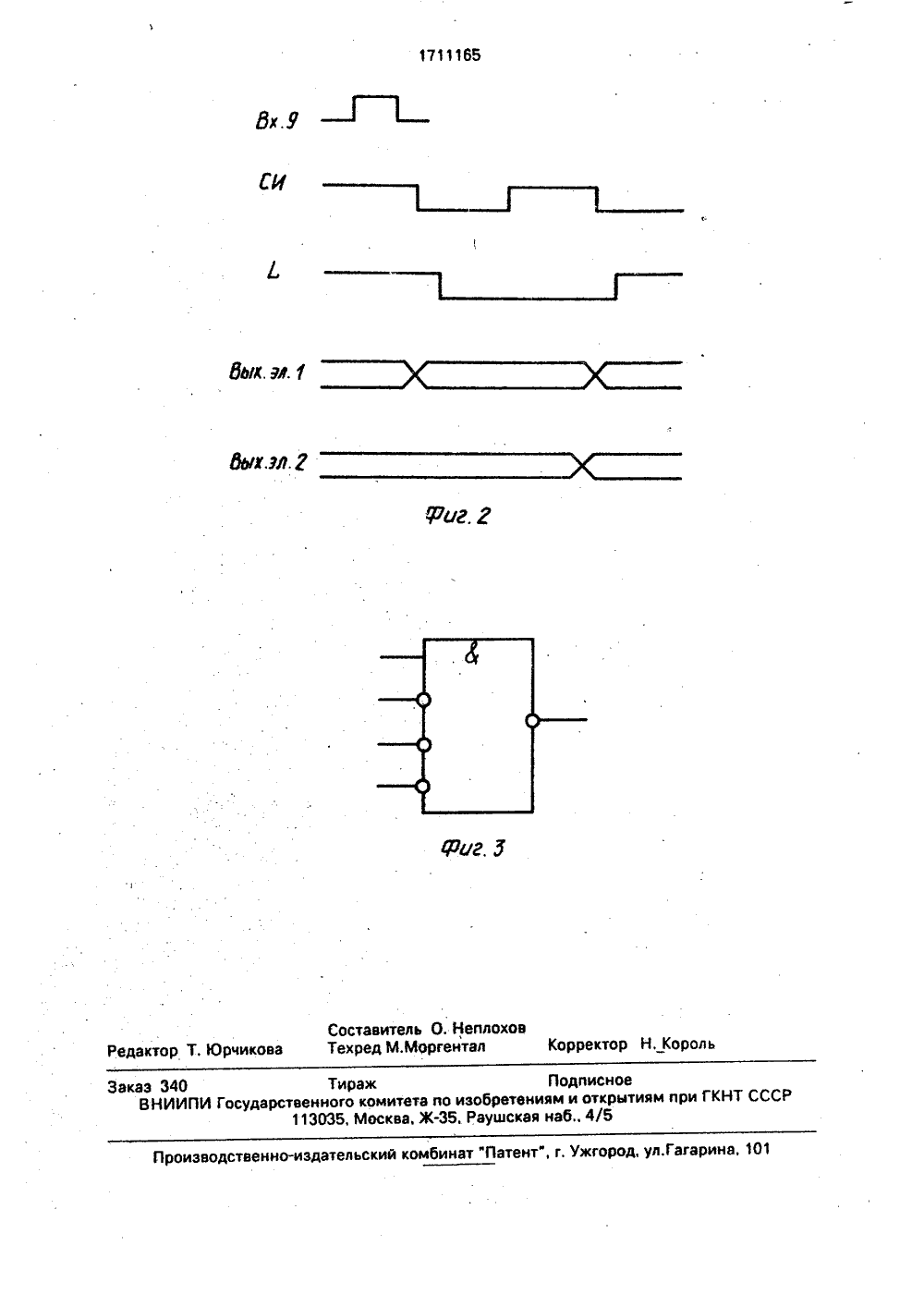

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(71) Одесский политехнический институт(56) Авторское свидетельство СССРМ 450160, л, Н 03 М 7/04, 1972.(54) УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОГОСЧЕТА КОЛИЧЕСТВА ЕДИНИЦ В ДВОИЧНОМ и-РАЗРЯДНОМ КОДЕ Изобретение относится к вычислительной технике и может быть использовано в системах контроля цифровой информации,Целью изобретения является повышение достоверности счета.На фиг.1 представлена структурная схема устройства для и = 8; на фиг.2 - временные диаграммы сигналов; на фиг.3 - пример выполнения блока сравнения,Устройство содержит входной регистр 1, триггер 2, блок 3 суммирования, выходной регистр 4, сумматор 5, блок 6 сравнения, информационные 7 и тактовый 8 входы, вход 9 сброса, контрольный 10 и информационные 11 выходы, Блох 3 суммирования содержит сумматоры З.К, соединенные соответствующим образом,Устройство работает следующим образом.В начальный момент времени на вход 9 сброса устройства поступает импульс, сбрасывающий триггер 2 в нулевое состояние. На вход 8 устройства поступают синхроимпульсы СИ, тактирующие работу устройства, Под действием этих импульсов,с 51 м 0 06 Г 11/ОО, Н 03 М 7/04(57) Изобретение относится к вь,ислительной технике и может быть использовано в системах контроля цифровой информации, Целью изобретения является повышение достоверности счета, Устройство содержит входной регистр 1, триггер 2, блок 3 суммирования, выходной регистр 4, сумматор 5, блок 6 сравнения, информационные 7 и тактовый 8 входы, вход 9 сброса, контрольный 10 и информационные 11 выходы устройства. Блок 3 суммирования содержит сумматоры З,К. 3 ил. приходящих на счетный вход триггера Т-типа, на его инверсном выходе формируется сигнал , показанный на Фиг,2. На входы 7 устройства поступают разряды двоичного числа А. Это число парафазным кодом записывает я во входной регистр 1 по заднему фронту синхросигналов СИ, При этом на вход режима входного регистра 1 подается с инверсного выхода триггера 2 единичный уровень сигналами, разрешающий прием кодаВходной регистр 1 имеет 2 п разрядов для хранения парафазного кода и-разрядного числа, причем инверсный вход(2)-1)-го и прямой вход 2)-го разрядов этого регистра обьединены между собой и являются 1-и входом входного регистра 1., )-м выходом которого является выход 21-го разряда,) = ;и,В результате записи парафазного кода во входной регистр 1 на его выходах появляется прямой код двоичного числа А. Этот код поступает на входы А и В сумматоров 3.1 - 3,4 первой группы блока 3 суммирования. Сигнал суммы каждого предыдущегосумматора З.К группы поступает для сложения на вход переноса Ро последующего сумматора З.К+1 группы. На входы переноса первых сумматоров каждой группы поступает нулевой уровень. Выходы переноса 5 сумматоров 3, К предыдущей группы поступают на входы А и В сумматоров З.К после, дующей группы, и которой также сигнал суммы каждого предыдущего сумматора З.К подается на вход переноса последую щего сумматора З,К+1, При этом с выходов суммы последних сумматоров З.К первой, второй и т,д. групп снимаются соответственно первый (младший), второй и т,д. (по количеству групп) разряды двоичного кода а 15 количества единиц числа А, Старший разряд кода а снимается с выхода переноса сумматоров З.К последней группы.Код а поступает на входы выходного регистра 4, в который записывается по сле дующему заднему фронту синхроимпульсов СИ с разрешения сигнала, инверсного ., и поступает на выходы 11 устройства, Одновременно с этим по тому же фронту синхроимпульсов СИ происходит сдвиг на одну 25 позицию парафазнаго кода во входном регистре 1. (Режим сдвига обеспечивается нулевым уровнем сигналана входе режима входного регистра 1). При этом с выходов входного регистра 1 снимается инверсный ЗО код числа А и пирамидальная схема на группах сумматоров 3, К подсчитывает(аналогично описанному выше) количество единиц а на инверсном коде.Коды а и а, равные соответственно ко-. З 5 личестеу единиц на прямом и инверсном кодах числа А, поступаот с выходов и входов выходного регистра 4 на группы входов первого и второго слагаемых сумматора 5. Результат г сложения кодов а и а при пра О вильной работе устройства должен равняться разрядности числа и. Поэтому результат поступает далее на входы блока 6 сравнения, который осуществляет сравнение результата с числом и и в случае их несовпадения формирует на контрольном выходе 10 устройства сигнал ошибки (единичный уровень). Формула изобретения Устройство для параллельного счета количества единиц в двоичном и-разрядном коде, содержащее входной регистр, выходы которого подключены к соответствующим входам блока суммирования, выходы которого соединены с входами выходного регистравыходы которого являются выходами устройства,отл и чаю ще еся тем, что, с целью повышения достоверности счета, в него введены триггер, сумматор и блок сравнения, а входной регистр выполнен 2 п-разрядным, при этом инверсные входы нечетных разрядов входного регистра абьединены с прямыми входами следующих четных разрядов и являются информационными входами устройства, выходами входного регистра являются выходы четных разрядов, синхровходы входного и выходного регистров и триггера обьединены и являются тактовым входом устройства, вход сброса триггера является входом сброса устройства, прямой и инверсный выходы триггера соединены соответственно с входом записи выходного регистра и входом режима входного регистра, первые и вторые входы сумматора подключены соответственно к выходам блока суммирования и выходного регистра, выходы сумматора соединены с входом блока сравнения, выход которого я в- ляется контрольным выходом устройства,1711165 бык.ю. 1Составитель О. Неплохое Редактор Т. Юрчикова Техред М.Моргентал Корректор Н. Король Заказ 340 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Рэушская наб 4/5Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина. 101

СмотретьЗаявка

4657863, 02.03.1989

ОДЕССКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ДРОЗД АЛЕКСАНДР ВАЛЕНТИНОВИЧ, ПОЛИН ЕВГЕНИЙ ЛЕОНИДОВИЧ, ЙОРДАНОВ ЙОРДАН БОЯНОВ, ЛАЗДИН АРТУР ВЯЧЕСЛАВОВИЧ, ДРОЗД ЮЛИЯ ВЛАДИМИРОВНА

МПК / Метки

МПК: G06F 11/00, H03M 7/04

Метки: двоичном, единиц, коде, количества, п-разрядном, параллельного, счета

Опубликовано: 07.02.1992

Код ссылки

<a href="https://patents.su/3-1711165-ustrojjstvo-dlya-parallelnogo-scheta-kolichestva-edinic-v-dvoichnom-p-razryadnom-kode.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для параллельного счета количества единиц в двоичном п-разрядном коде</a>

Предыдущий патент: Устройство приоритета

Следующий патент: Устройство для анализа производительности вычислительных систем

Случайный патент: 304335