Способ считывания информации из элементов памяти на полевых транзисторах и формирователь сигналов считывания

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

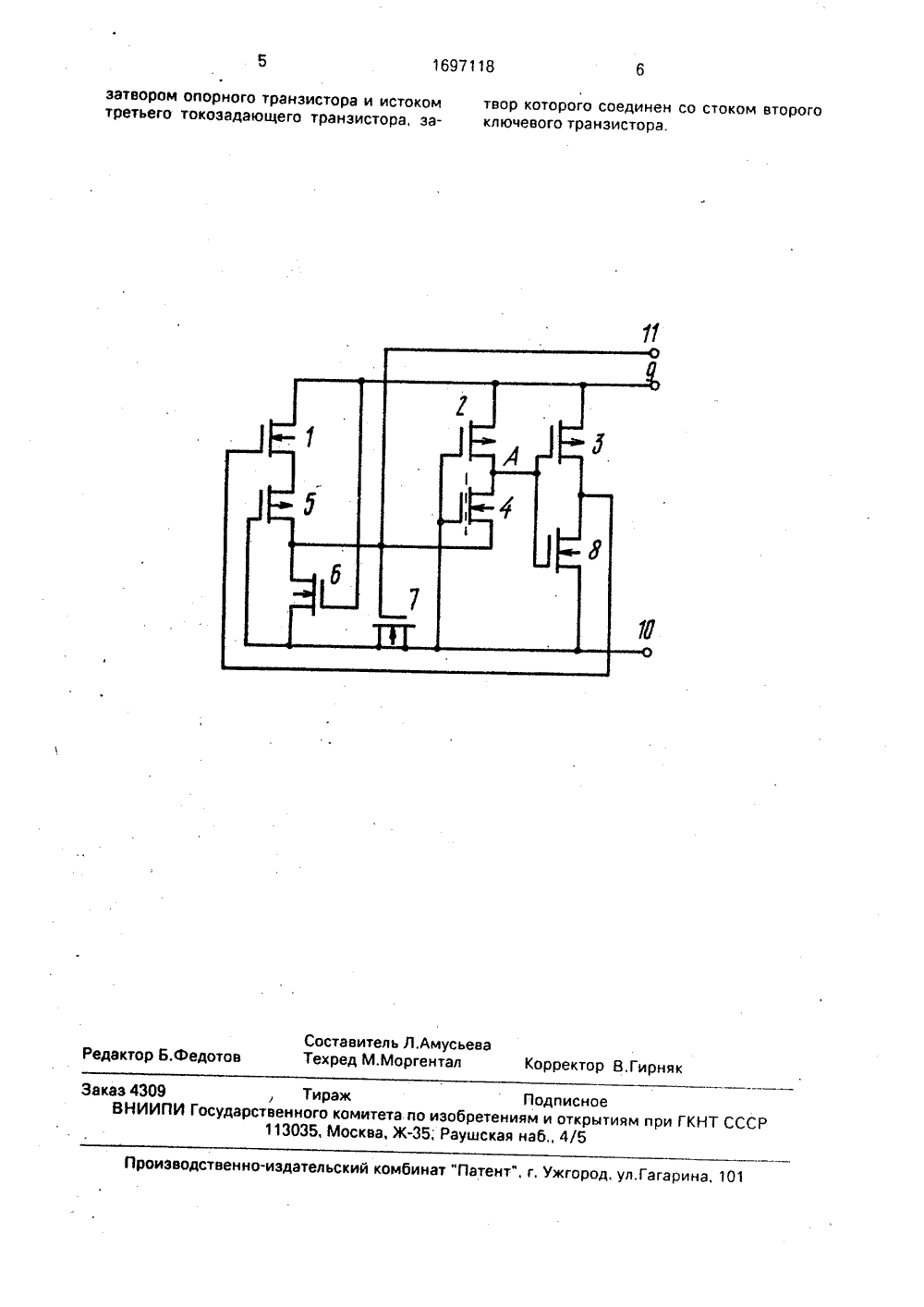

(5)5 О 7 О ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИПРИ ГКНТ СССР ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКО ВИДЕТЕЛЬСТВУ ФО РМАА ПОЛЕ- ВАТЕЛЬ 0 че- тыалом с ка- кана- щий ипа, м и- ана(21) 4718104/24(54) СПОСОБ СЧИТЫВАНИЯ ИНЦИИ ИЗ ЭЛЕМЕНТОВ ПАМЯТИ НВЫХ ТРАНЗИСТОРАХ И ФОРМИРОСИГНАЛОВ СЧИТЫВАНИЯ(57) Изобретение относится к вычислитеной технике и микроэлектронике и мож Изобретение относится к вычислительной технике и микроэлектронике и можетбыть использовано при разработке электрически стираемых программируемых постоянных запоминающих устройств (ЭСППЗУ)большой информационной емкости,Цель изобретения - повышение надежности считывания информации,На чертеже представлена электриская схема формирователя сигналов счивания. Формирователь содержит второй чевой транзистор 1 с каналом и-типа вый токозадающий транзистор 2 с кан р-типа, третий ключевой транзистор 3 налом р-типа, опорный транзистор 4 с лом п-типа, второй токозадаю транзистор 5 с каналом р-типа, третий задающий транзистор 6 с каналом пнакопительный транзистор 7 с канал типа, первый ключевой транзистор 8 с быть использовано при разработке репрограммируемых постоянных запоминающих устройств большой информационной емкости, Цель изобретения - повышение надежности считывания информации. Поставленная цель достигается подачей сигналов управления считывания на исток в запирающем для элемента памяти направлении и изменением их амплитуды пропорционально изменению уровня порогового элемента памяти до достижения им нулевого значения и обеспечивается расширением области допустимых значений порогового напряжения, исключением из состава ячейки памяти адресного транзистора. 1 з.п.флы,1 ил,лом п-типа, шину 9 питания, шину 10 нулевого потенциала, выход 11.Способ считывания информации из элементов памяти на полевых транзисторах завввввв ключается в следующем. Элемент памяти О представляет собой п-канальный, МНОП- транзистор. Для считывания информации из о на сток и затвор подают положитель ное напряжение относительно подложки, например 2 В и 4 В соответственно, а на исток - напряжение той же полярности, что на затвор и сток, При этом напряжение на истоке элемента памяти является запирающим р-л-переход исток-подложка Это напряжение изменяют пропорционально изменению порогового напряжения элемента памяти. При считывании информации изменение порогового напряжения элемента памяти происходит за счет изменения заряда в области обеднения подложки и не меняет величину информационного зарядаэлемента памяти, а также его логическое ,состояние. Изменение порогового напряжения элемента памяти ограничено нулевым значением, чтобы исключить ложное считывание информации из соседних не- выбранных элементов памяти (на затворе которых напряжение равно нулю), через которые также может протекать ток, если пороговое напряжение этих элементов (в случае использования п-канальной технологИи) в результате стирания информации примет отрицательные значения.При подключении напряжения на исток в запирающем для элемента памяти направлении (т.е, повышающем его пороговое напряжение) его пороговое напряжение увеличивается, При этом низкий уровень порОгового напряжения из отрицательного (для и канальных приборов) становится нулевым,Способ считывания информации из элементов памяти на полевых транзисторах может быть осуществлен с использованием фермирователя сигналов считывания. Формирователь работает следующим образом.В процессе стирания информации пороговое напряжение опорного транзистора 4 становится отрицательным.Подбором геометрических размеров транзисторов 2 и 4 добиваются того, что в этом случае потенциал в узле А становится ниже потенциала запирания транзистора 8 и выход 11 начинает заряжаться от шины 9 пИтания через транзисторы 1,5, причем размером транзистора 5 регулируется ток (постоянная времени заряда выхода 11). С повышением напряжения на выходе 11, а следовательно и на истоке транзистора 4 пороговое напряжение. последнего возрастает и при достижении определенной величины становится равным нулю, Транзистор 4 (опорный элемент памяти) закрываетсяа потенциал в узле А становится равным напряжению питания, что достаточно для запирания транзистора 3,В результате этого потенциал выхода 11 начинает понижаться за счет разряда емкости транзистора 7 через открытый канал транзистора б, Ток разряда (постоянная времени разряда) регулируется подбором геометрических размеров транзистора 6.Как только напряжение навыходе 11 достигнет величины, достаточной для отпирания транзистора 4, потенциал в узле А понижается, и емкость выхода 11 снова начинает заряжаться, т,е. напряжение на выходе 11 начинает возрастать. Таким образом, величина напряжения выхода 11 поддерживается на некотором заданном уровне, определяемом уровнем порогового напряжения транзистора 4. 5 10 15 20.25 30 35 40 45 50 55 Выход 11 подключается схемой управления к истокам запоминающих элементов матрицы накопителя в режиме считывания.Формула изобретения 1, Способ считывания информации из элементов памяти на полевых транзисторах, включающий формирование на электродах затвора и стока элемента памяти постоянных уровней напряжения относительно напряжения на подложке и определение информации, хранящейся в элементе памяти, по величине тока, протекающего через элемент памяти, о т л и ч а ю щ и й с я тем, что, с целью повышения надежности считывания информации, одновременно с формированием постоянных уровней напряжения на электродах стока и затвора элемента памяти на электрод истока элемента памяти подают напряжение той же полярности относительно напряжения на подложке, что и на электроды стока и затвора элемента памяти, изменяют напряжение на электроде истока элемента памяти пропорционально изменению порогового напряжения элемента памяти до достижения им нулевого значения.2, Формирователь сигналов считывания, содержащий первый и второй ключевые транзисторы с каналом п-типа, третий ключевой транзистор с каналом р-типа, первый и второй токозадающие транзисторы с каналом р-типа, третий токозадающий транзистор с каналом п-типа, накопительный транзистор с каналом п-типа, опорный трэнзистор с каналом п-типа, сток которого соединен с затворами первого и третьего ключевых транзисторов и стоком первого токозадающего транзистора, исток которого соединен с истоком третьего ключевого транзистора и подключен к шине питания формирователя, а затвор соединен с затвором опорного ключевого транзистора, сток третьего ключевого транзистора соединен со стоком первого ключевого транзистора, исток которого подключен к шине нулевого потенциала формирователя и соединен с истоком накопительного транзистора и истоком третьего токозадающего транзистора, сток которого соединен со стоком второго токоэадающего транзистора, затвор которого соединен со стоком накопительного транзистора, о т л и ч а ю щ и й с я тем, что сток и затвор второго ключевого транзистора соединены с истоком и стоком третьего ключевого транзистора соответственно, а исток соединен с истоком второготокозадающего транзистора, сток которого соединен Ь истоком опорного транзистора, затвором накопительного транзистора и является выходом формирователя, а затвор соединен с1697118 затвором опорного транзистора и истоком третьего токоэадающего транзистора, заСоставитель Л.Амусьеваедактор Б,Федотов Техред М.Моргентал Корректор В,Гирня Тираж Подписнственного комитета по изобретениям и отк 113035, Москва, Ж; Раушская наб 4/5 тиям при ГКНТ СС Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 аказ 4309 ВНИИПИ Госуд твор которого соединен со стоком второгоключевого транзистора.

СмотретьЗаявка

4718104, 22.05.1989

ПРЕДПРИЯТИЕ ПЯ Х-5737

СИДОРЕНКО ВЛАДИМИР ПАВЛОВИЧ, СТИКАНОВ ВАЛЕРИЙ ЕФИМОВИЧ, ГУСЕВА ТАТЬЯНА ГРИГОРЬЕВНА

МПК / Метки

МПК: G11C 7/00

Метки: информации, памяти, полевых, сигналов, считывания, транзисторах, формирователь, элементов

Опубликовано: 07.12.1991

Код ссылки

<a href="https://patents.su/3-1697118-sposob-schityvaniya-informacii-iz-ehlementov-pamyati-na-polevykh-tranzistorakh-i-formirovatel-signalov-schityvaniya.html" target="_blank" rel="follow" title="База патентов СССР">Способ считывания информации из элементов памяти на полевых транзисторах и формирователь сигналов считывания</a>

Предыдущий патент: Способ измерения параметров прижимного ролика и устройство для его осуществления

Следующий патент: Устройство для сдвига информации

Случайный патент: Способ получения алюминиево-кремниевого сплава в электролизере для производства алюминия