Формирователь импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

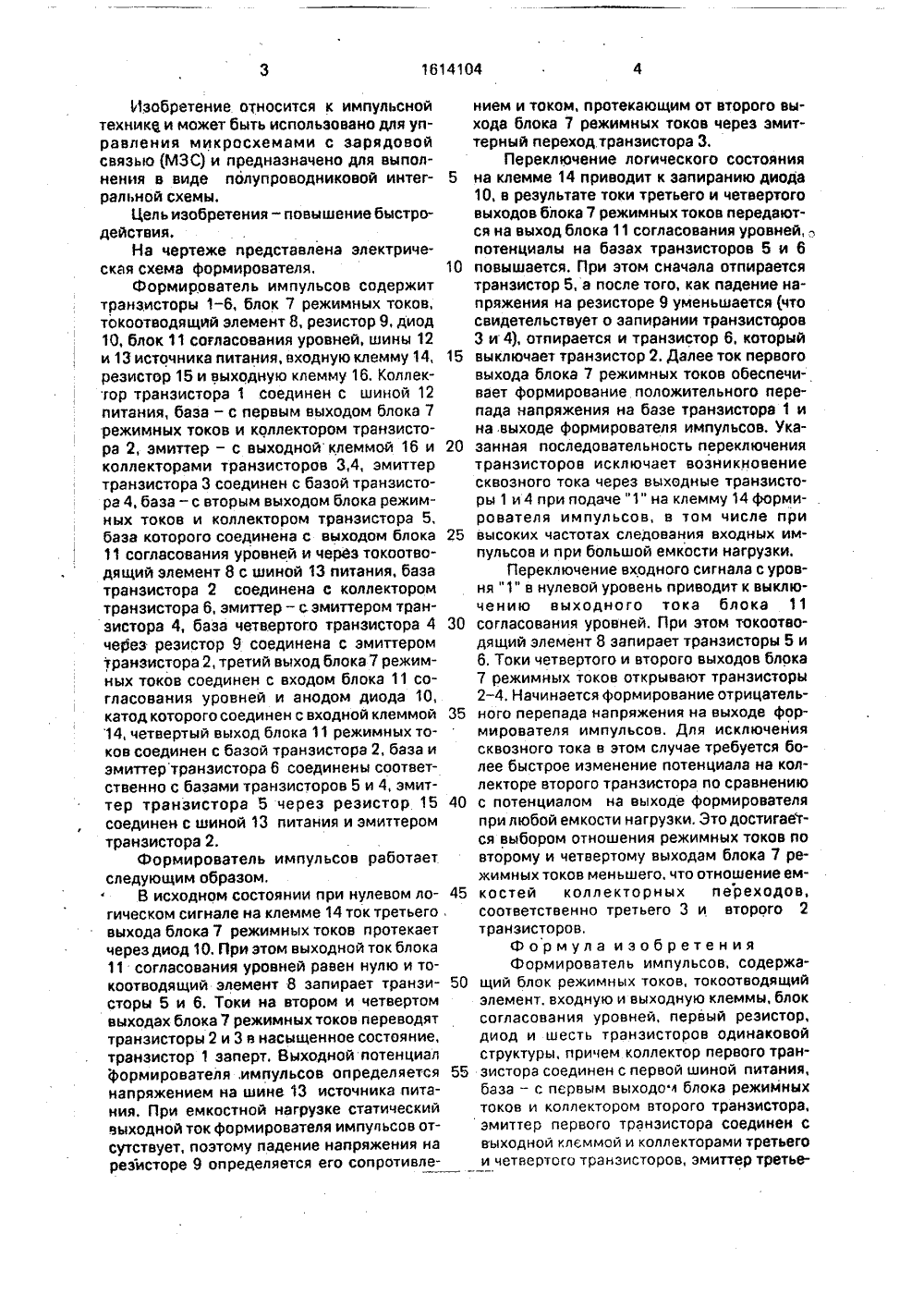

(5)5 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБРЕТЕНИ К КОМУ СВИДЕТЕЛЬСТ(57) Изобретение относится к импульсной технике и может быть использовано для управления микросхемами с зарядовой связью. Целью изобретения является повышение быстродействия, что достигается в результате предложенного схемногр построения формирователя импульсов. Формирователь содержит транзисторы 1-6, блок 7 режимных токов, токозадающий элемент 8, резистор 9, диод 10, блок 11 согласования уровней, шины 12 и 13, входную клемму 14, выходную клемму 16, резистор 15. 1 ил.Изобретение относится к импульсной технике и может быть использовано для управления микросхемами с зарядовой связью (МЗС) и предназначено для вцполнения в виде полупроводниковой интегральной схемы.Цель изобретения - повышение быстродействия,На чертеже представлена электрическая схема формирователя.Формирователь импульсов содержит транзисторы 1-6, блок 7 режимных токов, токоотводящйй элемент 8, резистор 9, диод 10, блок 11 согласования уровней, шины 12 и 13 источника питания, входную клемму 14, резистор 15 и выходную клемму 16. Коллектор транзистора 1 соединен с шиной 12 питания, база - с первым выходом блока 7 режимных токов и коллектором транзистора 2, эмиттер - с выходной клеммой 16 и коллекторами транзисторов 3,4, эмиттер транзистора 3 соединен с базой транзистора 4, база - с вторым выходом блока режимных токов и коллектором транзистора 5, база которого соединена с выходом блока 11 согласования уровней и через токоотводящий элемент 8 с шиной 13 питания, база транзистора 2 соединена с коллектором транзистора 6, эмиттер - с эмиттером транзистора 4, база четвертого транзистора 4 через резистор 9 соединена с эмиттером транзистора 2, третий выход блока 7 режимных токов соединен с входом блока 11 согласования уровней и анодом диода 10, катод которого соединен с входной клеммой 14, четвертый выход блока 11 режимных токов соединен с базой транзистора 2, база и эмиттертранзистора 6 соединены соответственно с базами транзисторов 5 и 4, эмиттер транзистора 5 через резистор 15 соединен с шиной 13 питания и эмиттером транзистора 2.Формирователь импульсов работает следующим образом.В исходном состоянии при нулевом логическом сигнале на клемме 14 ток третьего выхода блока 7 режимных токов протекает через диод 10. При этом выходной ток блока 11 согласования уровней равен нулю и токоотводящий элемент 8 запирает транзисторы 5 и 6. Токи на втором и четвертом выходах блока 7 режимных токов переводят транзисторы 2 и 3 в насыщенное состояние, транзистор 1 заперт, Выходной потенциал формирователя, импульсов определяется напряжением на шине 13 источника питания. При емкостной нагрузке статический выходной ток формирователя импульсов отсутствует, поэтому падение напряжения на резисторе 9 определяется его сопротивле 55 зистора соединен с первой шиной питания,база - с первым выходоблока режимных токов и коллектором второго транзистора,эмиттер первого транзистора соединен свыходной клеммой и коллекторами третьего и четвертого транзисторов, эмиттер третье 1015 2030354045 50 нием и током, протекающим от второго выхода блока 7 режимных токов через эмиттерный переход. транзистора 3Переключение логического состояния на клемме 14 приводит к эапиранию диода 10, в результате токи третьего и четвертого выходов блока 7 режимных токов передаются на выход блока 11 согласования уровнейпотенциалы на базах транзисторов 5 и 6 повышается. При этом сначала отпирается транзистор 5, а после того, как падение напряжения на резисторе 9 уменьшается (что свидетельствует о эапирании транзисторов 3 и 4), отпирается и транзистор 6, который выключает транзистор 2. Далее ток первого выхода блока 7 режимных токов обеспечивает формирование положительного перепада напряжения на базе транзистора 1 и на вцходе формирователя импульсов. Указанная последовательность переключения транзисторов исключает возникновениесквозного тока через выходные транзисторы 1 и 4 при подаче "1" на клемму 14 формирователя импульсов, в том числе при высоких частотах следования входных импульсов и при большой емкости нагрузки.Переключение входного сигнала с уровня "1" в нулевой уровень приводит к выключению выходного тока блока 11согласования уровней. При этом токоотводящий элемент 8 запирает транзисторы 5 и6, Токи четвертого и второго выходов блока 7 режимных токов открывают транзисторы2 - 4, Начинается формирование отрицательного перепада напряжения на выходе формирователя импульсов. Для исключения сквозного тока в этом случае требуется более быстрое изменение потенциала на коллекторе второго транзистора по сравнениюс потенциалом на выходе формирователяпри любой емкости нагрузки, Это достигается выбором отношения режимных токов по второму и четвертому выходам блока 7 режимных токов меньшего, что отношение емкостей колл екто рных переходов, соответственно третьего 3 и второго 2 транзисторов.Формула изобретения Формирователь импульсов, содержащий блок режимных токов, токоотводящий элемент, входную и выходную клеммы, блок согласования уровней, первый резистор, диод и шесть транзисторов одинаковой структуры, причем коллектор первого тран1614104 6 Составитель А. КоробковРедактор Л. Пчолинская Техред М.Моргентал Корректор В. Гирняк Заказ 3897 Тираж 665. Подписное ВНИИПИ Государственного комитета по изобретениям и открытигм при ГКНТ СССР 113035, Москва, Ж, Раушская наб., 4/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101 го транзистора соединен с базой четвертого транзистора, база третьего транзистора - с вторым выходом блока режимных токов и коллектором пятого транзистора, база которого соединена с выходом блока согласования уровней и через токоотводящий элемент с второй шиной питания, база второго транзистора соединена с коллектором шестого транзистора, а эмиттер - с эмиттером четвертого транзистора, база четвертого транзистора через первый резистор соединена с змиттером второго транзистора, третий выход блока режимных токов соединен с входом блока согласования и анодом диода, катод которого соединен с входной клеммой, о т л и ч а ю щ и й с я тем, что, с целью повышения быстродействия, в него 5 введен второй. резистор, четвертый выходблока режимных токов соединен с базой второго транзистора, база и эмиттер шестого транзистора соединены соответственно с базами пятого и четвертого 10 транзисторов, эмиттер пятого транзисторачерез второй резистор соединен с второй шиной питания и змиттером второго транзистора.

СмотретьЗаявка

4346095, 18.12.1987

МОСКОВСКИЙ ИНЖЕНЕРНО-ФИЗИЧЕСКИЙ ИНСТИТУТ, ПРЕДПРИЯТИЕ ПЯ А-3562

ГОЛЬДШЕР АБРАМ ИОСИФОВИЧ, ДИК ПАВЕЛ АРКАДЬЕВИЧ, ЛАШКОВ АЛЕКСЕЙ ИВАНОВИЧ, СТЕНИН ВЛАДИМИР ЯКОВЛЕВИЧ

МПК / Метки

МПК: H03K 5/01

Метки: импульсов, формирователь

Опубликовано: 15.12.1990

Код ссылки

<a href="https://patents.su/3-1614104-formirovatel-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь импульсов</a>

Предыдущий патент: Формирователь импульсов

Следующий патент: Синхронизатор импульсов

Случайный патент: Датчик для измерения алвжности сыпучих и пористых материалов