Цифровой генератор синусоидальных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

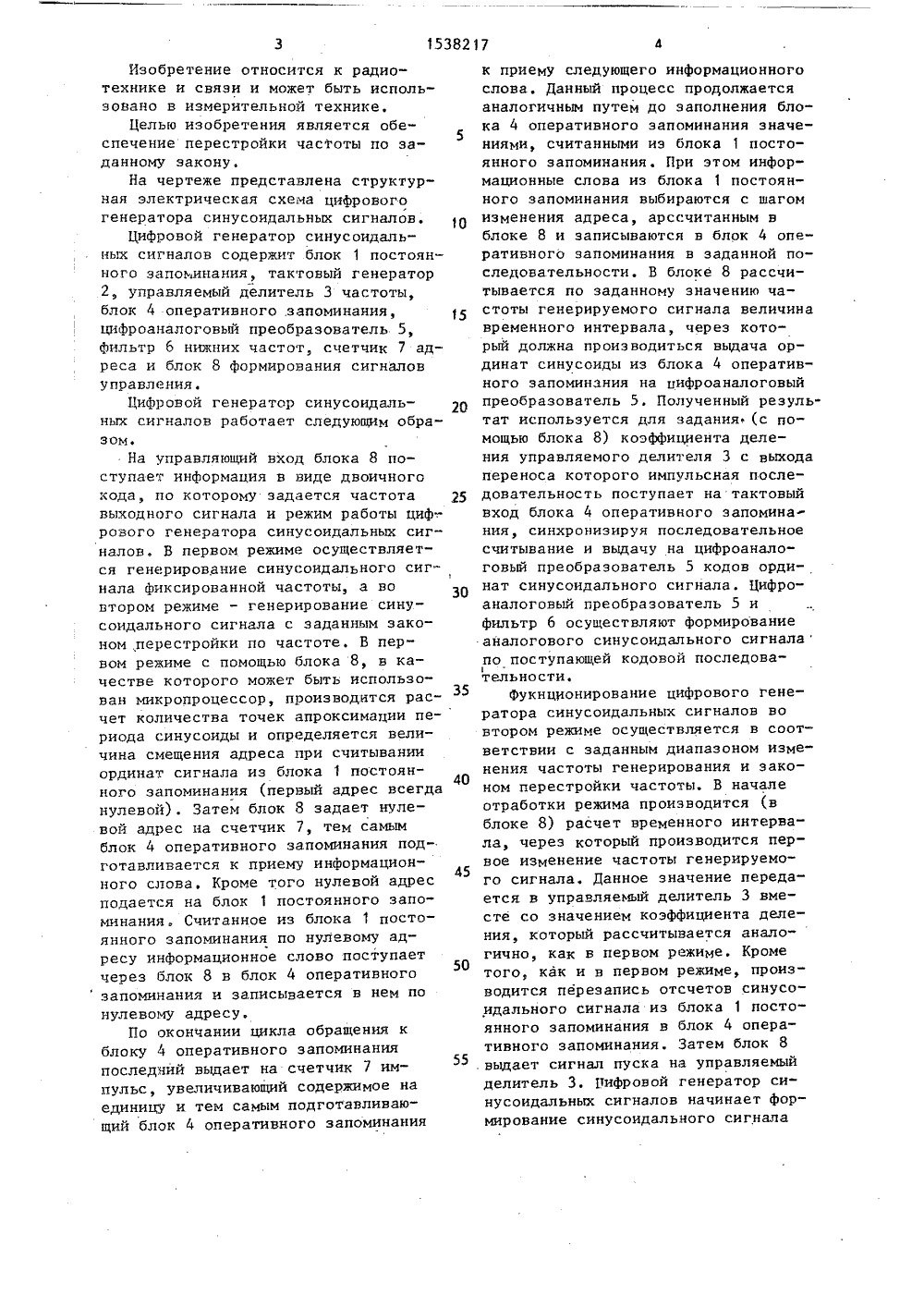

СОЮЗ СОВЕТСКИХсоцидлистичеснихРЕСПУБЛИН 9) 51) 19 0 ГОСУДАРСПО ИЗОБПРИ ГКН енный комитетЕТЕНИЯМ И ОТНРЫТИЯМ ССР ОПИСАНИЕ ИЗОБРЕТЕ ЕЛЬСТ нусолок 1 ит В ел заным диапазономнерирования ичастоты осущес соответстви зад частоты герестройкиенерированлов. При эсходит бм сигна зменения аконом п ляется г ых сигна -ра прои ЬР СИНУС ькаене е синусоидом перест адио- еспепауз межд различных ситсяения асто ани оты по эаданК АВТОРСКОМУ СВИ(1) Институт техничтики АН БССР(56) Лукьянов Д.А. ПЗный элемент цифровойропроцессорные средст1986, В 1, с,77.(54) ЦИФРОВОЙ ГЕНЕРАНЫХ СИГНАЛОВ(57) Изобретение отнтехнике. Цель изобречение перестройки ча 2закону. Цифровой гьных сигналов содероянного запоминания2, управляемый делиблок 4 оперативного5, фильтр 6 нижних7 адреса и блок 8 фалов управления, Целвведением управляечастоты,с помощьюИзобретение относится к радиотехнике и связи и может быть использовано в измерительной технике.Целью изобретения является обе 5спечение перестройки частоты по заданному закону.На чертеже представлена структурная электрическая схема цифровогогенератора синусоидальных сигналов.Цифровой генератор синусоидальных сигналов содержит блок 1 постоянного запоминания, тактовый генератор2, управляемый делитель 3 частоты,блок 4 оперативного запоминания,цифроаналоговый преобразователь 5,Фильтр б нижних частот, счетчик 7 адреса и блок 8 Формирования сигналовуправления.Цифровой генератор синусоидальных сигналов работает следующим образом.На управляющий вход блока 8 поступает информация в ниде двоичногокода, по которому задается частотавыходного сигнала и режим работы циф-.рового генератора синусоидальных сигналов. В первом режиме осуществляется генерирование синусоидального сигнала фиксированной частоты, а вовтором режиме - генерирование синусоидального сигнала с заданным законом,перестройки по частоте, В первом режиме с помощью блока 8, в качестве которого может быть использо 35 ван микропроцессор, производится расчет количества точек апроксимации периода синусоиды и определяется величина смещения адреса при считывании ординат сигнала иэ блока 1 постоянного запоминания (первый адрес всегда нулевой). Затем блок 8 задает нулевой адрес на счетчик 7, тем самым блок 4 оперативного запоминания подготавливается к приему информационного слова. Кроме того нулевой адрес подается на блок 1 постоянного запоминания. Считанное из блока 1 постоянного запоминания по нулевому адресу информационное слово поступает50 через блок 8 в блок 4 оперативногозапоминания и записывается в нем по нулевому адресу.По окончании цикла обращения к блоку 4 оперативного запоминания55 последний выдает на счетчик 7 импульс, увеличивающий содержимое на единицу и тем самым подготавливающий блок 4 оперативного запоминания к приему следующего информационного слова. Данный процесс продолжается аналогичным путем до заполнения блока 4 оперативного запоминания значениями, считанными иэ блока 1 постоянного запоминания. При этом информационные слова из блока 1 постоянного запоминания выбираются с шагом изменения адреса, арссчитанным н блоке 8 и записываются н блок 4 оперативного запоминания в заданной последовательности. В блоке 8 рассчитывается по заданному значению частоты генерируемого сигнала величина временного интервала, через который должна производиться выдача ординат синусоиды из блока 4 оперативного запоминания на цифроаналоговый преобразователь 5, Полученный результат используется для задания(с помощью блока 8) коэффициента деления управляемого делителя 3 с выхода переноса которого импульсная последовательность поступает на тактовый вход блока 4 оперативного запоминания, синхронизируя последовательное считывание и выдачу на цифроаналоговый преобразователь 5 кодов ординат синусоидального сигнала. Цифроаналоговый преобразователь 5 и фильтр 6 осуществляют формирование аналогового синусоидального сигнала по поступающей кодовой последовательности.Фукнционирование цифрового генератора синусоидальных сигналов во втором режиме осуществляется н соответствии с заданным диапазоном изменения частоты генерирования и законом перестройки частоты. В начале отработки режима производится (в блоке 8) расчет временного интервала, через который производится первое изменение частоты генерируемого сигнала, Данное значение передается н управляемый делитель 3 вместе со значением коэффициента деления, который рассчитывается аналогично, как н первом режиме, Кроме того, как и в первом режиме, производится перезапись отсчетов синусоидального сигнала из блока 1 постоянного запоминания н блок 4 оперативного запоминания. Затем блок 8 выдает сигнал пуска на управляемый делитель 3. Пифроной генератор синусоидальных сигналов начинает формирование синусоидального сигнала5 15382 первой из частот заданного диапазона. В блоке 8 производится расчет необходимых параметров для перехода . на следующую частоту диапазона в соответствии с заданным законом перестройки (рассчитывается число точек апроксимации периода синусоиды, величина смещения адреса для считывания из блока 1 постоянного запоми 10 нания, длительность интервала между считываниями отсчетов из блока 4 оперативного запоминания для подачи на цифроаналоговый преобразователь 5, значение временного интервала, че рез который будет производиться переход на формирование синусоидального сигнала новой частоты), По завершении расчета блок 8 переходит в режим ожидания сигнала с выхода 2 О управляемого делителя 3, говорящего об окончании временного интервала генерирования сигнала данной частоты и готовится к переходу к генерированию сигнала с новым значением 25 частоты. При появлении этого сигнала с помощью блока 8 осуществляется замещение значений дискретных отсчетов синусоиды одной частоты на значение отсчетов синусоиды другой ча О стоты, Это происходит следующим образом.Процесс считывания и подачи на цифроаналоговый преобразователь 5 очередного отсчета синусоидального сигнала происходит аналогично проце 35 дуре, описанной при рассмотрении режима генерирования сигнала с постоянной частотой, Однако в блок 4 оперативного запоминания по адресу 4 О считанного очередного отсчета записывается значение, соответствующее сигналу новой частоты. Данное значение извлекается с помощью блока 8 иэ блока 1 постоянного запоминания. При этом шаг изменения адресов блока 1 постоянного запоминания обеспечивается путем добавления в блоке 8 рассчитанного ранее значения смещения адреса к текущему значению.Модификация адреса считывания и записи для блока 4 оперативного запоминания происходит в счетчике 7 путем добавления единицы из блока 4 оперативного запоминания к текущему значению по окончании очередного 17 6такта считывания или записи и записи блоком 8 в счетчик 7, адреса на единицу меньшего, чем текущий перед заменой очередной ординаты синусоидального сигнала,Таким образом, эа период полного считывания информации из блока 4 оперативного запоминания происходит замена ее содержимого на значения, относящиеся к новой частоте генерирования, и начинается формирование синусоидального сигнала. При этом перестройка генератора происходит беэ пауз между генерированием сигналов различных частот.Формула изобретенияЦифровой генератор синусоидальных сигналов, содержащий последовательно соединенные блок оперативного запоминания, цифроаналоговый преобразователь и фильтр нижних частот, тактовый генератор, счетчик адреса, блок постоянного запоминания и блок формирования сигналов управления, о т л и ч а ю щ и й с я тем, что, с целью обеспечения перестройки частоты по заданному закону, введен управляемый делитель частоты, тактовый вход которого соединен с выходом тактового генератора, информационные выходы блока постоянного запоминания, управялемого делителя частоты, блока оперативного запоминания и счетчика адреса соединены с информационным входом блока формирования сигналов управления, управляющий выход которого соединен с входами блока постоянного запоминания, управляемого делителя частоты, блока оперативного запоминания и счетчика адреса, адресный выход которого соединен с адресным входом блока оперативного запоминания, выход переноса управляемого делителя частоты соединен с тактовым входом блока оперативного запоминания, выход стробирующго импульса которого соединен со счетным входом счетчика адреса,дополнительный вход блока формирования сигналов управления является управляющим входом цифрового генератора синусоидальных сигналов.

СмотретьЗаявка

4324593, 03.11.1987

ИНСТИТУТ ТЕХНИЧЕСКОЙ КИБЕРНЕТИКИ АН БССР

ДАШУК ВЛАДИМИР НИКОЛАЕВИЧ, ДЕМИДЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, КУНОВСКИЙ ЭДУАРД БРОНИСЛАВОВИЧ, БОРИСОВ ИГОРЬ ФЕДОРОВИЧ, ШИХОВ НИКОЛАЙ БОРИСОВИЧ, ЧЕГОЛИН ПЕТР МИХАЙЛОВИЧ

МПК / Метки

МПК: H03B 19/00

Метки: генератор, сигналов, синусоидальных, цифровой

Опубликовано: 23.01.1990

Код ссылки

<a href="https://patents.su/3-1538217-cifrovojj-generator-sinusoidalnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой генератор синусоидальных сигналов</a>

Предыдущий патент: Генератор сигналов инфранизких частот

Следующий патент: Синтезатор частот

Случайный патент: Парциальный водомер для открытого канала