Дельта-сигма-кодер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

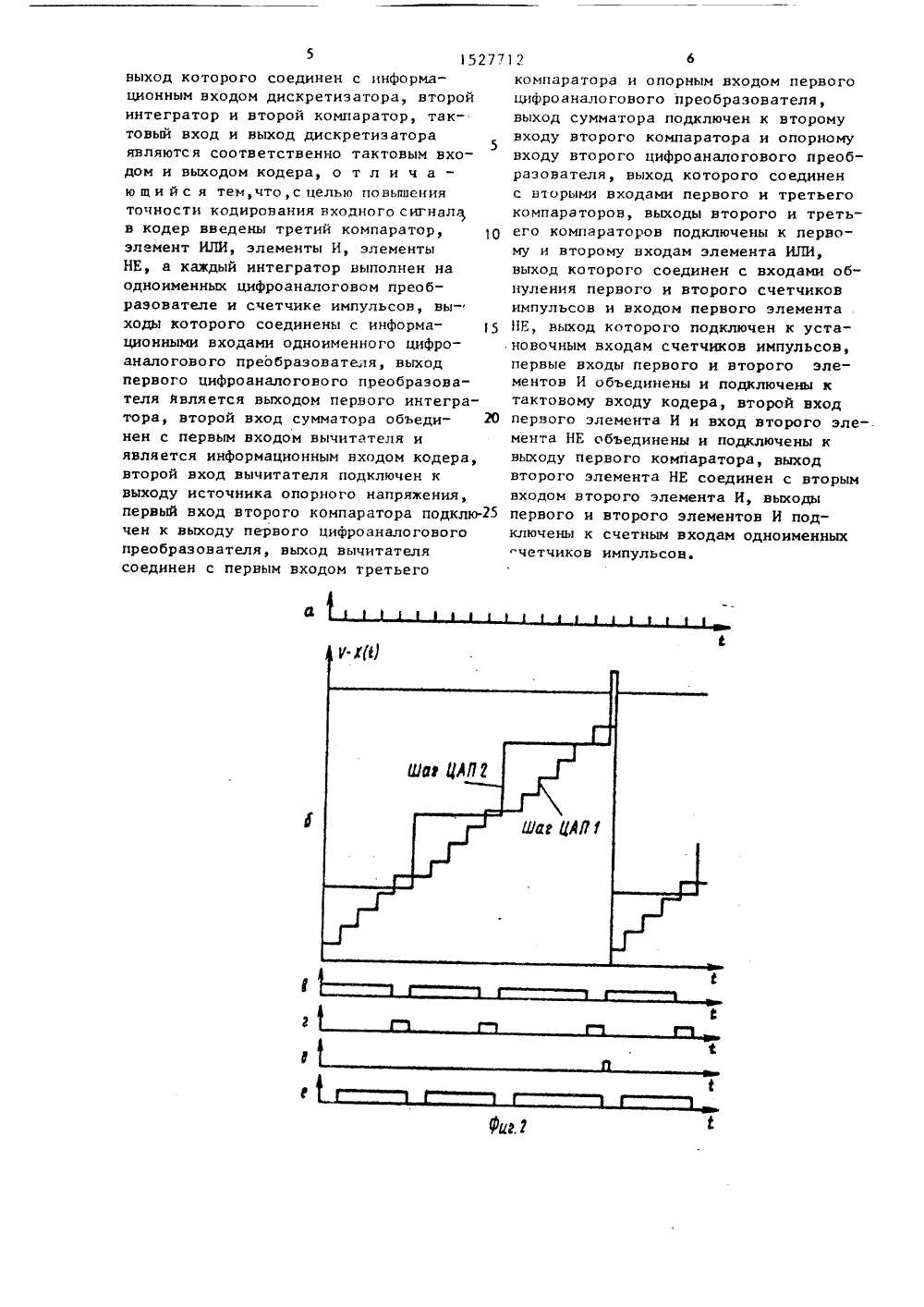

СООЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 1 03 М 3 02 ГОСУДАРСТ 8 ЕННЫИ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИПРИ ГКНТ СССР и ПИСАНИЕ ИЗОБРЕТЕНИЯА ВТОРСНОМ,К СВИДЕТЕЛЬСТВУ-24 Бюл, 9 литех чес инст ше Г(53) 621,376.5 Его использование в цифровых системасвязи, измерений, телеиехаяикн позволяет повысить точность кодированиявходного сигнала, Дельта-сигма-кодерсодержит вычитатель 1, сумматор 2,источник 3 опорного напряжения, дискретиэатор 9, компараторы 10, 11 иинтеграторы 13, 14. Благодаря введенэлементов И 4, 5, элементов НЕ 6, 7,элемента ИЛИ 8, компаратора 12 и выполнению каждого из интеграторов13, 14 на счетчике 15 импульсов ицифроаналоговом преобразователе 16точность кодирования определяетсяразрядностью счетчиков 15 к преобразователей 16. 2 ил.Изобретение относится к вычислительной технике и технике связи иможет быть использовано в цифровыхсистемах связи, измерений, телемеханики.Цель изобретения - повышение точности кодирования входного сигнала.На Фиг,1 приведена функциональнаясхема дельта-сигма-кодера; на фиг.2 - 10временные диаграммы его работы.Дельт;-сигма-кодер содержит вычитатель 1, сумматор 2, источник 3опорного напряжения, первый ивторой элемента И 4 и 5 и первый 15и второй элементы НЕ б и 7, элементИБ 8, дискретизатор 9, первыйтретий компараторы 10 - 12 и первый ивторой интеграторы 13 и 14, каждыйиэ которых включает в себя счетчик 2015 импульсов и цифроаналоговый преоб-разователь (ЦАП) 16. На фиг.1 обозначены информационный и тактовыйвходы 17 и 18.Дельта-сигма-кодер работает сле-, 25дующим образом.На вход 18 приходят тактовые импульсы (фиг.2 а), входной сигналХ поступает с входа 17 на вычитатель 1 и сумматор 2, которые предназначены цля Формирования размера шага,первого 16.1 и второго 16.2 ЦАП соответственно (Фиг.2 б). В зависимостиот величины входного напряжения накомлараторе 10 на его выходе вырабатывается сигнал (Фиг.2 в), а на выходевторого элемента НЕ 7 - инверсный сигнал (фиг.2 г), которые дискретизируются во времени первым и вторым элементами И 4 и 5 и далее, в противофазе, управляют первым 15,1 и вторым15.2 счетчиками,,Пля удобства рассмотрения предположим, что на вход 17 кодера поступаетположительное напряжение Х(С), находящееся в пределах 0 с, Х(С) с Ч и неизменяющееся во времени. В этом случаесигнал на выходе первого ЦАП 16.1меньше сигнала на выходе второгоЦАП 16.2 и на выходе Компаратора 10появляется логическая "1", которая вмомент прихода стробирующего импульса изменяет текущее состояние первого ЦАП 16,1 на единицу. В случае, если напряжение на выходе первого ЦАП6,1 по-прежнему меньше напряженияна выходе второго ЦАП 16,2, компаратор О остается в том же состоянии.В противном случае на выходе компаратора 10 появляется "О, который далее инвертируется элементом НЕ 7 ичерез второй элемент И 5 изменяет сстояние второго счетчика 15.2 и второго ЦАП 162.Таким образом осуществляется отсчет шагов на выходе первогоЦАП 16.1, размер которых пропорционален разности Ч - Х(1), относительношагов на выходе второго ЦАП 16.2, размер которых пропорционален сумме Ч ++ Х(С) с тем же коэффициентом пропорциональности, причем остаток от каждого предыдущего отсчета переноситсяна следующий отсчет. Непрерывностьотслеживания определяется разрядностью первого и второго ЦАП 16, т.е.временем прохождения полного циклаот начала счета до. сброса,Второй 11 и третий 12 компараторы,элемент ИЛИ 8 и первый элемент НЕ 6служат для формирования сигнала сброса (фиг.2 д), который вырабатываетсяв случае, когда сигнал одного из ЦАП16 превысит соответствующий опорныйуровень для первого ЦАП 16.1 Ч - Х(й)или для второго ЦАП 16.2 Ч + Х(1)При этом не происходит разрыв текущейпачки, что могло бы привести к дополнительной ошибке преобразования.Дискретизатор 9 служит для формирования выходной цифровой последовательности кодера (фиг.2 е).Таким образом происходит преобразование аналогового напряжения в цифровой вид. Функции интеграторов 13 и 14выполняют соответственно первые счетчик 15.1 и ЦАП 16.1 и вторые счетчик15,2 и ЦАП 16.2. Следовательно, точность преобразования целиком определяется разрядностью счетчиков 15 иЦАП 16. Для простоты рассмотренияна временных диаграммах (фиг.2) проиллюстрированы варианты с четырехразрядными счетчиками 15 и ЦАП 16.Практически достаточно высокие качественные характеристики достигаютсяпри применении 8-12 и более разрядных ЦАП,Формула изобретенияДельта-сигма-кодер, содержащий вычислитель, источник опорного напряжения, выход которого соединен с первым входом сумматора, первый интегратор, выход которого подключен к первому входу первого компаратора,6омпаратора и опорным входом первогофроаналогового преобразователя, ыход сумматора подключен к второму ходу второго компаратора и опорному ходу второго цифроаналогового преобазователя, выход которого соединенвторыми входами первого и третьего омпараторов, выходы второго и третьго компараторов подключены к первои второму входам элемента ИЛИ, ыход которого соединен с входами обгуления первого и второго счетчиков мпульсов и входом первого элемента 3 Е, выход которого подключен к установочным входам счетчиков импульсов, первые входы первого и второго элементов И объединены и подключены к тактовому входу кодера, второй вход первого элемента И и вход второго эле-. мента НЕ объединены и подключены к выходу первого компаратора, выход второго элемента НЕ соединен с вторым входом второго элемента И, выходы первого и второго элементов И подключены к счетным входам одноименных "четчиков импульсов. 15277 выход которого соединен с информа- к ционным входом дискретизатора, второй ци интегратор и второй компаратор, так- в товый вход и выход дискретизатора в являются соответственно тактовым вхо- в дом и выходом кодера, о т л и ч а Р ю щ и й с я тем,что, с целью повыщения с точности кодирования входного сигнала, к в кодер введены третий компаратор, о е элемент ИЛИ, элементы И, элементыНЕ, а каждый интегратор выполнен нав одноименных цифроаналоговом преобразователе и счетчике импульсов, вы- и ходы которого соединены с информационными входами одноименного цифроаналогового преобразователя, выходпервого цифроаналогового преобразователя является выходом первого интегратора, второй вход сумматора объеди нен с первым входом вычитателя иявляется информационным входом кодера, второй вход вычитателя подключен квыходу источника опорного напряжения, первый вход второго компаратора подключен к выходу первого цифроаналогового преобразователя, выход вычитателясоединен с первым входом третьего

СмотретьЗаявка

4374835, 02.02.1988

РИЖСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. А. Я. ПЕЛЬШЕ

ЯНЕНКО ЮРИЙ БОРИСОВИЧ, КОТОВИЧ ГЛЕБ НИКОЛАЕВИЧ, КОМАРОВ КОНСТАНТИН СЕРГЕЕВИЧ

МПК / Метки

МПК: H03M 3/02

Метки: дельта-сигма-кодер

Опубликовано: 07.12.1989

Код ссылки

<a href="https://patents.su/3-1527712-delta-sigma-koder.html" target="_blank" rel="follow" title="База патентов СССР">Дельта-сигма-кодер</a>

Предыдущий патент: Устройство аналого-цифрового преобразования

Следующий патент: Цифровой фильтр с дельта-модуляцией

Случайный патент: Электродвигатель постоянного тока с катящимся ротором