Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

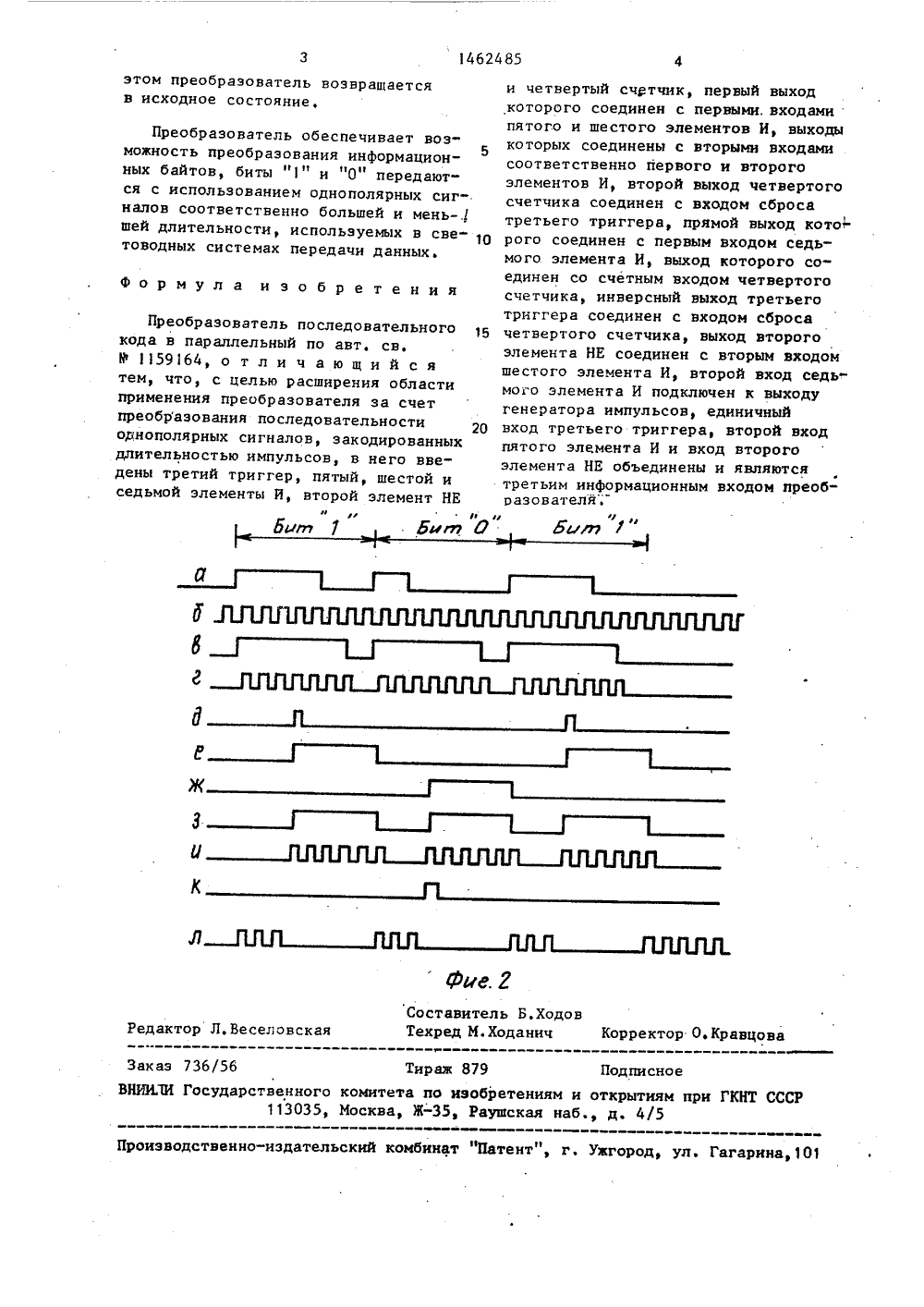

СОЮЗ СОВЕТСНСОЦИАЛИСТИЧЕРЕСПУБЛИН И 9) (И) 5 4 Н 03 М 7/00 ЕНИ ОСУДАРСТВЕННЫЙ НОМИТЕТО ИЗОБРЕТЕНИЯМ И ОТНРЬГГИЯМРИ ГКНТ СССР ИСАНИЕ ИЗО А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ(56) Авторское свидетельство СССР 9 1159164, кл. Н 03 М 7/00, 21.12.83. (54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬ, НОГО КОДА В ПАРАЛЛЕЛЬНЫЙ(57) Изобретение относится к вычислительной технике, может быть использовано при построении преобразователей, входящих в состав аппаратуры сопряжения с двухпроводными каналамисвязи и обеспечивает сопряжение преобразователя как с полудуплевскимдвухпроводным каналом связи, так и сосветоводной системой передачи информации, чем достигается расширениеобласти использования преобразователя.Преобразователь последовательногокода в параллельный содержит семьэлементов И 1,2,3,4,15,16 и 17тритриггера 5,6 и 14, четыре счетчика 7,8,9 и 19, элемент ИЛИ О, два элемента НЕ 11 и 18, генератор 12 импульсов и регистр 13 сдвига. 2 ил.Изобретение относится к вычислительной технике и может быть исполь, зовано при построении преобразователей, входящих в состав аппаратурысопряжения с двухпроводными каналамисвязиЦелью изобретения является расширение области применения преобразователя за счет преобразования последовательности однополярных сигналов,закодированных длительностью импульсов., На фиг.1 приведена блок-схемапреобразователя; на фиг,2 - временные диаграммы, поясняющие его работу.Преобразователь содержит первый -четвертый элементы И 1 - 4, первый5 и второй 6 триггеры, первый - третий счетчики 7 - 9, элемент ИЛИ 10,первый элемент НЕ 11, генератор 12импульсов, регистр 3 сдвига, третийтриггер 14, пятый - седьмой элементыИ 15 - 17, второй элемент НЕ 18 и 25четвертый счетчик 19,На фиг.1 позициями 20, 21 и 22обозначены соответственно первый -третий информационные входы преобразователя, позициями 23 и 24 - соответственно информационный выход ивыход разрешения считывания преобразователя.На входе 2 обозначены: а - сигнална входе 22; б - сигнал на выходегенератора 12; в - сигнал напрямомвыходе триггера 14; г - сигнал навыходе элемента И 17; д - сигнал навыходе третьего элемента И 15; е -сигнал на прямом выходе триггера 5; 40ж " сигнал на прямом выходе триггера 6; з - сигнал на выходе элементаИЛИ 10; и, - сигнал на выходе элемента И 4; к - сигнал на выходе элемента И 16; л - сигнал на выходе элемента И 3.Преобразователь последовательногокода в параллельный работает следующим образом.В исходном состоянии сигналы свыхода генератора 12, поступают через элемент 3 на счетный вход счетчика 8, а все остальные счетчики9 и 19 и все триггеры 5,6 и 14 находятся в состоянии "О". Состояние регистра 3 может быть любым. Рабатапреобразователя заключается в преобразовании последовательно поступающих на его вход 22 информационных 11-разрядных байтов в параллельный код и формировании сигнала сопровождения параллельного кода на выходе счетчика 7.Для передачи каждого бита необходимо время, равное Т. Информационные байты, следуют друг эа другом через время й 3 2 Т.При поступлении первого бита "1" информационного байта на вход 22 преобразователя устанавливается в состояние "1" триггер 14, в результате чего начинает работать счетчик 19. Сигнал с первого счетчика 19 через элементы И 15 и 1 устанавливает в . состояние "1" триггер 5, после чего появляется сигнал на выходе элемента ИЛИ 10. Этот сигнал производит сдвиг информации в регистре 13, изменяет состояние счетчика 7 на единицу, устанавливает счетчик 8 в состояние "0" и вызывает работу счетчика9 под воздействием импульсов, посту"пающих на его счетный вход с выходагенератора 12 через элемент И 4,Триггер 14 ",озвращается в исходноесостояние 0 при появлении сигналан а втором выходе счетчика 1 9 , послечего сче тчи к1 9 также устанавливаетсяв состояние " 0" . Пр и работе счетчика9 появляется сигнал н а е го выходе длясброса триггеров 5 и 6 , после чегопрекращается сигнал н а выходе элемента 1 О , а сигнал с выхода элемента НЕ1 1 производит сброс счетчика 9 и р азрешает работу счетчика 8 до поступления следующе го би т а . При по ступлении н а вход 2 2 пр еобр аз о вателя второго бита 0 " работа триггера 1 4 и счетчика 1 9 повторяется однако сигнал с первого выхода счетчика 1 9 , пройдя элементы И 1 6 и 2, устанавливает в состояние " 1 " три ггер 6 , при э том сигнал с выхода элемента ИЛ1 0 производит те же действия , что и при поступлении н а вход 2 2 преобразователя бита " 1"При приеме последующих битов работа пр еобр азо ва" теля повторяется , однако в момент приема последнего одиннадцатого би т а информ ацн окно го байта н а выходе счетчика 7 вырабатывается сигнал сопр овож, де ния информации , введенной в регистр 1 3 . До по ступле ния ,н а вход 2 2 пре обр азо в ателя очередного информационного байта в результате работы счетчика 8 производится сброс счетчика 7 , при1462485 этом преобразователь возвращаетсяв исходное состояние. Формула и з о б р е т е н и я Ж 3 Составитель Б,ХодовТехред М,Ходанич Корректор О.Кравцова Редактор Л.Веселовскаящш т ШЕ е1 Ш Заказ 736/56 Тираж 879 Подписное ВНИИЛИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб., д. 4/5Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина,101 Преобразователь обеспечивает возможность преобразования информацион 5 ных байтов, биты "1" и 0" передаются с использованием однополярных сигналов соответственно большей и мень-. шей длительности, используемых в све товодных системах передачи данных. Преобразователь последовательного кода в параллельный по авт. св.9 115964, о т л и ч а ю щ и й с я тем, что, с целью расширения области применения преобразователя за счет преобразования последовательности однополярных сигналов, закодированных длительностью импульсов, в него введены третий триггер, пятый, шестой и седьмой элементы И, второй элемент НЕИ у у йбит 1 Бигт) О и четвертый счетчик, первый выход которого соединен с первыми, входами пятого и шестого элементов И, выходы которых соединены с вторымн входами соответственно первого и второго элементов И, второй выход четвертого счетчика соединен с входом сброса третьего триггера, прямой выход кото рого соединен с первым входом седьмого элемента И, выход которого соединен со счетным входом четвертого счетчика, инверсный выход третьего триггера соединен с входом сброса четвертого счетчика, выход второго элемента НЕ соединен с вторым входом шестого элемента И, второй вход седьмого элемента И подключен к выходу генератора импульсов, единичный вход третьего триггера, второй вход пятого элемента И и вход второго элемента НЕ объединены и являются третьим информационным входом преобразователя",Ф/Бил У

СмотретьЗаявка

4158641, 08.12.1986

ПРЕДПРИЯТИЕ ПЯ А-3706

ГЛАДКОВ ВЛАДИМИР ДМИТРИЕВИЧ, МАКУНИН ВИКТОР МИХАЙЛОВИЧ

МПК / Метки

МПК: H03M 7/00

Метки: кода, параллельный, последовательного

Опубликовано: 28.02.1989

Код ссылки

<a href="https://patents.su/3-1462485-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Преобразователь угла поворота вала в код с самоконтролем

Следующий патент: Преобразователь кодов

Случайный патент: Упаковка для текучего вещества