Дельта-кодер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

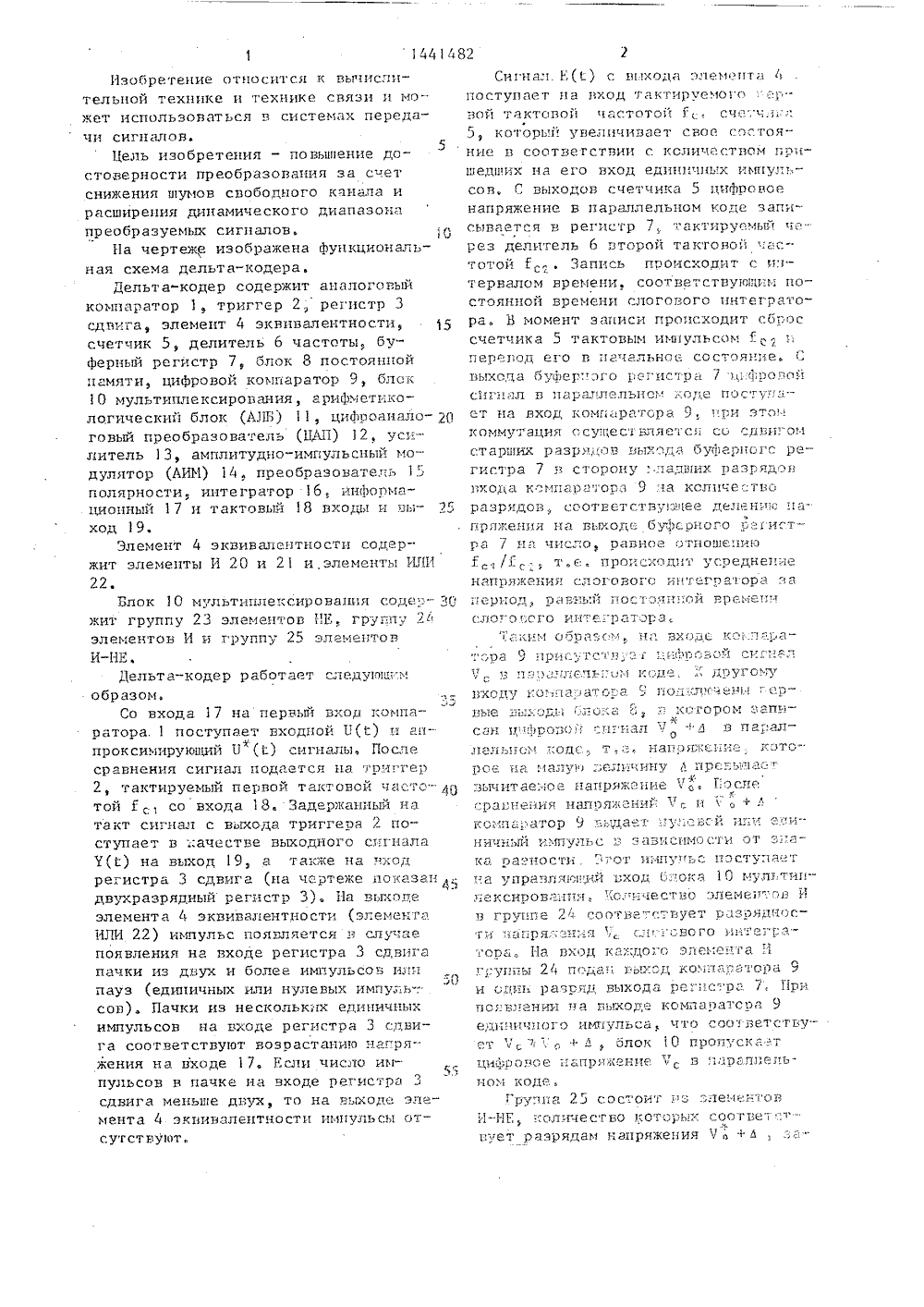

(51)4 Н 03 М 3/О ИТЕТ СССРЙ И ОТНРЫТИ ОСУДАРСТВЕННЫИ. Н ПО ДЕЛАМ ИЗОБРЕТЕ ПИСАНИЕ ИЗОБРЕТЕНИЯ ГА".:.7 У СВИДЕТЕЛЬСТВ Н АВТОРС повысить достовер-,ия за счет снижеого канала и расшиго диапазона преобДельта-кодер сокомпаратор 1, тригсдвига, элемент 4 счетчик 5, делитель ый регистр 7, блок ти, цифровой компамультиплекс ский блокованци 2 Б разователь силителя модулят олярност соответс ний в де ампли, пре- интегра ующей ор- а-кодере ь ее высокая достования. 1 ил. 12 1) 4263477/24-24(46) 30,11.88, Бкл. К 44 (71) Рижский политехнический институт им. А.Я.Пельше(57) Изобретение относится к вычисли тельной технике и технике связи. Его использование в системах передачи сигн алов по зволяе ность преобразова ния шумов свободн рения динамическо разуемых сигналов держит аналоговый гер 2, регистр 3 эквивалентности, б частоты, буферн .8 постоянной памя ратор 9, блок 10 арифметико-логиче роаналоговый прео годаря введению ч тудно-импульсного образователя 15 п тора 16, а также ганизации соедине обеспечивается бо верность преобразИзобретение относится к вьгислительной технике и технике связи и может использоваться н системах передачи сигналов.5Цель изобретения - повышение достоверности преобразования за счетснижения шумов снободного канала ирасширения динамического диапазонапреобразуемых сигналов,1На чертеже изображена функциональная схема дельта-кодера.Дельта-кодер содержит аналоговыйкомпаратор 1, триггср 2 регистр 3сдвига, элемент 4 эквивалентности,счетчик 5, делитель 6 частоты, буферный регистр 7, блок 8 постояннойпамяти, цифровой компаратор 9, блок10 мультиплексирования, ариф.ет,кологический блок (А 1 Пт) 11, цифроаналоговый преобразователь (ЦАП) 12, усилитель 13, амплитудно-импульсный модулятор (ЛИИ) 14, преобразователь 15полярности, интегратор 16, информационный 17 и тактовый 18 входы и ныход 19.Элемент 4 эквивалентности содержит элементы И 20 и 2 и,элементы ИЛИ22.Блок 10 мультиглессироваця соде.; - 3жит группу 23 элементов ИЕ, грунту 2элементоВ И и Группу 25 элементовИ - 1-1 Е.Дельта-кодер работает "чеду 1 тт,т мобразом,Со входа 17 на первый вхор компаратора. 1 поступает входцой 11(Г) и аппроксимируктций 11 (1:) сигналы, Послесравнения сигнал подается ца тряггер 2, тактируемый п ернои тактовой частс - 0 той Ест со входа 18. Задержанный нд такт сигнал с выхода. триггера 2 поступает вачестве выходного сигнала (С) на выход 19, а также на вход регистра 3 сдвига (ца чертеже показан ., двухразрядный регистр 3). Иа ньгхоце элемента 4 эквивалентности (элеменга или 22) импульс появляется В слтчае появления на входе регистра 3 сдвига пачки из Двух и более импульсон иХН50 пауз (единичных или нулевых импуль-. сон). Пачки из несколькпх единичных импульсов на входе регистра 3 сдвига соответстнуот нозрастанито напря женин на входе 17, Если число импульсов н пачке на входе регистра 3 сдвига меньше двух то на выхоЕте элемента 4 эквивалентности импульсы отсут ст нуот. Сигнал. Е(.) с выхода элеметтапоступает ца вход тдктируемого ,:рной тактовой чдстотой 1 ст сче.;.-а 5, который увеличивает свое состоя- НИС". Н СООТНР ГСТНИИ С КОЛИТЕ СТНОМ ПНИшедших на его вход едицичць.х импул -сов, С выходов счетчика 5 цифровоенапряжение в параллельном коде записывается в регистр 7, тактируемый через делитель 6 второй тактонои т;дстотой ГЗапись происходит с .1- терналом времени. соответстнука 1: постоянной времени слогового интегратора3 мОМРнт 3 писи ГроисхОДит сброс счетчика 5 тактовым имульсом сс; 1, и ЕРЕ 11 ОД ЕГО И П ДЧаЛЬНО Е СО СТОЯНИЕ.1 тыхода тт "ттеР:.ОГО Регисгад 7 ттт фтдопой сгнал в паралельцо 1 .:о .:,е посгугд - ст на ВхОд 1 сомп,раторд. 9, 11;и зтот коммутация осу;ес 1 нпяетсп со ивигом старих разр 511 он 1 тыходд бу 1 терцос регистра 7 ц сторону ",адих разрядон входа компанаторэ 9 а колцче твс,Стазр 5 дов, ссотнетствушт 1 ее делен,1.11 Напряжения ца выходе буферного т 1 истРД I Ца ЧИСЛО, РаННОЕ ОГЦОТ 11 Е 1 Дгс/- с: , .т, с 1, происходит усредне 1.-е ННПРЯжЕНИЯ СЛОГОВОГО 51ттт аОРа З Д. : ЕРИОД, РДННЬй ПОСТОЯЦ 1:Ой ВРЕМЕ тЛОтТ "С 1 О 11.ТЕГтатоРД,ГПСИ, Обттт,ЗСМ, Н; НХОПС. КО.т=. дт.-.",."ГЕЛЬ:. С:С.:ДТЕ ДТОУГОГ ВХОПУ :О:Д татс-,.а: ОП.СГЦСЧЕ 1 ТЬ - С:РВЫЕ НЬ;.ОД .Тто.Д., ПКОГОРОМ ЗаПИ- сдн 1 тг т 1 тровот" 1 тт татт ,т н и а;дтт- .ЕГЬО КОДС, т,:, НаПР 5 ТТС;Ие КЗТТО. - Рсс Н.та"тт.т . Р 11 П 1 ТУ Т ПРС;,аа;.т 3 ЫЧИТ аЕ: О Е ЦаПР 51 тд 1 Е тт, Г: О СПР Сратнтня 1 ВПтдя;ЕИИТ 1 с И+ Лтт1- 1 атор 9 аг5 тттттт,й т:тПЧ тТЬС1 вт СПМОСТИ От З"Д - СЙ ОаРНОСТИ ГОТ ИМПУтЬС ПЭСГтслант та упрет.,Л 5;,;1 Сй ХОД ; ,т Кд 1 0 туЛттц- ЛЕКСИСТОВа;И 5 То,тиЧЕСТВОтЕМЕ;т. - ,В И в Группе 2-. СоотР-.свует р.1 зряпнт)с- Гт тт 1 Ч 15 П "ЯО ГО И "ГД" . Ора, 1 а вход сат;цого э 5 е 1 е:тга тс 1т угттТЫ 2 Т Пт-,;а;:; НЬ: .":Т ;О"1;Тд,-,дтОТТа к Оди 1: 1 аряд Выхода регцттрс. /При по 1:в.енин та выходе компаратсра 9 Е; 1;11111 ТГО 1 М 1 ттЛЬ а Ч ГО СООтт НЕ ГС ГЬУЕТ , - т+ Л блотС 10 ПроцтСа ".ГттТП,фРОТОЕгТТТ;,(аИР тт, В ПНДПЕПТТ.о 1 Код 1 ру.тпа 2 т с:остоит из зле 1 ментов 11-11 Е кс 1 л 1 гчество соторьх соо Гнет .тч 1;ттЕТ раэрядам НалряжЕцияо + Л:,:г1444 аж 929 Подписное Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4 нис;нного в блок 8, Па один из входов каждого элемента ИЕ заведен выход компаратора 9, а на второй вход - разряд цифрового напряжения Ъ + Л, проинвертировапного элементом ПЕ5 группы 23. При поступлении с выхода компаратора 9 нулевого импульса, что соответствует 7Ч о + д, на выходесгруппы 25 элементов И-ИЕ появляется двоичное напряжение 7 + Л в параллельном коде, что делается с целью задания минимального напряжения Ъ + +3 , ниже которого не может быть напряжения Ч слогового интегратора, . при этом (при дальнейшем вычитании 7 с - 7) разность Ъс - Чвсегда по - ложительная. Такая операция устраняет пульсации на выходе слогового интегратора (т.е. счетчика 5, делителя 2 О 6 и регистра 7).С выходов блока 10 на первый вход ЛЛБ 11 поступает цифровой сигнал Ъ с 3 Ч .ь а, Па вторые входы АЛБ 11 заведены вторые выходы блока 8, где 25 в параллельном коде записано вычиты+ваемое напряжение 7,. Это напряжение вычитается с целью повышения степени сжатия динамического диапазона.разность 7 с - о с выходов ЛЛБ 11 ЗОв параллельном коде подается на входыЦАП 12, где греобразуется в аналоговое напряжение ", г. - Ч и, пройдя через усилитель 13, умножается на коэфФициент К., усиления, Полученное напряжение К(Ч- Ч ) поступает напервый вход АИ 11 14, на второй входкоторого подается выходной сигнал7(в). С выхода АИИ 14 сигнал 7 самплитудой, измененной в соответствии 40с уровнем К, (Ъс - Ч), постугает навход преобразователя 15 полярности,С его выхода двухполярное напряжениеЧ поступает на вход интегратора16 формирующего ступеньку аппроксимирующего напряжения П (С), поступающего на второй вход компаратора 1,Таким образом, в дельта-кодереобеспечивается сжатие динамическогодиапазона и уменьшение шумов свободйого канала в режиме холостого хода,благодаря чему повышается достоверность преобразования,Ф о р м у л а изобретения Дельта-кодер, содержащий аналогоьь:й компаратор, первый вход которого ВБ 111 ПИ Заказ 6296/57 Тир82является информационным вхолом дельта-кодера, выход соединен с информационным входом триггера, выход которого подключен к информационному входу регистра сдвига и является выходом дельта-кодера, тактовый вход регист - ра сдвига объединен с тактовым входом триггера и входом делителя частоты и является тактовым входом дельта-кодера, прямые и ийзер"ные выходы разря-, дов регистра сдвига соединены с пер- выми и вторыми входами элемента эквивалентности, выход которого подключен к счетному входу счетчика, буФерный регистр, блок постоянной памяти, первые выходы которого соединены с первыми входами цифрового компаратора, блок мультиплексирования арифметико-логический блок и цифроаналоговый преобразователь, о т л и ч а ю щ и й с я тем, что, с целью повышения достоверности преобразования за счет снижения шумов свободного канала и расширения динамического диапазона преобразуемых сигналов, в дельта кодер введены усилитель и последовательно соединенные амплитудно- импульсный модулятор, преобразователь полярности и интегратор, выход которого подключен к второму входу англогового компаратора, выход делителя частоты соединен с тактовым входом буферного регистра и входом обнуления счетчика, тактовый вход которого подключен к тактовому входу дсльтакодера, выходы счетчика .-. единены с информационными входами буферного регистра, выходы которого подключены к первым информационнымвходак блока мультиплексирования и соответствующим вторым входам цифрового компаратора, выход которого соединен с управляющим входом блока мультиплексирования вторые информационные входы которого подключены к первым выходам блока постоянной памяти, выходы блока мультиплексирования и вторые выходы блока постоянной памяти соединены с первыми и вторыми входами арифметико-логического блока, выходы которого подключены к входам цифроаналогового преооразователя, выход которого через усилитель соединен с первым входом амплитудно-импульсного модулятора, второй вход которого подключен к выходу триггера.

СмотретьЗаявка

4263477, 17.06.1987

РИЖСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. А. Я. ПЕЛЬШЕ

КОТОВИЧ ГЛЕБ НИКОЛАЕВИЧ, ЗЫРЯНОВ МИХАИЛ ЮРЬЕВИЧ, РИМШ АЙВАР АНАТОЛЬЕВИЧ, ФЛЕЙШМАН ИГОРЬ ОСИПОВИЧ

МПК / Метки

МПК: H03M 3/02

Метки: дельта-кодер

Опубликовано: 30.11.1988

Код ссылки

<a href="https://patents.su/3-1441482-delta-koder.html" target="_blank" rel="follow" title="База патентов СССР">Дельта-кодер</a>

Предыдущий патент: Умножающий цифро-аналоговый преобразователь

Следующий патент: Устройство для кодирования информации

Случайный патент: Устройство для рихтовки железнодорожного пути