Кодер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1399894

Автор: Залманов

Текст

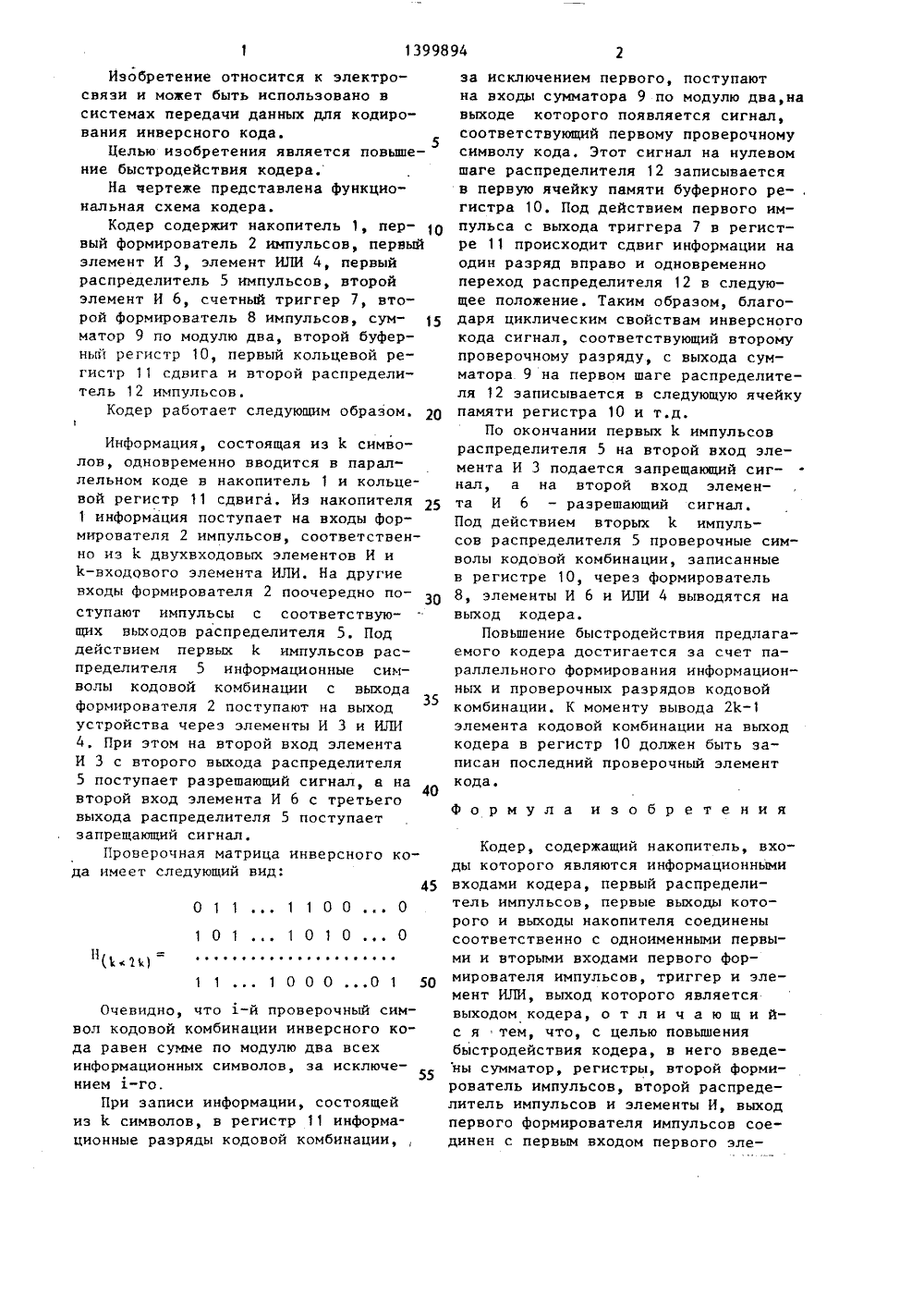

СОЮЗ СОЕЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК 894 1 ОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ПИСАНИЕ ИЭОБРЕТВТОРСНОМУ СВИДЕТЕЛЬСТВУ связи и мокет использоваться в системах передачи информации для кодирования инверсного кода. Изобретениепозволяет повысить быстродействие кодера эа сч вания инфо разрядов к содерзит н 2, 8 импул мент ИЛИ 4 рия и практикаих ошибки, М,ис 1,4.ельство СССР1 3/02, 1974. сов,ры 10 тносится к электро" ениИзобретение относится к электросвязи и может быть использовано всистемах передачи данных для кодирования инверсного кода.Целью изобретения является повышение быстродействия кодера.На чертеже представлена функциональная схема кодера.Кодер содержит накопитель 1, первый формирователь 2 импульсов, первый элемент И 3, элемент ИЛИ 4, первый распределитель 5 импульсов, второй элемент И 6, счетный триггер 7, второй формирователь 8 импульсов, сумматор 9 по модулю два, второй буферный регистр 10, первый кольцевой регистр 11 сдвига и второй распределитель 12 импульсов.Кодер работает следующим образом.Информация, состоящая из 1 символов, одновременно вводится в параллельном коде в накопитель 1 и кольцевой регистр 11 сдвига. Иэ накопителя 1 информация поступает на входы формирователя 2 импульсов, соответственно издвухвходовых элементов И и К-входового элемента ИЛИ. На другие входы формирователя 2 поочередно поступают импульсы с соответствующих выходов распределителя 5. Под действием первых 1 импульсов распределителя 5 информационные символы кодовой комбинации с выхода формирователя 2 поступают на выход35 устройства через элементы И 3 и ИЛИ 4, При этом на второй вход элемента И 3 с второго выхода распределителя 5 поступает разрешающий сигнал, а на второй вход элемента И 6 с третьего выхода распределителя 5 поступает запрещающий сигнал,Проверочная матрица инверсного кода имеет следующий вид:45О 1 11 1 О ОО1 О 11 О 1 ОО(Ъ с 2 с)1 11 О О О О 1 50Очевидно, что -й проверочный символ кодовой комбинации инверсного ко" да равен сумме по модулю два всех информационных символов, за исключением д-го.При записи информации, состоящей из 1 символов, в регистр 11 информационные разряды кодовой комбинации,за исключением первого, поступают на входы сумматора 9 по модулю два,на выходе которого появляется сигнал, соответствующий первому проверочному символу кода, Этот сигнал на нулевом шаге распределителя 12 записывается в первую ячейку памяти буферного ре-, гистра 10, Под действием первого импульса с выхода триггера 7 в регистре 11 происходит сдвиг информации на один разряд вправо и одновременно переход распределителя 12 в следующее положение, Таким образом, благодаря циклическим свойствам инверсного кода сигнал, соответствующий второму проверочному разряду, с выхода сумматора 9 на первом шаге распределителя 12 записывается в следующую ячейку памяти регистра 10 и т.д.По окончании первых 1 импульсов распределителя 5 на второй вход элемента И 3 подается запрещающий сигнал, а на второй вход элемента И 6 - разрешающий сигнал, Под действием вторых 1 импульсов распределителя 5 проверочные символы кодовой комбинации, записанные в регистре 10, через формирователь 8, элементы И 6 и ИЛИ 4 выводятся на выход кодера.Повышение быстродействия предлагаемого кодера достигается за счет параллельного формирования информационных и проверочных разрядов кодовой комбинации. К моменту вывода 2 Еэлемента кодовой комбинации на выход кодера в регистр 10 должен быть записан последний проверочный элемент кода.Формула изобретенияКодер, содержащий накопитель, входы которого являются информационными входами кодера, первый распределитель импульсов, первые выходы которого и выходы накопителя соединены соответственно с одноименными первыми и вторыми входами первого формирователя импульсов, триггер и элемент ИЛИ, выход которого является выходом кодера, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия кодера, в него введены сумматор, регистры, второй формирователь импульсов, второй распределитель импульсов и элементы И, выход первого формирователя импульсов соединен с первым входом первого эле% Редактор Е. Копча Заказ 2677/56 Тираа 928 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий113035, Москва, Ж, Раушская наб д, 4/5 Производственно-полиграфическое предприятие, г. Уагород, ул, Проектная, 4 мента И, выход которого соединен с первым входом элемента ИЛИ,входы триггера и первого распределителя импульсов объединены и являются син 5 хронизирующим,входом кодера, выход триггера соединен с тактовым входом первого регистра и входом второго распределителя импульсов, информационные входы первого регистра подлючены к одноименным информационным входам кодера, выходы первого регистра соединены с одноименными входами сумматора, выходы сумматора и второго распределителя импульсов соединены 15 соответственно с информационным и одноименными управляющими входамивторого регистра, выходы которогосоединены с одноименными первьаки входами второго формирователя импульсов,вторые входы которого подключены кодноименным первым выходам первогораспределителя импульсов, выход второго формирователя импульсов соединен с первым входом второго элемента И, выход которого соединен свторым входом элемента ИЛИ, второй итретий выходы первого распределителяимпульсов соединены с вторыми входамн соответственно первого и второгоэлементов И,

СмотретьЗаявка

4171128, 04.01.1987

ПРЕДПРИЯТИЕ ПЯ Р-6609

ЗАЛМАНОВ АЛЕКСАНДР ЛЕОНИДОВИЧ

МПК / Метки

МПК: H03M 13/05

Метки: кодер

Опубликовано: 30.05.1988

Код ссылки

<a href="https://patents.su/3-1399894-koder.html" target="_blank" rel="follow" title="База патентов СССР">Кодер</a>

Предыдущий патент: Устройство для исправления стираний

Следующий патент: Индукционная установка для нагрева железобетона

Случайный патент: Газоотвод доменной печи