Устройство для дифференцирования частоты повторения импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 525117

Автор: Чистяков

Текст

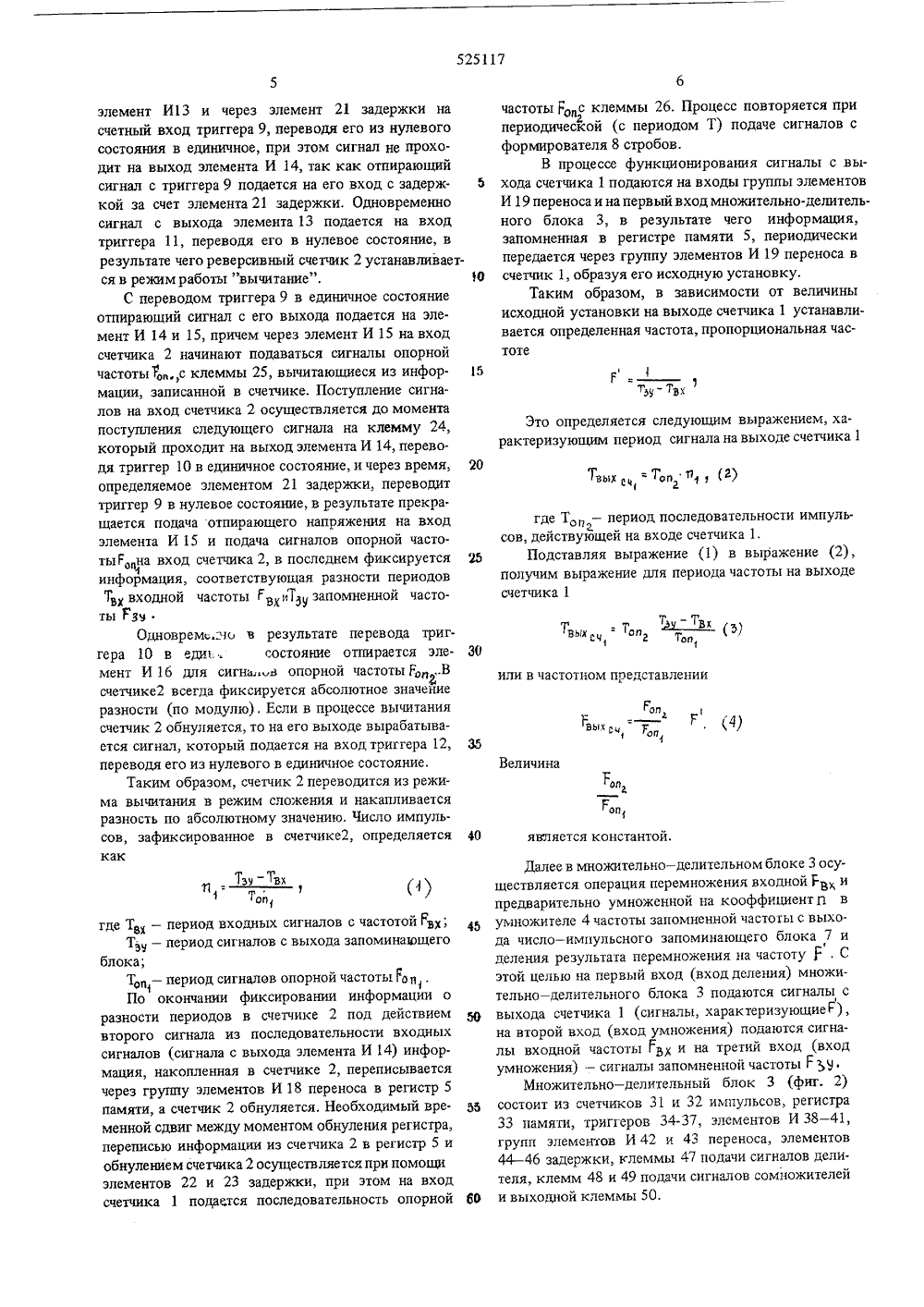

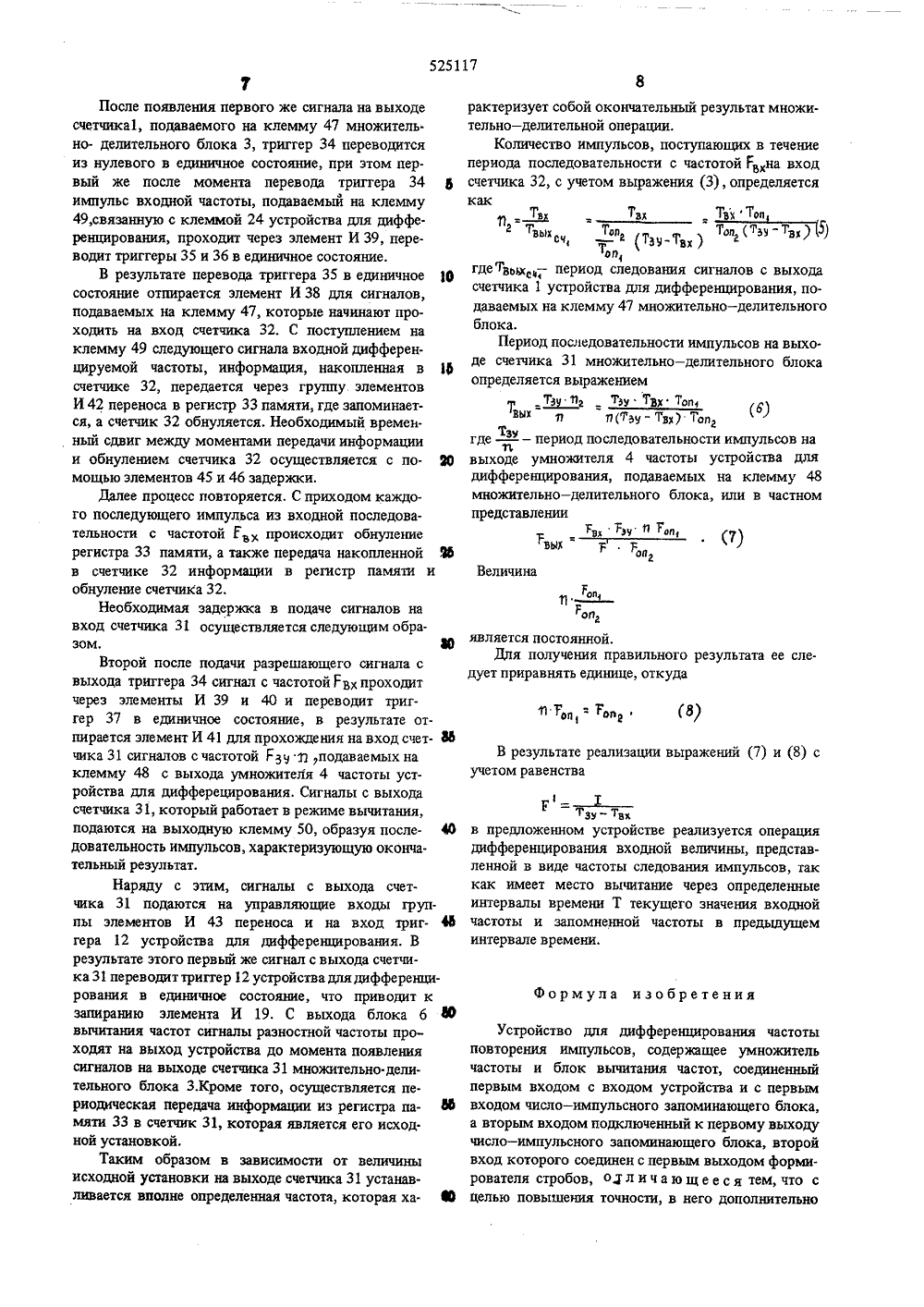

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советских Социалистических Республик(22) Заявлено 19.12.74 (21) 2086048/24с присоединением заявкиМ. Кл, 6 06 0 7/18 Государственный камитеСаввтв Министров СССРпа дедам нзааретеннйн открытий 23) Приоритет - 43) Опубликова 15.08.76. Бюллетень Ю) Дата опубликования описания 07.04.7 2) Автор изобретен В. Чистяков 1) Заявите 54) УСТРОЙСТВО ДЛЯ ДИ ПОВТОРЕНИЯавтоматики и , к устройстульсных сигн частностиот но - имп вычислительнои техники,вам дифференцирования чналов. имею пульсные дифференцижащие блоки вычитания версивные счетчики, умИзвестны частотно - и ующие устройства, содер частот, блоки задержки, р ожители и делители часто ы. Недостатком известны ниженное быстродействие определяемых постоянство ду входнои и задерж вательностями и нерав оследовательности имп дифферен- содержая частот,тва дляпульсов вычи таниодом уст ства оминаюенный к сного зап о ого зало соединен аю пер Изобретение относится к облас х устроиств является по и точность вычислений м величины сдвига меж иной импульсными последо номерностью самой выходно Кроме того, известны устроис цирования частоты повторения им щее множитель частоты и блок соединенный первым входом с вх с первым входом число - импул щего блока, а вторым входом первому выходу число - импульсы го блока, второй вход которого выходом формирователя стробов ЕРЕНЦИРОВАНИЯЧАСТОТЬИМПУЛЬСОВ днако известные устройства из - за неравнсти выходной последовательности импульсо пониженную точность вычислений. целью повышения точности вычислений предлагаемое устроиство дополнительно введенъ логические элементы И, ИЛИ, элементы задержки, триггеры управления, счетчики, регистр и множительно - делительный блок, выход которого соединен с входом выходного элемента ИЛИ, подкг эчен ного вторым входом к выходу первого элемента И,соединенного одним входом с выхоцом блока вычитания частот, другим входом - с выходом первого триггера управления, подключенного входом к первому выходу множительно - делительного бло ка, и соединенного третьим входом с входом запуска устройства, первым входом второго элемента И и первым входом формирователя стробов, второй вход которого соединен с первым входом третьего элемента И и третьим входом число - импульсного р) запоминающего блока, подключенного вторым выходом к поразрядным входам первого счетчика, счетный вход которого соединен с выходом третьего элемента И, подключенного вторым входом к первому входу четвертого элемента И н выходу 25 второго триггера управления, вход которого черезпервый элемент задержки соединен с первым входом третьего триггера управления и выходом пятого элемента И, подключенного входами соответственно к входу устройства и второму выходу формирователя стробов, причем второй вход третьего ьтриггера управления, соединенного выходами свходами управления реверсом первого счетчика,подключен к выходу этого счетчика, поразрядныевыходы которого через первую группу элементов Ипереноса соединены с входами регистра, выходы которого через вторую группу элементов И переноса соединены с поразрядными входами второго счетчика, подключенного выходом к управляющему входу второйгруппы элементов И переноса и первому входу множительно-делительного блока, второй вход которого ,бсоединен с вторым входом четвертого элемента И,подключенного выходом к выходу четвертого триггера управления, входу обнуления регистра, и черезвторой и третий элементы задержки соответственнок входу обнуления первого счетчика и управляющему 20входу первой группы элементов И переноса, а третийвход множительно-целительного блока подключен через умноютельч частоты к первому выходу число-импульсного запоминающего блока, причем выходчетвертого триггера управления соединен с вторым 25входом второго элемента И, подключенного выходом к счетному входу второго счетчика,На фиг, 1 представлена функциональная схемапредлагаемого устройства; на фиг, 2 - схемаъпюжительно делительного блока. 30Устройство состоит из счетчиков 1 и 2 импульсов, множительно - делительного блока 3, умножи.тел я 4 частоты, регистра 5, блока 6 вычитания частот,число-импульсного запоминающего блока 7, формирователя 8 стробов, триггеров 9 - 12 управления, я 5элементов И 13 - 17, групп элементов И 18 и 19переноса, элемента ИЛИ 20, элементов в 21 - 3 за.держки, клеммы 24 подачи входных сигналов,клемм 25 и 26 подачи сигналов опорных частот, клеммы 27 подачи сигнала разрешения, выходной клемы т 4928 и клемм 29 и 30 выдачи знака производной.Сигналы дифференцируемой последовательности импульсов с частотой ",родаются на клемму 24, на первый вход число - импульсного запоминающего блока 7, на первый вход блока 6 вычитания 45 частот и на второй вход множительно-дслительного блока 3. Сигналы опорных частот Р,и Еподаются соотвектвенно на клеммы 25 и 6.В исходном состоянии счетчики, регистр и триггеры обнулены. В момент гна клемму 27 пода- Я 3 ется сигнал разрешения, который далее подается на входы элементов И 18 и 19 и на первый вход формирователя 8 стробов, периодически вырабатывающего сигналы на своих выходах с периодом Т, которые подаются на вход элемента И 13 ина 55 второй вход число - импульсного запоминающего блока 7, причем первый сигнал после момента ь с выхода формирователя 8 стробов подается только на вход число - импульсного запоминающего блока 7, бО С подачей указанного сигнала на вход блока 7под действием первого же сигнала входной дифференцируемый последовательности с частотой Г внем осуществляется запись и запоминание информации о периоде входной частоты в данный моментвремени, а также преобразование запомненной информации в частоту следования импульсов, которые непрерывно подаются на входы блока 6 вычитания частот и умножителя 4 частоты. Указанныеоперации производятся в запоминающем блоке путем подсчета импульсов опорной частоты о с по.мощью счетчика в течение периода сигналов вход.ной частоты, последующей передачи, полученной всчетчике информации в регистр памяти, переводасчетчика в режим работы "вычитание" и периодической записи информации в счетчик из регистрапамяти выходными сигналами и ее считывания,Таким образом, на выходе счетчика имеет место последовательность импульсов с периодом, соответствующим запомненной информации, а в регистре памяти - запомненная информация в кодовомпредставлении.Поскольку после подачи сигнала разрешениярезультирующая последовательность на выходемножительно - целительного блока появляется с некоторой задержкой, то до появления этой последо.вательности на вход выходного элемента ИЛИ 20подается через элементИ 19 с выхода блока 6вычитания частот последовательность неравномерной разностной частоты между входной частотойг, и запомненной в блоке 7. Блок вычитанияЮчастот может быть выполнен на триггере и двухэлементах И 13 - 17. выходы которых соединены свходами элемента ИЛИ 20, а входы подключены ксоответствующим выходам триггера, к клеммампода пи первой и второй последовательности и черезэлементы задержки - к соответствующим входамтриггера, при этом знак разности (производной)фиксируется на клеммах 29 и 30. Управление подачей указанной последовательности на выход устройства осуществляется сигналами разрешения (склеммы 27) и с выхода триггера 12, запрещающегопрохождение сигналов с выхода блока 6 вычитанияпри появлении первого же сигнала на выходе множительно делительного блока 3,Работа основного тракта дифференцированияосуществляется следующим образом.При подаче следующего второго сигнала с выхода формирователя 8 стробов он подается на входблока 7, а также на вхоц элемента И 13, при этомвыдается запомненная в блоке 7 информация впараллельном коде на счетчик 2 и запись в запоминающий блок текущего значения периода частотывходных сигналов,В счетчике 2 вычитается информация о периодезапомненной частоты и периоде текущего значениячастоты, что производится следующим образом.Первый после момента подачи сигнала с выходаформирователя 8 стробов импульс входной частоты, подаваемый на клемму 24, проходит через525117 элемент И 13 и через элемент 21 задержки на счетный вход триггера 9, переводя его из нулевого состояния в единичное, при этом сигнал не проходит на выход элемента И 14, так как отпирающий сигнал с триггера 9 подается на его вход с задержкой за счет элемента 21 задержки. Одновременно сигнал с выхода элемента 13 подается на вход триггера 11, переводя его в нулевое состояние, в результате чего реверсивный счетчик 2 устанавливае ся в режим работы "вычитание".С переводом триггера 9 в единичное состояние отпирающий сигнал с его выхода подается на элемент И 14 и 15, причем через элемент И 15 на вход счетчика 2 начинают подаваться сигналы опорной частоты Ур,с клеммы 25, вычитающиеся из информации, записанной в счетчике. Поступление сигналов на вход счетчика 2 осуществляется до момента поступления следующего сигнала на клемму 24, который проходит на выход элемента И 14, переводя триггер 10 в единичное состояние, и через время, определяемое элементом 21 задержки, переводит триггер 9 в нулевое состояние, в результате прекращается подача отпирающего напряжения на вход элемента И 15 и подача сигналов опорной часто- тыГ на вход счетчика 2, в последнем фиксируетсярвинформация, соответствующая разности периодов Тв входной частоты ГвИТу запомненной частоты ГЗзОдноврем, чо в результате перевода триггера 10 в един, состояние отпирается элемент И 16 для сигнв, н опорной частоты Рр,1,.В счетчике 2 всегда фиксируется абсолютное значениеоп" разности (по модулю). Если в процессе вычитания счетчик 2 обнуляется, то на его выходе вырабатывается сигнал, который подается на вход триггера 12, переводя его из нулевого в едининое состояние.Таким образом, счетчик 2 переводится из режима вычитания в режим сложения и накапливается разность по абсолютному значению, Число импульсов, зафиксированное в счетчике 2, определяется как т 15 20 Твых="рп т у2 вылал-- 1)- 1 вк сч, 2 ТолВеличина 40 является константой. Далее в множительно - делительном блоке 3 осуществляется операция перемножения входной Ри предварительно умноженной на кооффициент и в умножителе 4 частоты запомненной частоты с выхода число - импульсного запоминающего блока 7 иделения результата перемножения на частоту 1., С этой целью на первый вход (вход деления) множительно - целительного блока 3 подаются сигналы с Эъ выхода счетчика 1 (сигналы, характеризующиеся),на второй вход (вход умножения) подаются сигналы входной частоты Г и на третий вход (вход умножения) - сигналы запомненной частоты г у.Множительно - делительный блок 3 (фиг. 2) Ь состоит из счетчиков 31 и 32 импульсов, регистра33 памяти, триггеров 34-37, элементов И 38 - 41, групп элементов И 42 и 43 переноса, элементов 44 - 46 задержки, клеммы 47 подачи сигналов делителя, клемм 48 и 49 подачи сигналов сомножителей бО и выходной клеммы 50.Тргде Тат - период входных сигналов с частотой Рвх,Тз - период сигналов с выхода запоминающего блока;Тр - период сигналов опорной частоты гр я, По окончании фиксировании информации о разности периодов в счетчике 2 под действием второго сигнала из последовательности входных сигналов (сигнала с выхода элемента И 14) информация, накопленная в счетчике 2, переписывается через группу элементов И 18 переноса в регистр 5 памяти, а счетчик 2 обнуляется. Необходимый временной сдвиг между моментом обнуления регистра, переписью информации из счетчика 2 в регистр 5 и обнулением счетчика 2 осуществляется при помощи элементов 22 и 23 задержки, при этом на вход счетчика 1 подается последовательность опорной частоты гопс клеммы 26. Процесс повторяется при"Япериодической (с периодом Т) подаче сигналов сформирователя 8 стробов.В процессе функционирования сигналы с выб хода счетчика 1 подаются на входы группы элементовИ 19 переноса и на первый вход множительно-делительного блока 3, в результате чего информация,запомненная в регистре памяти 5, периодическипередается через группу элементов И 19 переноса в Ю счетчик 1, образуя его исходную установку.Таким образом, в зависимости от величиныисходной установки на выходе счетчика 1 устанавливается определенная частота, пропорциональная час- тоте Это определяется следующим выражением, характеризующим период сигнала на выходе счетчика 1 где Тр и - период последовательности импуль.мсов, действующей на входе счетчика 1.26 Подставляя выражение (1) в выражение (2),получим выражение для периода частоты на выходесчетчика 1 или в частотном представленииПосле появления первого же сигнала на выходесчетчика 1, подаваемого на клемму 47 множительно- делительного блока 3, триггер 34 переводитсяиз нулевого в единичное состояние, при этом первый же после момента перевода триггера 34импульс входной частоты, подаваемый на клемму49,связанную с клеммой 24 устройства для дифференцирования, проходит через элемент И 39, переводит триггеры 35 и 36 в единичное состояние.В результате перевода триггера 35 в единичное 19состояние отпирается элемент И 38 для сигналов,подаваемых на клемму 47, которые начинают проходить на вход счетчика 32. С поступлением наклемму 49 следующего сигнала входной дифференцируемой частоты, информация, накопленная в фсчетчике 32, передается через группу элементовИ 42 переноса в регистр 33 памяти, где запоминается, а счетчик 32 обнуляется, Необходимый временный сдвиг между моментами передачи информациии обнулением счетчика 32 осуществляется с помощью элементов 45 и 46 задержки.Далее процесс повторяется, С приходом каждого последующего импульса из входной последовательности с частотой Гвх происходит обнулениерегистра 33 памяти, а также передача накопленнойв счетчике 32 информации в регистр памятиобнуление счетчика 32,Необходимая задержка в подаче сигналов навход счетчика 31 осуществляется следующим образом. 30Второй после подачи разрешающего сигнала свыхода триггера 34 сигнал с частотой ГВх проходитчерез элементы И 39 и 40 и переводит триггер 37 в единичное состояние, в результате отпирается элемент И 41 для прохождения на вход счетчика 31 сигналов с частотой Г у г 1,подаваемых наклемму 48 с выхода умножителя 4 частоты устройства для дифферецирования. Сигналы с выходасчетчика 31, который работает в режиме вычитания,подаются на выходную клемму 50, образуя последовательность импульсов, характеризующую окончательный результат. Фби Наряду с этим, сигналы с выхода счетчика 31 подаются на управляющие входы группы элементов И 43 переноса и на вход триг гера 12 устройства для дифференцирования. В результате этого первый же сигнал с выхода счетчика 31 переводит триггер 12 устройства для дифференцирования в единичное состояние, что приводит к запиранию элемента И 19, С выхода блока 6 Ю вычитания частот сигналы разностной частоты проходят на выход устройства до момента появления сигналов на выходе счетчика 31 множительно.дели- тельного блока З.Кроме того, осуществляется периодическая передача информации из регистра па мяти 33 в счетчик 31, которая является его исходной установкой,Таким образом в зависимости от величины исходной установки на выходе счетчика 31 устанавливается вполне определенная частота, которая ха-следовательности импульсов на выхо множительно - делительного блока де счетчик определяется выражением7:Ъ Л 2 - ГвУВх опщх г л(тву - вх) То 1где -- период последовательности иЗУвыходе умножителя 4 частоты устрдифференцирования, подаваемых намножительно-делительного блока, илпредставлениив Ъопвых роа 2 мпульсов на ойства для клемму 48 и в частном 7) личина оуод2 является постояннои. Для получения правильного результата ее слдует приравнять единице, откуда оп," оду В результате реализации выражений (7) и (8) сетом равенства 1 зу твв предложенном устройстве реализуется операция дифференцирования входной величины, представленной в виде частоты следования импульсов, так как имеет место вычитание через определенные интервалы времени Т текущего значения входной частоты и запомненной частоты в предыдущем интервале времени,Формула изобретения Устройство для дифференцирования частоты повторения импульсов, содержащее умножитель частоты и блок вычитания частот, соединенный первым входом с входом устройства и с первым входом число - импульсного запоминающего блока, а вторым входом подключенный к первому выходу число-импульсного запоминающего блока, второй вход которого соединен с первым выходом формирователя стробов, М л и ч а ю щ е е с я тем, что с целью повышения точности, в него дополнительно рактеризует собой окончательный результат множительно - делительной операции.Количество импульсов, поступающих в течение периода последовательности с частотой Гвна вход счетчика 32, с учетом выражения (3), определяется как вл 1 вх ТвхТо 7 ввх Топ Тол (зу-гвх) З сч - 2 (Тзу-Гвх )"оп гдеТВыд- , период следования сигналов с выхода счетчика 1 устройства для дифференцирования, подаваемых на клемму 47 множительно - делительного блока.Период повведены логические элементы И, ИЛИ, элементы задержки, триггеры управления, счетчики, регистр и множительно - делительный блок, выход которого соединен с входом выходного элемента ИЛИ, подключенного вторым входом к выходу первого элемента И, соединенного одним входом с выходом блока вычитания частот, другим входом - с выхо Йдом первого триггера управления, подключенного входом к первому выходу множительно - делитель- ного блока, и соединенного третьим входом с входом запуска устройства, первым входом второго элемента И и первым входом формирователя стробов, второй вход которого соединен с первым входом третьего элемента И и третьим входом число в импульсно запоминающего блока, подключенного вторым выходом к поразрядным входам первого счетчика, счетный вход которого соединен с выходом третьего элемента И, подключенного вторым входом к первому входу четвертого элемента И и выходу второго триггера управления, вход которого через первый элемент задержки соединен с первым входом третьего триггера управления и выходом пятого элемента И, подключенного входами соответственно к входу устройства и второму выходу формирователя стробов, причем второй вход третьего триггера управления, соединенного выходами с входами управления реверсом первого счетчика, подключен к выходу этого счетчика, поразрядные выходы которого через первую группу элементов И переноса соединены с входами регистра, выходы которого через вторую группу элементов И переноса соединены с поразрядными входами второго счетчика, подключенного выход дом к управляющему входу второй группы элементов И переноса и первому входу множительно - делительного блока,второй вход которого соеди.нен с вторым входом четвертого элемента И, подключенного выходом к входу четвертого триггера 1 я управления, входу обнуления регистра, и черезвторой и третий элементы задержки соответственно к входу обнуления первого счетчика и управляющему входу первой группы элементов И переноса, а третий вход множительно - делительного блока под.39 ключен через умножитель частоты к первому выходу число - импульсного запоминающего блока, причем выход четвертого триггера управления соединен с вторым входом второго элемента И, подключен.ного выходом к счетному входу второго счетчика,525117 Составитель И. ШепиловаТехред О. Луговая Корректор Н. Бугакова Редактор Т, Янова Заказ Филиал ППП" Патент ", г. Ужгород, ул. Проектная, 4 5091/591 Тираж 864 Подписное ЦНИИПИ Государственного Комитета Совета Министров СССР но делам изобретений и открытий 113035, Москва, Ж - 35, Раушская наб., д. 4/5

СмотретьЗаявка

2086048, 19.12.1974

ПРЕДПРИЯТИЕ ПЯ А-1923

ЧИСТЯКОВ БОРИС ВИКТОРОВИЧ

МПК / Метки

МПК: G06G 7/18

Метки: дифференцирования, импульсов, повторения, частоты

Опубликовано: 15.08.1976

Код ссылки

<a href="https://patents.su/6-525117-ustrojjstvo-dlya-differencirovaniya-chastoty-povtoreniya-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для дифференцирования частоты повторения импульсов</a>

Предыдущий патент: Частотный интегратор

Следующий патент: Устройство для дифференцирования

Случайный патент: Способ получения биметаллов