D-триггер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

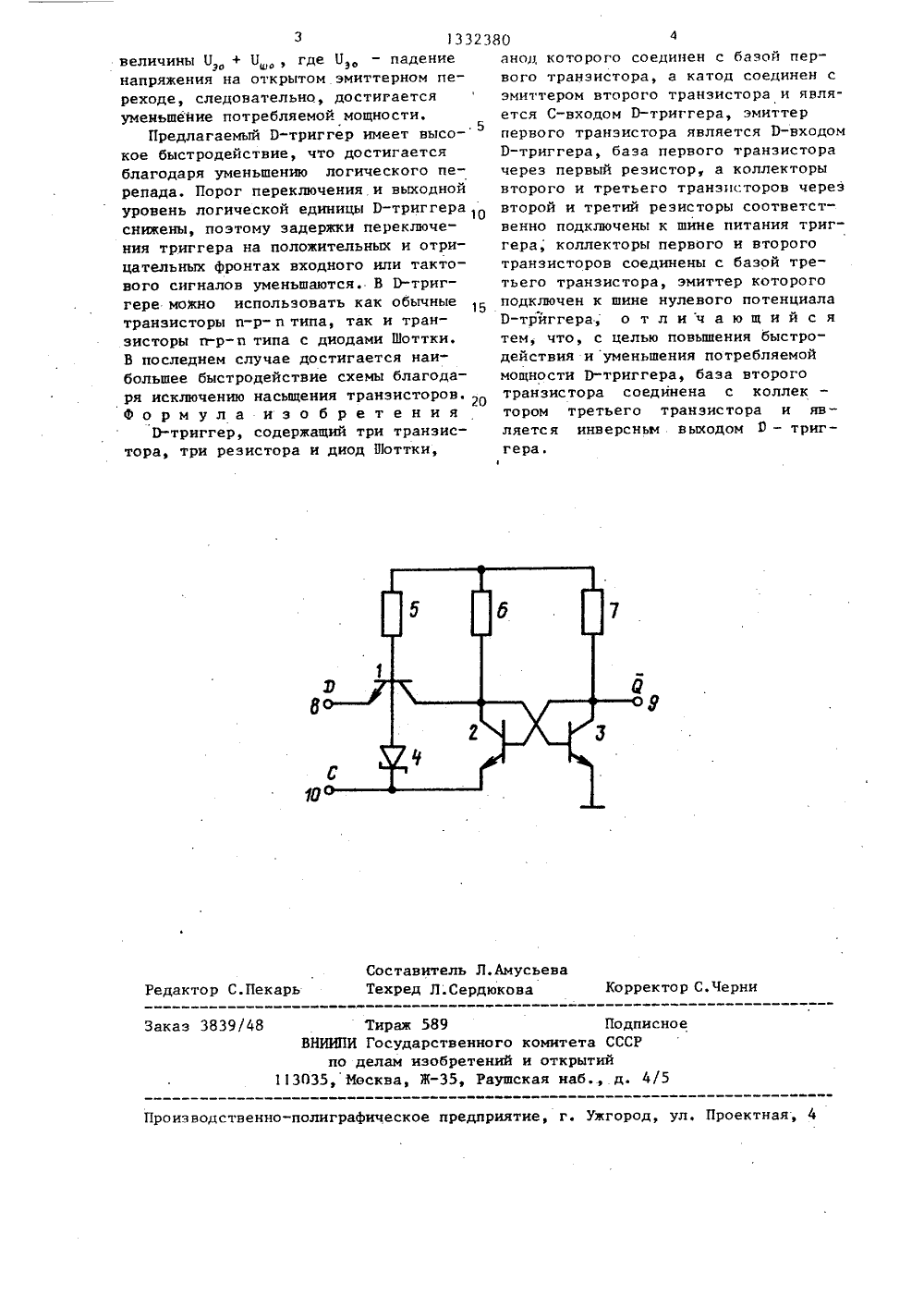

Изобретение относится к вычислительной технике и предназначено дляиспользования в интегральных логических микросхемах цифровых ЭВМ.Цель изобретения " снижение потребляемой мощности и повьшение быстродействия триггера.На чертеже изображена принципиальная схема П-триггера.0-триггер содержит три транзистора 1-3, два из которых 2 и 3 образуютбистабкпьную ячейку, диод Ноттки 4 итри резистора 5-7, база первого транзистора 1 через токоограничительныйпервый резистор 5, а коллекторы второго 2 и третьего 3 транзисторов бистабильной ячейки через нагрузочные(второй и третий) резисторы 6 и 7 соответственно соединены с шиной питания, эмиттер транзистора 1 является0-входом 8 Э-триггера, коллектортранзистора 1 соединен с базой третьего транзистора 3 бистабильнойячейки, коллектор которого являетсяинверсным выходом 9 В-триггера, эмиттер транзистора 2 бистабкпьной ячейки является тактовым входом 1 О 0 триггера, анод входного диода 4 Шоттки соединен с базой транзистора 1,а катод - с тактовым входом 10 Втриггера,база транзистора 3 бистабильной ячейки соединена с инверснымвыходом 9 П-триггера, а эмиттер транзистора 3 бистабильной ячейки соединен с общей шиной.Р-триггер работает следующим образом,Предположим, что на тактовыйвход 1 О подано напряжение логическойединицы 0", тогда диод 4 Шоттки закрыт при любом значении потенциала навходе 8 триггера и ток через него непротекает. Если на входе 8 триггераустановлен потенциал логической единицы П, то транзистор 1 находится винверсном режиме и его ток коллектора втекает в базу транзистора 3 и является достаточным для насыщениятранзистора 3, потенциал на коллекторе которого, т.е. на выходе 9 триггера, равен остаточному напряжениюПотенциал логической единицы с входатактового сигнала поступает также ииа эмиттер транзистора 2, поэтомутранзистор 2 выключен и его ток коллектора равен нулю.Если на вход 8 триггера подаетсяпотенциал логического нуля Уф, транс 10 15 20 25 30 35 40 45 50 55 зистор 1 насьпцается и на его коллекторе устанавливается потенциал Б + + У где 0 - падение напряжениякп э кнмежду коллектором и эмиттером насыщенного транзистора, Этот потенциал недостаточен для удержания транзистора 3 во включенном состоянии, поэтому он выключается и потенциал на его коллекторе увеличивается до уровня логической единицы 1, однако транзистор 2 по-прежнему закрыт и его ток коллектора равен нулю,Таким образом, при удержании потенциала логической единицы на тактовом входе 10 на выходе 9 триггера появляется потенциал логической инверсии входного сигнала.Пусть на тактовый вход 10 поданоонапряжение 1, диод Шоттки открывается и потенциал базы транзистора 1 уменьшается до величины У + Бщ ,гдео Цщ, - напряжение на открытом диоде Ноттки. Тогда независимо от величины входного сигнала на эмиттере транзистора 1 на базе этого транзистора сохраняется низкий потенциал Б + ц недостаточный для отпирания транзистора 1, поэтому коллекторный ток транзистора 1 равен нулю. Потенциал эмиттера транзистора 2 равен 1 поэтому если потенциал на выходе триггера равен Б, то в базу транзистора 2 втекает ток резистора 7, достаточный для насьпцения транзистора 2. На базе транзистора 3 устанавливается потенциало+ У,о недостаточный для отпирания транзистора 3, поэтому на выходе триггера сохраняется высокий потенциал У = У + 09,. Если же на выходе тригогера было напряжение логического нуОля О, то транзистор 2 остается закрытым, так как напряжение между его базой и эмиттером близко к нулю, а ток резистора 6 втекает в.базу транзистора 3 и достаточен для удержания его в насыщенном состоянии. При этом на выходе 9 триггера сохраняется потено.циал логического нуля, Следовательно, при удержании потенциала лоогического нуляна тактовом входе 1 О триггер сохраняет записанную ранее информацию.Таким образом, устройство, схема которого изображена на чертеже, функционирует как 0-триггер, тактируемый. уровнем логической единицы.Р-триггер работает при низких напряжениях источника питания вплоть доректор С.Черн Редактор С.Пек Тираж 589ИИПИ Государственногпо делам изобретений5, Москва, Ж, Рауш Заказ 3839 4 Подписноекомитета СССРи открытийкая наб , д. 4/5 лиграфическое предприятие, г. Ужгород, ул. Проектна Производственно з 3323 величины Б, + Пгде Б - падение напряжения на открытом эмиттерном переходе, следовательно, достигается уменьшение потребляемой мощности,5Предлагаемый Э-триггер имеет высо- кое быстродействие, что достигается благодаря уменьшению логического перепада. Порог переключения.и выходной уровень логической единицы Р-триггера снижены, поэтому задержки переключения триггера на положительных и отрицательных фронтах входного или тактового сигналов уменьшаются. В 0-триггере можно использовать как обычные транзисторы и-р-и типа, так и транзисторы и-р-и типа с диодами Шоттки, В последнем случае достигается наибольшее быстродействие схемы благодаря исключению насыщения транзисторов. Формула изобретенияО-триггер, содержащий три транзистора, три резистора и диод Шоттки,80 4анод которого соединен с базой первого транзистора, а катод соединен с эмиттером второго транзистора и является С-входом П-триггера, эмиттер первого транзистора является Р-входом Э-триггера, база первого транзистора через первый резистор, а коллекторы второго и третьего транзисторов через второй и третий резисторы соответственно подключены к шине питания триггера, коллекторы первого и второго транзисторов соединены с базой третьего транзистора, эмиттер которого подключен к шине нулевого потенциала П-триггера, о т л и ч а ю щ и й с я тем, что, с целью повышения быстродействия и уменьшения потребляемой мощности Э-триггера, база второго транзистора соединена с коллек тором третьего транзистора и яв - ляется инверсным . выходом Р - триггера.

СмотретьЗаявка

3931201, 12.07.1985

МОСКОВСКИЙ ИНЖЕНЕРНО-ФИЗИЧЕСКИЙ ИНСТИТУТ, ПРЕДПРИЯТИЕ ПЯ М-5769

ПАНФИЛОВ АРКАДИЙ ПАВЛОВИЧ, САВОТИН ЮРИЙ ИВАНОВИЧ, ШАГУРИН ИГОРЬ ИВАНОВИЧ

МПК / Метки

МПК: G11C 11/40

Метки: д-триггер

Опубликовано: 23.08.1987

Код ссылки

<a href="https://patents.su/3-1332380-d-trigger.html" target="_blank" rel="follow" title="База патентов СССР">D-триггер</a>

Предыдущий патент: Запоминающий элемент

Следующий патент: Регистр сдвига с самоконтролем

Случайный патент: Устройство для контроля громкоговорителей