Система электропитания электронно-вычислительной машины, включающей в себя процессор и узлы оперативной и долговременной памяти

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1290417

Авторы: Нестеренко, Пельтек, Попов, Редько

Текст

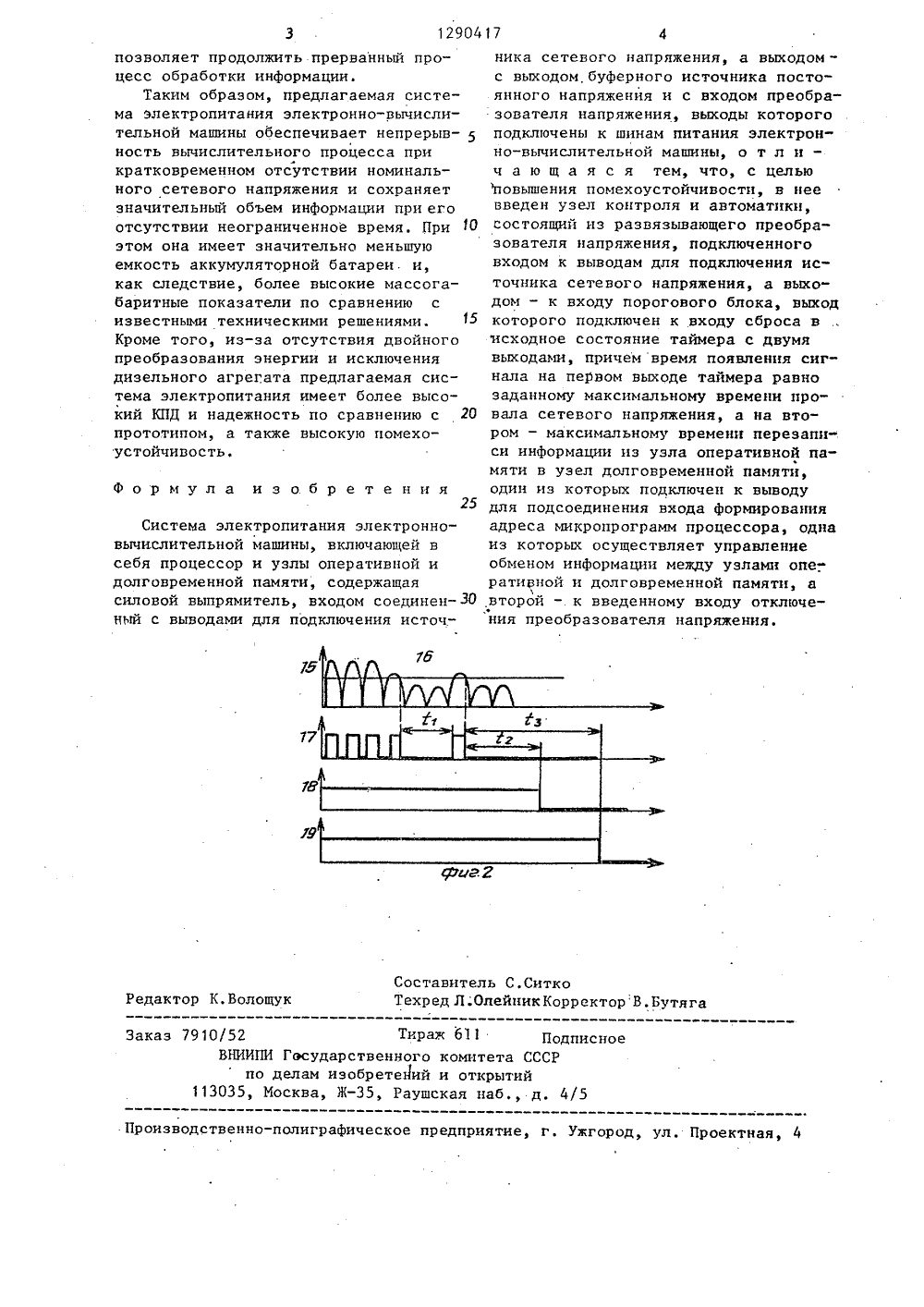

(19) (11) ОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(57) Изобретение относится к вторичным источникам электропитания. Цель - повьппение помехоустойчивости системы. Цель достигается за счет включения в схему таймера, фиксирующего сбой по 151) 4 С 11 С 11/00, Н 02 М 7/04, Н 02 Д 9/06 цепи питания. С таймера 11 формируется низкий логический уровень 18, поступающий в процессор 5, где происходитпереход на подпрограмму Прерывание по сбою питания", которая производит прерывание обработки информациии осуществляет перезапись информациина узлы 6 и 7. С таймера 11 на второмвыходе делителя частоты формируетсянизкий логический уровень 19, поступающий на вход отключения преобразо-.вателя 3 напряжения. ПреобРазователь3 отключается и потребление энергииот буферного источника 2 прекращается. 2 ил.12904Изобретение относится к электротехнике и может быть использовано для питания стабилизированными напряжениями электронно-вычислительных машин ЭВМ, имеющих энергонезависимые оперативные запоминающие устройства.Целью изобретения является повыше;ние помехоустойчивости системы.На фиг.1 представлена функциональная схема системы электропитания; га 10 фиг,2 - временные диаграммы.Система электропитания содержит силовой выпрямитель 1, буферный источник 2 постоянного напряжения, преобразователь 3 напряжения, выходы ко 15 торого подключены к шинам питания электронно-вычислительной машины (ЭВМ) 4, включающей в себя процессор 5, узел 6 оперативной памяти и узел . 7 долговременной памяти и узел 8 .контроля и автоматики, состоящий из развязывающего преобразователя 9, подключенного входом к выводам для подключения источника сетевого напряжения, а выходом - к входу порогового блока 10, выход которого подключенвходу сброса в исходное состояние таймера 11 с двумя выходами, один из которых подключен к выводу для подсоединения входа формирования адреса микропрограмм процессора, а второй - к входу отключения преобразователя 3. Таймер в одном из вариантов может быть выполнен на задающем генераторе 12, делителе частоты 13, выполненном на 35 логических элементах 14.Система электропитания работает следующим образом.Сетевое напряжение выпрямляется и сглаживается выпрямителем 1 и поступает в преобразователь 3 напряжения, который на повышенной частоте преобразует выпрямленное сетевое напряжение в необходимые напряжения для питания узлов ЭВМ 4 (процессор 5, узел 45 6 и т.д.) и узла 8 контроля и автоматики. Кроме того, напряжение с выпрямителя 1 прикладывается к буферному источнику 2 постоянного напряжения(например, аккумуляторной батарее).1Напряжение 15 с выхода развязывающего преобразователя (фиг.2), сравни-.ваясь с заданным опорным напряжением16 в пороговом блоке (например, вкомпараторе), формирует на его выходеимпульсы 17. Эти импульсы подаются навход управления таймера 11 (напрнмер,на входы сброса в ноль счетчиков де 17 2лителя частоты (фиг.1) . При наличии сетевого напряжения с допустимой амплитудой раз за полупериод сетевого напряжения происходит сброс счетчиков. Делитель частоты имеет два выхода, на которых формируются сигналы (низкий логический уровень) через =С игТ(Т -), где Т - период сетевогонапряжения) работы счетчиков делителячастоты,Таким образом, при наличии сетевого напряжения с допустимой амплитудойна первсм и втором выходе делителячастоты имеется логическая единицаСигналы на выходах делителя частотыне изменяются и при кратковременномпропадании либо уменьшением величинысетевого напряжения (фиг.2, ,сй ).При этом ЭВМ 4 находится в обычномрежиме, так как во время кратковременного сбоя электропитания.преобразователь, 3 напряжения получает энергию от буферного источника 2 постоянного напряжения.При длительном отсутствии сетевого.напряжения (11: ) из-эа конечной емкости буферного источника 2 постоянного напряжения необходимо защититьинформацию, находящуюся в быстродействующем, но энергозависимом узле 6оперативной памяти. С этой целью напервом выходе делителя частоты таймера 11 через время с=С формируетсянизкий логический уровень 18 (фиг.2),поступающий в процессор 5, где происходит переход на подпрограмму."Прерывание пс сбою питания", которая производит прерывание обработки информации и осуществляет перезапись информации на узлы 6 и 7.По ис.течении времени 1=1 (фиг.2)на втором выходе делителя частотытаймера 11 формируется низкий логический уровень 19 (Фиг.2), поступающий на вход отключения преобразователя 3 напряжения. При этом преобразователь 3 отключается и потреблениеэнергии от буферного источника 2 постоянного напряжения прекращается.В качестве преобразователя 3 напряжения может быть применен источникпитания с бестрансформаторным входом.При появлении сетевого напряжениявновь на любом этапе работы системыэлектропитания возможно автоматическое восстановление информации в процессоре 5 в прерванном месте, что12904 17 Составитель С.СиткоТехред Л.ОлейникКорректорВ.Бутяга Редактор К.Волощук Заказ 7910/52 Тираж 611 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 позволяет продолжить прерванный процесс обработки информации.Таким образом, предлагаемая система электропитания электронно-вычислительной машины обеспечивает непрерыв ность вычислительного процесса пригкратковременном отсутствии номинального сетевого напряжения и сохраняет значительный объем информации при его отсутствии неограниченное время. При 10 этом она имеет значительно меньшую емкость аккумуляторной батареи. и, как следствие, более высокие массогабаритные показатели по сравнению с известными техническими решениями. 15 Кроме того, из-за отсутствия двойного преобразования энергии и исключения дизельного агрегата предлагаемая система электропитания имеет более высокий КПД и надежность по сравнению с 20 прототипом, а также высокую помехоустойчивость. Формула изобретения25 Система электропитания электронновычислительной машины, включающей всебя процессор и узлы оперативной идолговременной памяти, содержащаясиловой выпрямитель, входом соединенный с выводами для подключения источ. -ника сетевого напряжения, а выходом "с выходом, буферного источника постоянного напряжения и с входом преобразователя напряжения, выходы которогоподключены к шинам питания электронно-вычислительной машины, о т л и -ч а ю щ а я с я тем, что, с цельюповышения помехоустойчивости, в неевведен узел контроля и автоматики,состоящий из развязывающего преобразователя напряжения, подключенноговходом к выводам для подключения источника сетевого напряжения, а выходом - к входу порогового блока, выходкоторого подключен к входу сброса висходное состояние таймера с двумявыходами, причем время появления сигнала на первом выходе таймера равнозаданному максимальному времени провала сетевого напряжения, а на втором - максимальному времени перезапи."си информации из узла оперативной памяти в узел долговременной памяти,один из которых подключен к выводудля подсоединения входа формированияадреса микропрограмм процессора, однаиз которых осуществляет управлениеобменом информации между узлами опе-.ратирной и долговременной памяти, авторой в .к введенному входу отключе,нния преобразователя напряжения.

СмотретьЗаявка

3665807, 05.08.1983

ПРЕДПРИЯТИЕ ПЯ А-3361

НЕСТЕРЕНКО ГЕНАДИЙ АНАТОЛЬЕВИЧ, РЕДЬКО ВИКТОР БОРИСОВИЧ, ПЕЛЬТЕК ИЛЬЯ ФЕДОРОВИЧ, ПОПОВ АЛЕКСАНДР АНАТОЛЬЕВИЧ

МПК / Метки

МПК: G11C 11/00, H02J 9/06, H02M 7/04

Метки: включающей, долговременной, оперативной, памяти, процессор, себя, узлы, электронно-вычислительной, электропитания

Опубликовано: 15.02.1987

Код ссылки

<a href="https://patents.su/3-1290417-sistema-ehlektropitaniya-ehlektronno-vychislitelnojj-mashiny-vklyuchayushhejj-v-sebya-processor-i-uzly-operativnojj-i-dolgovremennojj-pamyati.html" target="_blank" rel="follow" title="База патентов СССР">Система электропитания электронно-вычислительной машины, включающей в себя процессор и узлы оперативной и долговременной памяти</a>

Предыдущий патент: Кассета для двухслойных запоминающих матриц на биаксах

Следующий патент: Динамическое запоминающее устройство с автономным контролем

Случайный патент: Соединитель устройства для парентериального введения жидкости в организм биообъекта