Формирователь сигналов считывания

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

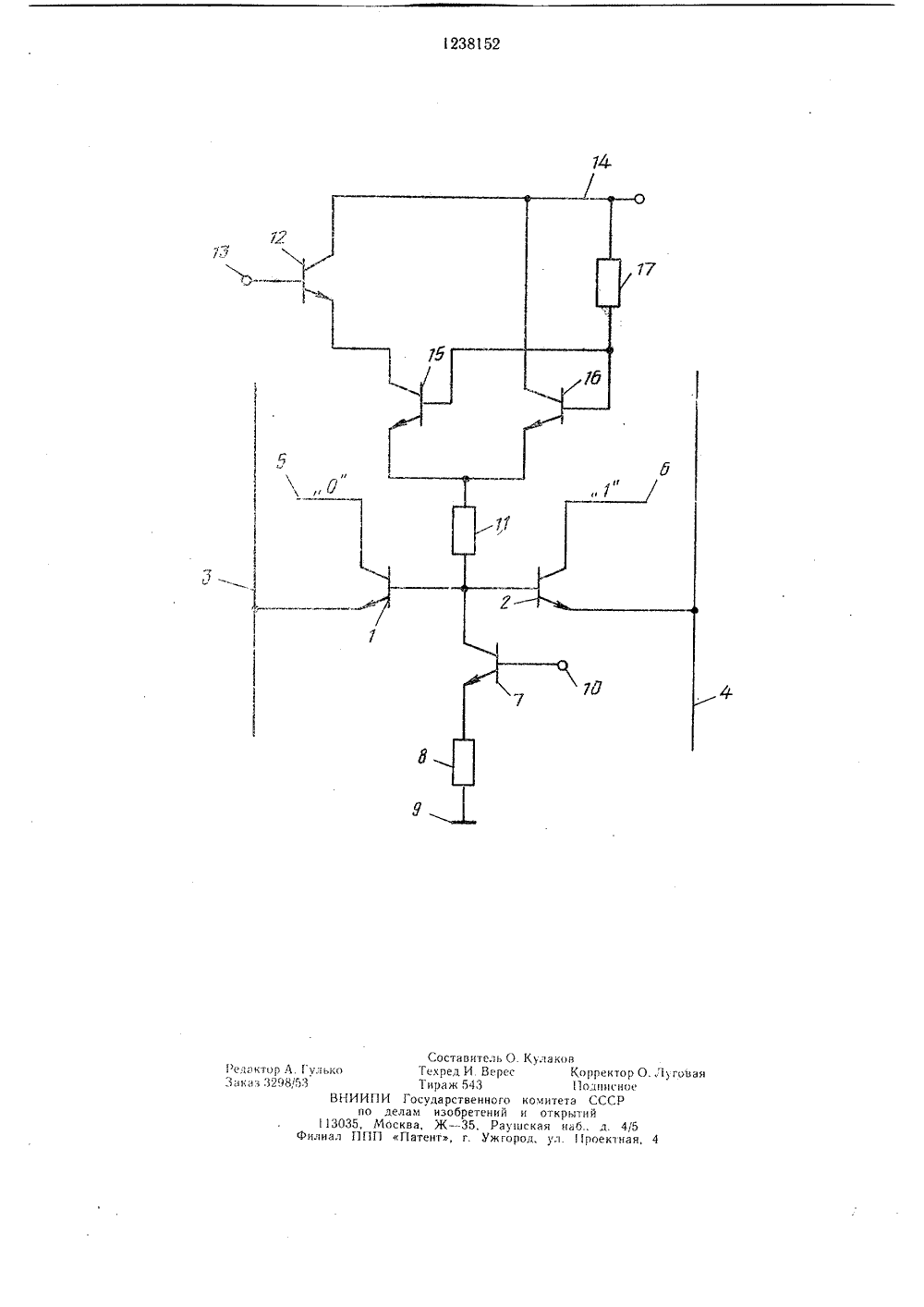

(57) Изобретение числительной тех относится к област ики и может быт ы- использовано при создании полупроводниковых интегральных схем памяти. Цель изобретения - упрощение формирователя сигналов считывания и снижение потребляемой им мощности при сохранении высокого быстродействия при считывании информации с запоминающих ячеек. Формирователь содержит ключевые транзисторы, резисторы, стабилизирующий транзистор, усилительные транзисторы, разрядные шины. Снижение потребляемой мощности осуществляется за счет оптимизации уровня считываемого сигнала.1 ил.5 10 1 20 25 30 35 40 45 50 55 Изобретение относится к вычислительной техникс и может быть использовано при создании попупроводниковых интегральных схем памяти.Цельк изобретения является упро 1 цение схемь и снижение потребляемой мощности при сохранении высокого быстродействия при счить 1 вании информации с запоминаюгцих ячЕЬк.На чертеже представлена принципиальная схема формирователя сигналов считывания.Формирователь содержит первый 1 и вто. рой 2 ключевые транзисторы, эмиттеры которых подключены к первой 3 и второй 4 разрядным шинам соответственно, а коллекторы является нулевым 5 и единичным 6 контрольными выходами формирователя, источник тока, состояц.ий из третьего кл)оченого ттднзистора 7 и первого резистора 8, г цц зынод которого подктцочен к общей ш гце 9, а нто 1 ии - к эмиттеру третьего ключевого транзистора 7, база которого является входом 1 О для подключения ис, о:1 ика опорного напряжения. Коллектор ц, дключец к перному выводу второго резистора 1, базы транзисторов 1 и 2 объецьецы и подкл 1 очецы к коллектору транзистора 7, базы стабилизирующего транзистод 12 является управляющим входом 13 формирователя, коллектор его подключен к шицс питания 14, а эмиттер соединен с коллектором первого усилительного транзистора .:-3 ми т.рь первого 15 и второго 6 усилительных транзисторов соединены и подключены к 1 лорому выводу резистора 11, коллгкто 1 второго усилительного транзистора 16 подключен к шине питания 14, резистор 17 подключен одцим выводом к шине ц гднця 14, а вторымк базам транзисторов 15 и 16.Формирователь работает следующим образом.При подаче на управляющий вход 13 напряжения шины питания 14 транзистор 15 находится нд границе насыщения и его больпсй базовый ток вызывает падение напряжения цд резисторе 7, равное ., =И, где И. цдцрчжецие коллектор - эмиттер насыщенного транзистора. Это происходит, так как контур база в эмитт транзистора 2, коллектор эмиттер транзистора 15 и контур база - эмиттер транзистора 16, резистор 7 включены параллельно, а падение цдцряжения ца переходах база в эмитт различных транзисторов в интегральной технологии выдерживается достаточно одинаковым.Таким образом, в точке соединения эмиттерон транзисторов5 и 6 сформирован потенциал, равный Е -- И - И., где Енапряжение шины питания 15; И, - напряжение на переходах база - -эмиттер транзисторов. Для обеспечения оптимального уровня Г - 1,75 И, на базах транзисторов 1 и 2 недостающее падение потенциала, равное 0,75 И-, формируется на резисторе 11 за счет протекания по нему гока источника тока ца транзисторе 7 и резисторе 8, получающем опорное напряжение с гходд 10,В результате один из транзисторов 1 или 2 открывается соответственно состоянию разядных шин 3 и 4, и, таким оордзом информация о состоянии разрядых шин 3 и 4 передается ца контрольные выходы 5 и 6.Снижение напряжения нд управляющем входе 13, моделируюнем сцижецис потенциала строки за счет уменьшения коэффициента усиления транзисторов н диапазоне рабочих температур, изменения разброса коэффициента усиления н техцологцлсском процессее и изменения тока, протекающего через стОку Я пиапдзоне рдбОчцх пемперату, передается за счет изменения базового тока транзистора 15 на резистор 7 и изменяет потенциал точки соединения змиттерон трдц зисторов 15 и 16.Уровень считьванин поникается ца такую же величину, что и управляющий вход 13 и остается оптимальным с токи зрения быстродеиствия при считывании.Формула изотретени Формирователь сигналов считывания, содержаций первый, второй, третий кночецьц транзисторы, стабил изцукнций транзистор, первый и второй резисторы, причем змит терц первого и второго кл:оченых т 1 днзисторов являются информдцнопцими входами формирователя, ныходамц которого являотея коллекторы первого и второго к ночевых транзисторов, один вывод цернгцо резцстора подключен к шицс нулевого потенциала, а другой вывод - к эмиттеру третьего ключевого транзистора, база которого подключена к шине опорного напряжения, а коллектор - к одному выводу второго резистора, коллектор стабилизируюцего транзистора соединен с шиной питания, а база является уцранляюгцим вхо. дом формирователя, агличаои 1 ийся тем, что, с целью упрощения формирователя и сцижения потребляемой им мощности, в него введены первый и второй усилительные транзисторы и третий резистор, один вывод которого подключен к цице питания, а другой -- к базам усилительных транзисторов, эмиттеры которых соединены с другим выводом второго резистора, коллектор вто. рого усилительного транзистора подключен и шине питания, коллектор первого уси. лительного транзистора соединен с эмиттером стабилизирующего транзистора, базы первого и второго ключевых транзисторов подключены к коллектору третьего ключевого транзистора.ь О. Кулакорес ставите. едИ В ж 543 рстаенн обретен- 35,гоЬа ого ко ий и Рдушс жгород едактор Л. 1 улькои к а з 320/8 53 ВНИИП по 113035,илиал ПП

СмотретьЗаявка

3779608, 14.08.1984

ОРГАНИЗАЦИЯ ПЯ А-3106

БОТВИНИК МИХАИЛ ОВСЕЕВИЧ, САХАРОВ МИХАИЛ ПАВЛОВИЧ, ПОПЕЛЬ АЛЕКСАНДР СЕМЕНОВИЧ

МПК / Метки

МПК: G11C 11/409, G11C 7/00

Метки: сигналов, считывания, формирователь

Опубликовано: 15.06.1986

Код ссылки

<a href="https://patents.su/3-1238152-formirovatel-signalov-schityvaniya.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь сигналов считывания</a>

Предыдущий патент: Устройство для регенерации информации

Следующий патент: Ферроакустическое запоминающее устройство

Случайный патент: Способ сейсмической разведки