Параллельно-последовательный аналого-цифровой преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1221751

Автор: Виксна

Текст

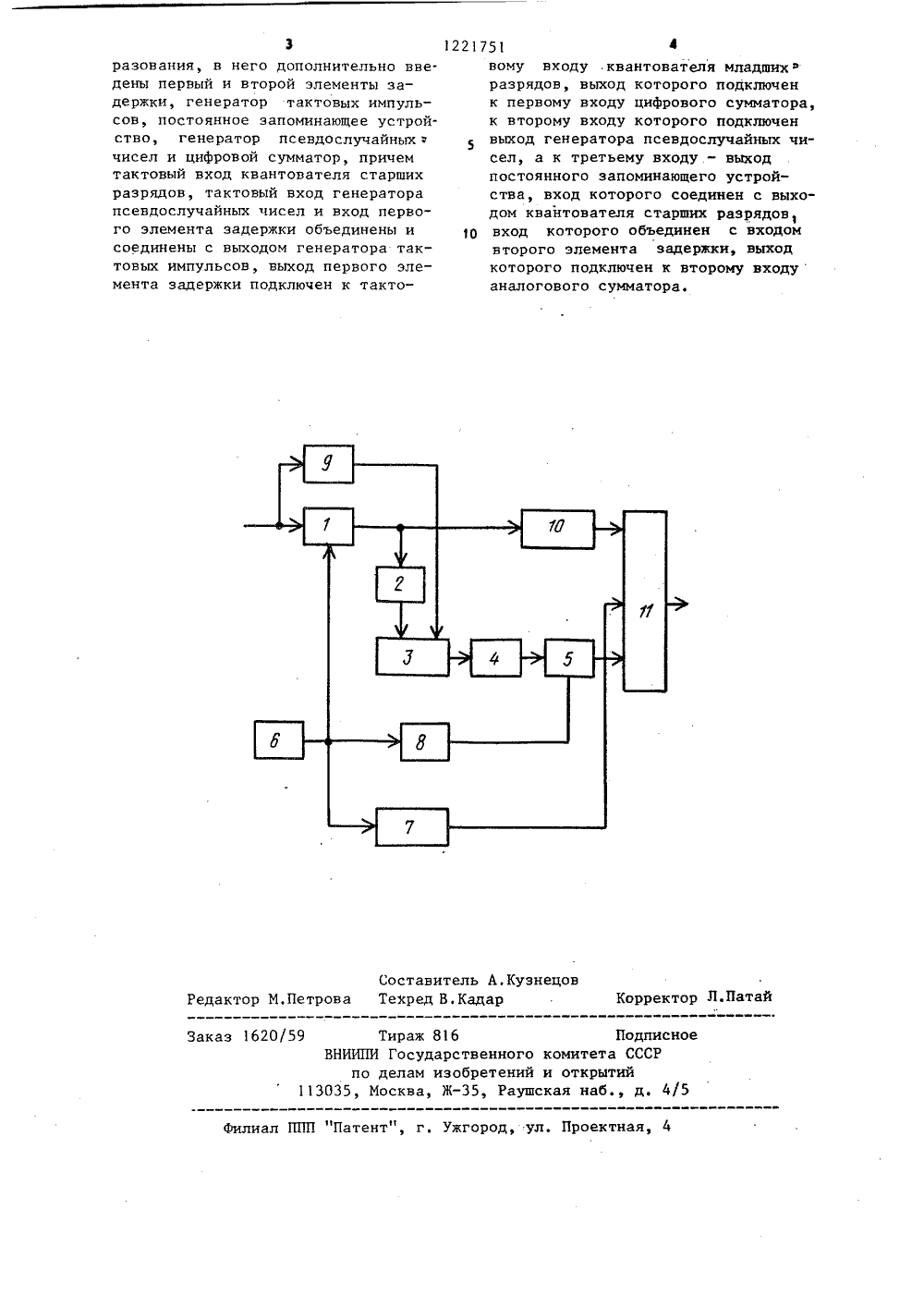

СООЭ СОВЕТСКИХСОЦИАЛ ИСТИЧЕСКРЕСПУБЛИК 1751 САНИЕ И Т СТВУ трукторскоестроения сИнститутаЛатССР тво СССР 75, 1978(54) ПАРАЛЛЕЛЬНО АНАЛОГО-ЦИФРОВОЙ (57) Изобретение пульсной технике устройствам парал ОСЛЕДОВАТЕЛЬНЫЙ РЕОБРАЗОВАТЕЛЬ тносится к имв частности к ельного аналог ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ АВТОРСКОМУ СВИДЕТ(71) Специальное консбюро научного прибороопытным производствоммеханики полимеров АН(56) Авторское свидетельУ 769731, кл. Н 03 К 13/Патент ФРГ У 2756675,кл. Н 03 К 13/09, 1981,дискретного преобразования, в которых множество опорных значений,различных по величине, одновременно сравнивается с аналоговыми значениями преобразуемого сигнала.Изобретение позволяет повысить точность преобразования параллельнопоследовательного аналого-цифровогопреобразователя, содержащего квантователь 1 старших разрядов, блок 2цифроаналогового преобразования,аналоговый сумматор 3, .усилитель 4,квантователь 5 младших разрядов, эасчет введения в устройство первого8 и второго 9 элементов задержки,генератора 6 тактовых импульсов, по.стоянного запоминающего, устройства10, генератора 7 псевдослучайных .чисел и цифрового сумматора 11 1 ил.45 50 55 1 122Изобретение относится к импульсной технике, в частности к устройствам параллельного аналого-дискретного преобразования,. в которых множество опорных значений, различныхпо величине, одновременно сравниваются с аналоговыми значениями преобразуемого сигнала, и может бытьиспользовано в скоростных системахобработки информации.Цель изобретения - повьппение точности преобразования.На чертеже представлена структурная схема параллельно-последовательного аналого-цифрового преобразователя.1Преобразователь содержит квантователь 1 старших разрядов, блок 2цифроаналогового цреобразования;аналоговый сумматор 3, усилитель 4,квантователь 5 младших разрядов, генератор б тактовых импульсов, генератор 7 псевдослучайных чисел, первый8 и второй 9 элементы .задержки, постоянное запоминающее устройство 10,цифровой сумматор 1.Выход цифрового сумматора 11 является выходом устройства.Устройство работает следующим образом.Тактовые импульсы от генератораб тактовых импульсов поступают наквантователь 1 старших разрядов игенератор 7 псевдослучайных чисел.Первый элемент 8 задержки задерживает последовательность тактовых импульсов на времянеобходимое длякомпенсации времени формирования кода квантователя 1 старших разрядов,времени срабатывания блока 2 цифроаналогового преобразования, аналогового сумматора 3 и усилителя 4.Второй элемент 9 задержки задерживает преобразуемый сигнал Х на время Й, необходимое для компенсациивремени формирования .кода квантователя 1 старших разрядов и временисрабатывания блока 2 цифроаналогового преобразования, Код с квантователя 1 старших разрядов Х блоком2 цифроаналогового преобразованияпреобразуется в аналоговый сигналХ и поступает на вход аналоговогоЯАсумматора 3, куда также поступаетчерез элемент 9 задержки преобразуемый сигнал Х,На выходе аналогового сумматора3 формируется разность сигналов(Х-Х ), которая усилителем 4 уси 1751 а ливается до требуемой величины, задаваемой квантователем 5 младших разрядов.Усиленный сигнал разности (Х-Х)5в квантователе 5 младших разрядовквантуется, в результате чего навыходе квантователя 5 формируетсякод (Х-Х)9.Так как величина погрешности преобразования стабильна во времени,то в предлагаемом устройстве имеетсяпостоянное запоминающее устройство10, в котором записаны предварительно замеренные, с погрешностью не более половины значения младшего кванта, значения Хц, т.е, фактические дискретные значения аналоговыхвеличин Х , подаваемых на вход аналогового сумматора 3,В цифровом сумматоре 11 суммируются фактические значения Х 1, хранящиеся в постоянном запоминающемустройстве 10 с кодами квантователя 5 младших разрядов.(Х-ХА )9, врезультате чего формируется конечный многоразрядный код оценки мгновенного значения входного сигнала.Так как разрядность суммы кодовХ=1 Х А+(Х-Х 1)9 больше разряднос 30ти всего аналого-цифрового преобразователя,то посредствомдобавленияк кодукХ в цифровом сумматоре 11равномерно распределенного псевдослучайного числаи округления младшихразрядов суммы ( Х+, получается навыходе цифрового сумматора 11 округленное значение оценки Х без систематической ошибки.Источником псевдослучайных чиселявляется генератор 7,40 Введенную избыточность уровней квантования для квантователя 5 младших разрядов учитывают при расчетевеличин кодов Х .( Формула изобретения Параллельно-последовательный аналого-цифровой преобразователь, содержащий последовательно подключенные квантователь старших разрядов, блок цифроаналогового преобразования, аналоговый сумматор, усилитель и квантователь младших разрядов, вход квантователя старших разрядов является входной шиной, о т л и ч а ю щ и й с я тем,. что, с целью повышения точности преоб1221751 Составитель А.КузнецовРедактор М.Петрова Техред В.КадарКорректор Л.Патай Заказ 1620/59 Тираж 816 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 разования, в него дополнительно введены первый и второй элементы задержки, генератор тактовых импульсов, постоянное запоминающее устройство, генератор псевдослучайныхчисел и цифровой сумматор, причемтактовый вход квантователя старшихразрядов, тактовый вход генераторапсевдослучайных чисел и вход первого элемента задержки объединены исоединены с выходом генератора тактовых импульсов, выход первого элемента задержки подключен к тактовому входу квантователя младшихфразрядов, выход которого подключенк первому входу цифрового сумматора,к второму входу которого подключенвыход генератора псевдослучайных чисел, а к третьему входу. - выходпостоянного запоминающего устройства, вход которого соединен с выходом квантователя старших разрядов 1 О вход которого объединен с входомвторого элемента задержки, выходкоторого подключен к второму входуаналогового сумматора.

СмотретьЗаявка

3676070, 12.12.1983

СПЕЦИАЛЬНОЕ КОНСТРУКТОРСКОЕ БЮРО НАУЧНОГО ПРИБОРОСТРОЕНИЯ С ОПЫТНЫМ ПРОИЗВОДСТВОМ ИНСТИТУТА МЕХАНИКИ ПОЛИМЕРОВ АН ЛАТВССР

ВИКСНА АНДРИС ЖАНОВИЧ

МПК / Метки

МПК: H03M 1/36

Метки: аналого-цифровой, параллельно-последовательный

Опубликовано: 30.03.1986

Код ссылки

<a href="https://patents.su/3-1221751-parallelno-posledovatelnyjj-analogo-cifrovojj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Параллельно-последовательный аналого-цифровой преобразователь</a>

Предыдущий патент: Аналого-цифровой преобразователь

Следующий патент: Преобразователь угол-код

Случайный патент: Универсальный частотный пьезодатчик механических величин