Устройство для вычисления функции ( )

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1076912

Автор: Анишин

Текст

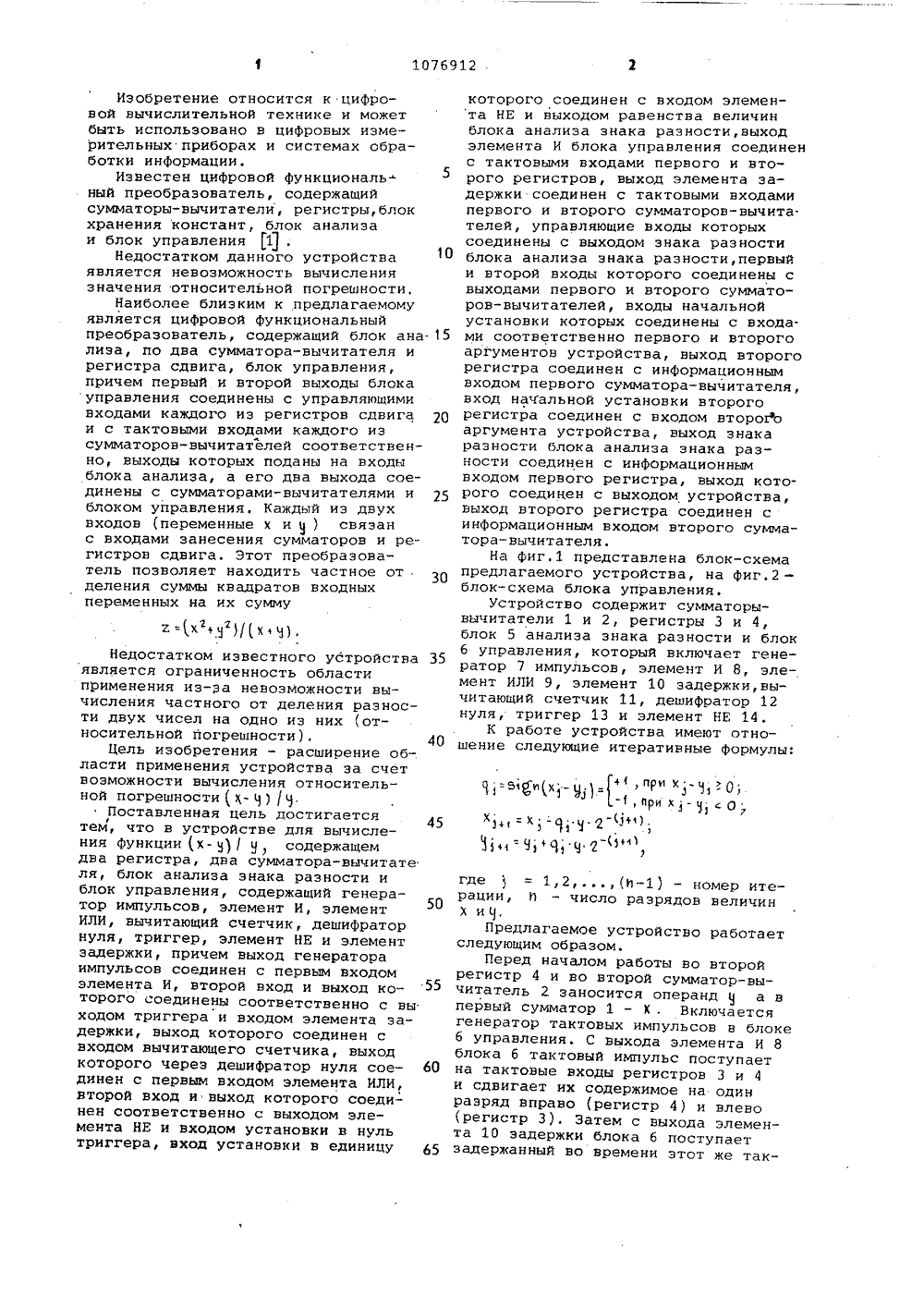

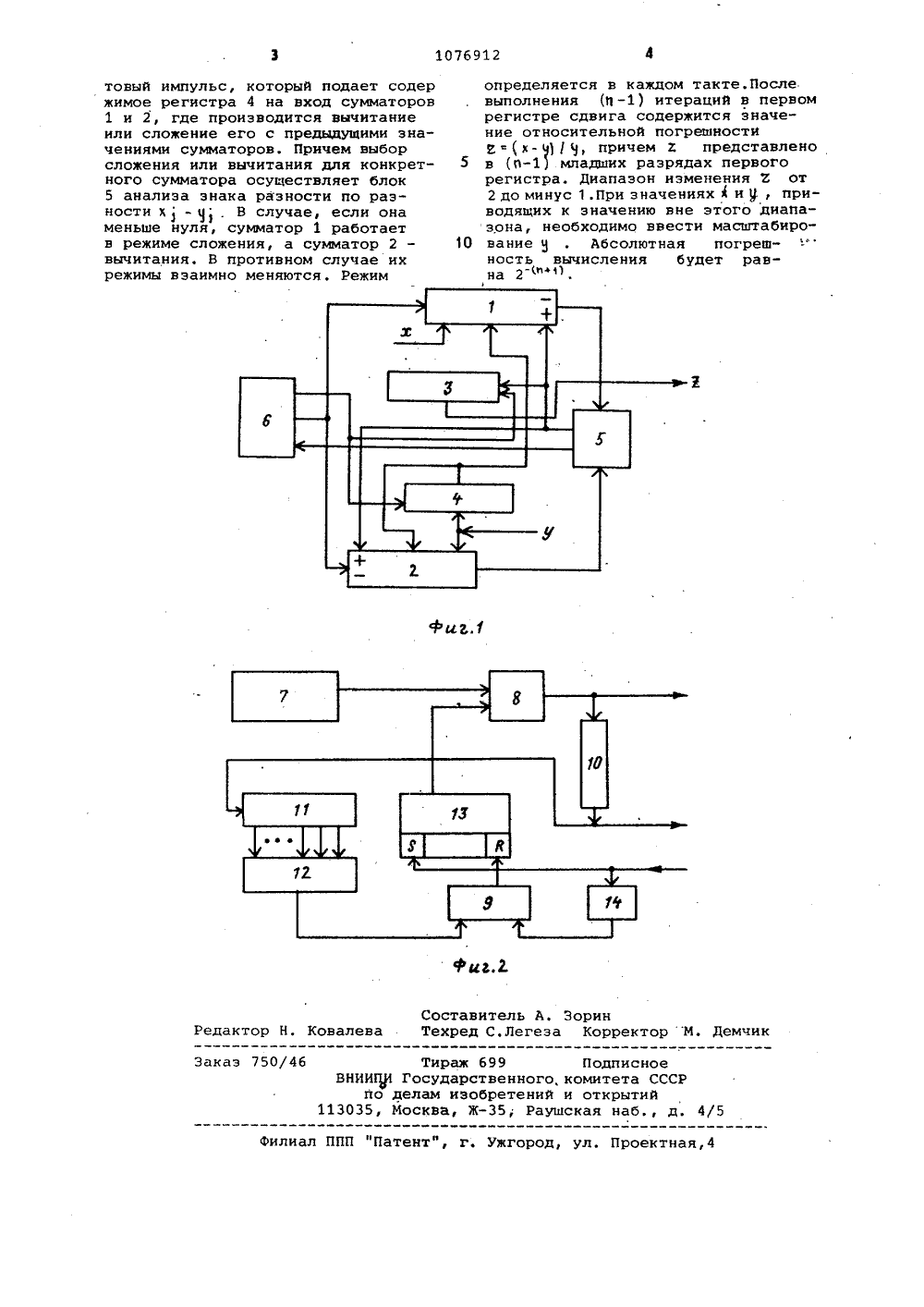

(19) (11) 3151) 0 06 Г 15/31 ОПИСАНИЕ ИЗОБРЕТЕНИЯН АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(72) Н.С. Анишин и А.С, Анишин (71) Кубанский государственный университет(56) 1. Авторское свидетельство СССР Р 922760, кл. 0 06 Р 15/31, 1980.2. Авторское свидетельство СССР744595, кл. 0 06 Р 15/31, 1976 (прототип).(54) (57) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИя фУКЦИИ (х-у)/у, содержащеедва регистра, два сумматора-вычитателя, блок анализа знака разностии блок управления, содержащий генератор импульсов, элемент И, элемент ИЛИ, вычитающий счетчик, дешифратор нуля, триггер, элемент НЕи элемент задержки, причем выходгенератора импульсов соединен спервым входом элемента И, второйвход и выход которого соединенысоответственно с выходом триггераи входом элемента задержки, выходкоторого соединен с входом вычитающего счетчика, выход которого черездешифратор нуля соединен с первымвходом элемента ИЛИ, второй вход ивыход которого соединены соответственно с выходом элемента НЕ ивходом установки в нуль триггера,вход установки в единицу которого соединен с входом элемента НЕ и выхо дом равенства величин блока анализа знака разности, выход элемента И блока управления соединен с тактовыми входами первого и второго регистров, выход элемента задержки соединен с тактовыми входами первого и второго сумматоров-вычитателей, управляющие входы которых соединены с выходом знака разности блока анализа знака разности, первый и второй входы которого соединены соответственно с выходами первого и второго сумматоров-вычитателей, входы начальной установки которых соединены соответственно с входами первого и второго аргументов устройства, выход второго регистра соединен с входом первого сумматоравычитателя, вход начальной установки второго регистра соединен с входом второго аргумента устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения за счет возможности вычисления относительной погрешности(-9)( Ц, выход знака разности блока анализа знака разности соединенс информационным входом первого регистра,выход которого соединен с выходом устройства, выход второго регистра соединен с информационным входом второго сумматора-вычитателя.Изобретение относится к цифровой вычислительной технике и может быть использовано в цифровых измерительных приборах и системах обработки информации.Известен цифровой функциональ ный преобразователь, содержащий сумматоры-вычитатели, регистры, блок хранения констант, блок анализа и блок управления (1 .Недостатком данного устройства является невозможность вычисления значения относительной погрешности,Наиболее близким к предлагаемому является цифровой функциональный преобразователь, содержащий блок ана лиза, по два сумматора-вычитателя и регистра сдвига, блок управления, причем первый и второй выходы блока управления соединены с управляющими входами каждого из регистров сдвига 7 О и с тактовыми входами каждого из сумматоров-вычитателей соответственно, выходы которых поданы на входы блока анализа, а его два выхода соединены с сумматорами-вычитателями и 25 блоком управления. Каждый из двух входов (переменные х и) связан с входами занесения сумматоров и регистров сдвига. Этот преобразователь позволяет находить частное от деления суммы квадратов входных переменных на их суммук =хг+ г)/ х+ Ч)Недостатком известного устройства 35 является ограниченность области применения из-за невозможности вычисления частного от деления разности двух чисел на одно из них (относительной погрешности). 40Цель изобретения - расширение области применения устройства за счет воэможности вычисления относительной погрешности ( Х- Ч ) / 3Поставленная цель достигается тем, что в устройстве для вычисления функции х- ) / у, содержащем два регистра, два сумматора-вычитате ля, блок анализа знака разности и блок управления, содержащий генератор импульсов, элемент И, элемент ИЛИ, вычитающий счетчик, дешифратор нуля, триггер, элемент НЕ и элемент задержки, причем выход генератора импульсов соединен с первым входом элемента И, второй вход и выход которого соединены соответственно с вы. ходом триггера и входом элемента задержки, выход которого соединен с входом вычитающего счетчика, выход которого через дешифратор нуля сое динен с первым входом элемента ИЛИ, второй вход и выход которого соединен соответственно с выходом элемента НЕ и входом установки в нуль триггера, вход установки в единицу 65 которого соединен с входом элемента НЕ и выходом равенства величин блока анализа знака разности, выход элемента И блока управления соединен с тактовыми входами первого и второго регистров, выход элемента задержки соединен с тактовыми входами первого и второго сумматоров-вычита. телей, управляющие входы которых соединены с выходом знака разности блока анализа знака разности, первый и второй входы которого соединены с выходами первого и второго сумматоров-вычитателей, входы начальной установки которых соединены с входами соответственно первого и второго аргументов устройства, выход второго регистра соединен с информационным входом первого сумматора-вычитателя, вход начальной установки второго регистра соединен с входом второго аргумента устройства, выход знака разности блока анализа знака разности соединен с информационным входом первого регистра, выход которого соединен с выходом устройства, выход второго регистра соединен с информационным входом второго сумматора-вычитателя.На Фиг.1 представлена блок-схема предлагаемого устройства, на фиг.2 - блок-схема блока управления.Устройство содержит сумматорывычитатели 1 и 2, регистры 3 и 4, блок 5 анализа знака разности и блок 6 управления, который включает генератор 7 импульсов, элемент И 8, элемент ИЛИ 9, элемент 10 задержки,вычитающий счетчик 11, дешифратор 12 нуля, триггер 13 и элемент НЕ 14.К работе устройства имеют отношение следующие итеративные формулы:где= 1,2 (И) - номер итерации, й - число разрядов величин Х иЦ.Предлагаемое устройство работает следующим образом.Перед началом работы во второй регистр 4 и во второй сумматор-вычитатель 2 заносится операнда в первый сумматор 1 - М . Включается генератор тактовых импульсов в блоке б управления. С выхода элемента И 8 блока б тактовый импульс поступает на тактовые входы регистров 3 и 4 и сдвигает их содержимое на один разряд вправо (регистр 4) и влево (регистр 3). Затем с выхода элемента 10 задержки блока б поступает задержанный во времени этот же так, комитета СССР и открытий ушская наб д. 4каэ 750 699рственнозобретенЖ, Р Тираж ВНИИПИ ГосУда по делам и 3035, Москва, Ужгоро роектная,4 товый импульс, который подает содержимое регистра 4 на вход сумматоров1 и 2, где производится вычитаниеили сложение его с предыдущими значениями сумматоров. Причем выборсложения или вычитания для конкретного сумматора осуществляет блок5 анализа знака разности по разности х-. В случае, если онаменьше нуля, сумматор 1 работаетв режиме сложения, а сумматор 2вычитания. В противном случае ихрежимы взаимно меняются. Режим Филиал ППП "Патент" определяется в каждом такте. Послевыполнения (И -1) итераций в первомрегистре сдвига содержится значение относительной погрешности( ю - ч) (причем е представленов (о) младших разрядах первогорегистра. Диапазон изменения Е от2 до минус 1.При значениях ( и фприводящих к значению вне этого диапаэона, необходимо ввести масштабирование ц . Абсолютная погрешность вычисления будет равна 2-Ф 11

СмотретьЗаявка

3404884, 11.03.1982

КУБАНСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ

АНИШИН НИКОЛАЙ СЕРГЕЕВИЧ, АНИШИН АНАТОЛИЙ СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 17/10

Метки: вычисления, функции

Опубликовано: 28.02.1984

Код ссылки

<a href="https://patents.su/3-1076912-ustrojjstvo-dlya-vychisleniya-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функции ( )</a>

Предыдущий патент: Устройство для вычисления функции ( )( + )

Следующий патент: Параллельный статистический анализатор отклонений и колебаний напряжения

Случайный патент: Узловое соединение стержней пространственного покрытия