Буферное запоминающее устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1034069

Автор: Лупиков

Текст

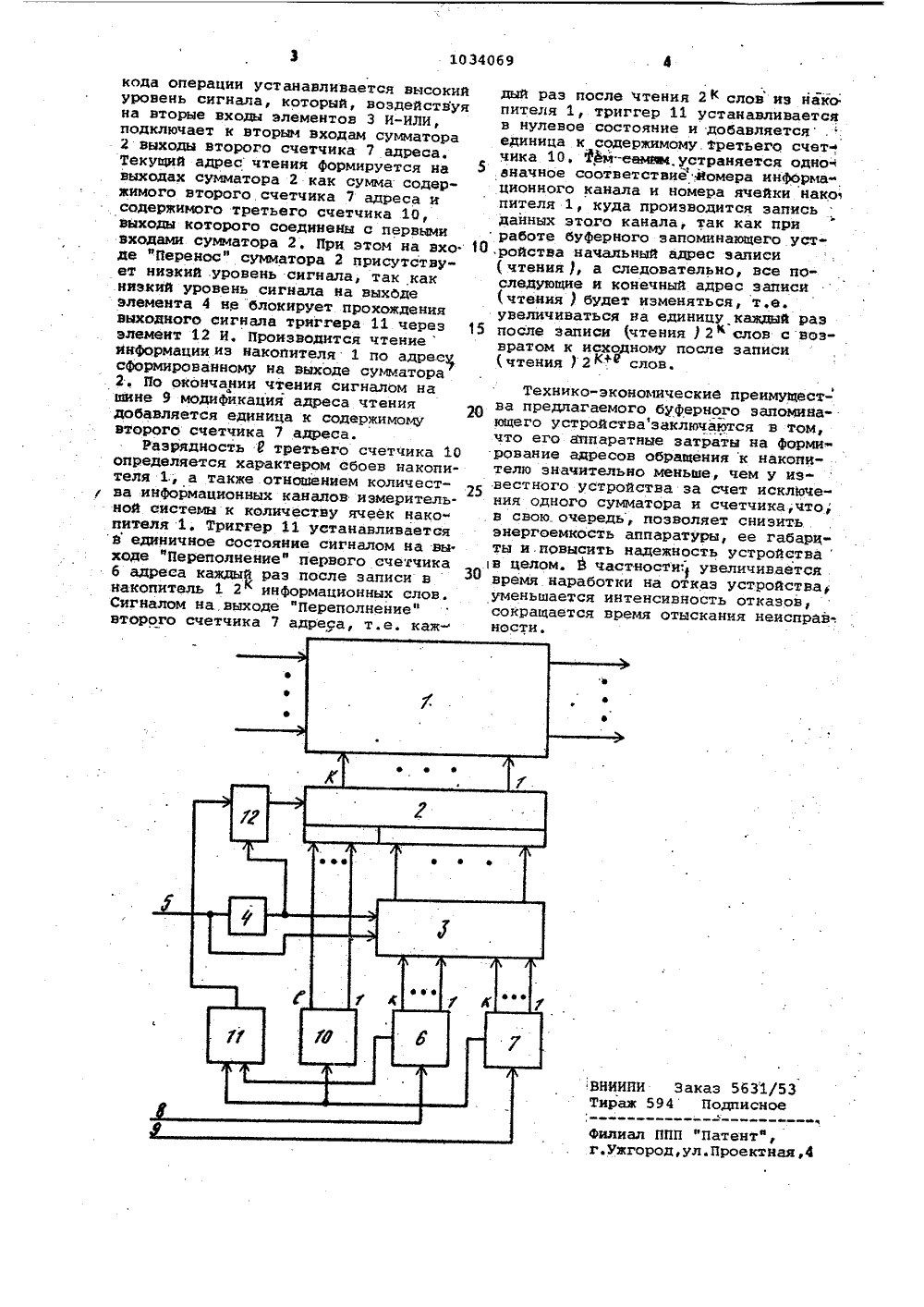

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 3 а)С 11 С 90 ОМИТЕТ СССРРЕТЕНИЙ И ОТКРЫТИЙ Оп НАВ АКИЕ ИЗ ОЬВУ СВИДЕТ БР Н СТВ(56) 1. Авторское свидетельство СССР.Р 822287 кл. 6 11 С 9/00 1979.2, Авторское свидетельство СССРпо заявке Р 3289715/18-24,кл. 6 11 С 9/00, 1981 (прототип).(54)(57) БУФЕРНОЕ ЗАПОМИНИОЩЕЕУСТРОЙСТВО, содержащее накопитель,информационные входы и выходы которо ,го являются соответственно информационными входами и выходами устройства, сумматор, элементы И-ИЛИпервыевходы которых соединены с выходомэлемента НЕ, вход элемента НЕ соеди- .нен с вторыми входами элементов И-ИЛИи является первым управляющим входомустройства, первый и второй счетчикиадреса, входы которого являются соот,ветственно вторым и третьим управля,.ЯО 1034069 ющими входами устройства, б т л ич а ю щ е е с я тем, что, с цельюповышения надежности устройства, внего введены триггер, элемент И, третий счетчик адреса, вход которогосоединен с первым входом триггера ивыходом фПереполнение" второго счетчика адреса, выходы третьего счетчика адреса соединены с одними вхо-дами сумматора, другие входы которогосоединены с входами элементов И-ИЛИ,третьи и четвертые входы которых со,ответственно соединены с выходамипервого и второго счетчиков адреса,выход "ПерепоЛнение" первого счетчика адреса соединен с вторым входомтриггера, выход которого соединен спервым входом элемента И, второйвход которого соединен с выходомэлемента НЕ, а выход элемента И соединен с входом "Перенос" сумматора,выходы которого соединены с адресными входами накопителя.35 40 45 50 55 Изобретение относится к вычислительной технике и может быть исполь" зовано в буферных запоминающих устройствах систем ввода информации многоканальных измерительных комплексов.Известно буферное запоминающееустройство, в котором используется метод перекрестно-последовательного об ращения, позволяющий осуществлять двусторонний обмен информацией и сов мещать процессы ввода в буферное за" поминающее устройство и вывода инфор мации из него 11.Однако использование известного устройства в системах ввода информа ции многоканальных измерительных комплексов, когда последовательность опроса каналов неизменна, а их количество Равно или кратно и превышает количество ячеек буферного запоминаю щего устройства, отказ одной или нескольких ячеек накопителя приводит к потерям информации от одного или нескольких каналов,Наиболее близким к предлагаемому является буферное запоминающее устройство, содержащее накопитель,информационные входы и выходы которого соответственно являются информационными входами и выходами устройства, сумматор, элементы И-ИЛИ,первые входы которых подключены к выходу элемента НЕ, вход элемента НЕ соединен с вторыми входами элементов И-ИЛИ и является первым управляю щим входом устройства, первый и второй счетчики адреса, входы которых являются соответственно вторым и тре тьим управляющими входами устройства 12 1.Недостатком такого устройства является низкая надежность, обусловлен. ная большим количеством оборудования схем формирования адресов обращения к накопителю,Цель изобретения - повышение надежности устройства за счет его упрощения.Поставленная цель достигается тем, что в буферное запоминающее уст ройство, содержащее накопитель, информационные входы и выходы которого являются соответственно информационными входами и выходами устройства, сумматор, элементы И-ИЛИ, первые входы которых соединены с выходом элемента НЕ, вход элемента НЕ соединен с вторыми входами элементов И-ИЛИ и является первым управляющим входом устройства, первый и второй счетчики адреса, входи которых являются соответственно вторым и третьим управляю 60 щими входами устройства, введенытриггер, элемент И, третий счетчикадреса, вход которого соединен с первым входом триггера и выходом "Переполнение" второго счетчика адреса,выходы третьего счетчика адреса соединены с одними входами сумматора, другие входы которого соединены с входами элементов И-ИЛИ, третьи и четвертые входы которых соответствен но соединены с .выходами первого и второго счетчиков адреса, выход "Переполнение" первого счетчика адреса соединен с вторым входом триггера, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом элемента НЕ, а выход элемента И соединен с входом "Перенос" сумматора, выходы которого соединены с адресными входами накопителя.На чертеже представлена структурная схема буферного запоминающего устройстваУстройство содержит накопитель 1, сумматор 2, элементы 3 И-ИЛИ, элемент 4 НЕ, шину 5 кода операции, первый счетчик б адреса, второй счетчик 7 адреса, шину 8 модификации адреса записи, шину 9 модификации адреса чтения, третий счетчик 10 адреса, триггер 11, элемент 12 И.Устройство работает следующим образом.Перед началом работы счетчики б, 7 и 10 адреса устанавливаются, как и триггер 11, в нулевое состояние цепь начальной установки на чертеже не.показана ), Емкость буферного запоминающего устройства определяет- ся разрядностью первого счетчика б адреса второго счетчика 7 адреса) и составляет Ч =2 слов, где К - количество разрядов первого счетчика 6 второго счетчика 7 адреса.При выполнении операции записи информации в накопитель 1 на шине 5 кода операции устанавливается низкий уровень сигнала, который, воздействуя через элемент 4 НЕ на первые входы элементов 3 И-ИЛИ, подключает к вторым входам сумматора 2 выходы первого счетчика б адреса. Текущий адрес записи Формируется на выходах сумматора 2 как суыка содержимого первого счетчика б адреса и содержимого третьего счетчика 10, выходы которого соединейк с первыми .входами сумматора 2, с учетом сигнала на входе "Перенос" сумматора 2. Высокий уровень сигнала на выходе элемента 4 НЕ, воздействуя на элемент 12 Иподключает ко входу переноса сумматора 2 выходной сигнал триггера 11, В накопитель 1 по адресу, сформированному на выходах сумматора 2, осуществляется запись информации с входных шин числа. По окончании записи сигналом на шине 8 модификация адреса записи добавляется единица к содержимому первого счетчика б адреса записи.При выполнении операции чтения информации из накопителя 1 на шине 51034069 И Заказ 5631/5 594 Подписное кода операции устанавливается высокийуровень сигнала, который, воздействуяна вторые входы элементов 3 И-ИЛИ,подключает к вторым входам сумматора2 выходы второго счетчика 7 адреса,Текущий адрес чтения формируется навыходах сумматора 2 как сумма содержимого второго. счетчика 7 адреса исодержимого третьего счетчика 10,выходы которого соединены с первымивходами сумматора 2. При. этом на входе фйереносф сумматора 2 присутствует низкий уровень сигнала, так какнизкий уровень сигнала на выходеэлемента 4 не блокирует прохождениявыходного сигнала триггера 11 черезэлемент 12 И. Производится чтениеинформации из накопителя 1 по адрессформированному на выходе сумматора2. По окончании чтения сигналом нашине 9 модификация адреса чтениядобавляется единица к содержимомувторого счетчика 7 адреса.Разрядность Ю третьего счетчика 10определяется характером сбоев накопителя 1, а также отношением количеств ва информационных каналов измерительной.системы к количеству ячеек вако"пителя 1. Триггер 11 устанавливается в единичное состояние сигналом на вы.ходе фйереполнениеф первого счетчикаб адреса каждый раз после записи внакопитель 1 2 информационных слов.Сигналом на.выходе "Переполнение"второго счетчика 7 адреса, т.е. каждый раз после чтения 2 " слов из нако пителя 1, триггер 11 устанавливается в нулевое состояние и добавляется ." единица к содержимому. третьего счетчика 10. Тем-еемща,устраняется одно вначное соответствие 4 омера информа ционного канала и номера ячейки нако пителя 1, куда производится запись данных зтога канала, так как приработе буферного запоминающего усто ройства начальный адрес записи(чтения , а следовательно, все последующие и конечный адрес записи (чтения ) будет изменяться, т.е, увеличиваться на единицу каждый раз 15 после записи (чтения 1 2 К слов с возвратом к исходному после записи (чтения ) 2+ слов. Технико-зкономические преимущества предлагаемого буферного запоминающего устройствазаключаются в том, что его аппаратные затраты на форин рование адресов обращения к накопителю значительно меньше, чем у известного устройства за счет исключения одного сумматора и счетчика,что; . в свою. очередь, позволяет снизить энергоемкость аппаратуры, ее габарИ- ты и повысить надежность устройства в целом. Й частности. увеличивается время наработки на отказ устройства уменьшается интенсивность отказов, сокращается время отыскания неисправ; ности. иал ППП фПатентф, г.Ужгород,ул.Проектная,4

СмотретьЗаявка

3411800, 26.03.1982

ПРЕДПРИЯТИЕ ПЯ А-3756

ЛУПИКОВ ВИКТОР СЕМЕНОВИЧ

МПК / Метки

МПК: G11C 19/00

Метки: буферное, запоминающее

Опубликовано: 07.08.1983

Код ссылки

<a href="https://patents.su/3-1034069-bufernoe-zapominayushhee-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Буферное запоминающее устройство</a>

Предыдущий патент: Устройство для прошивки запоминающих матриц на ферритовых сердечниках

Следующий патент: Запоминающее устройство с обнаружением ошибок

Случайный патент: 188292