Микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

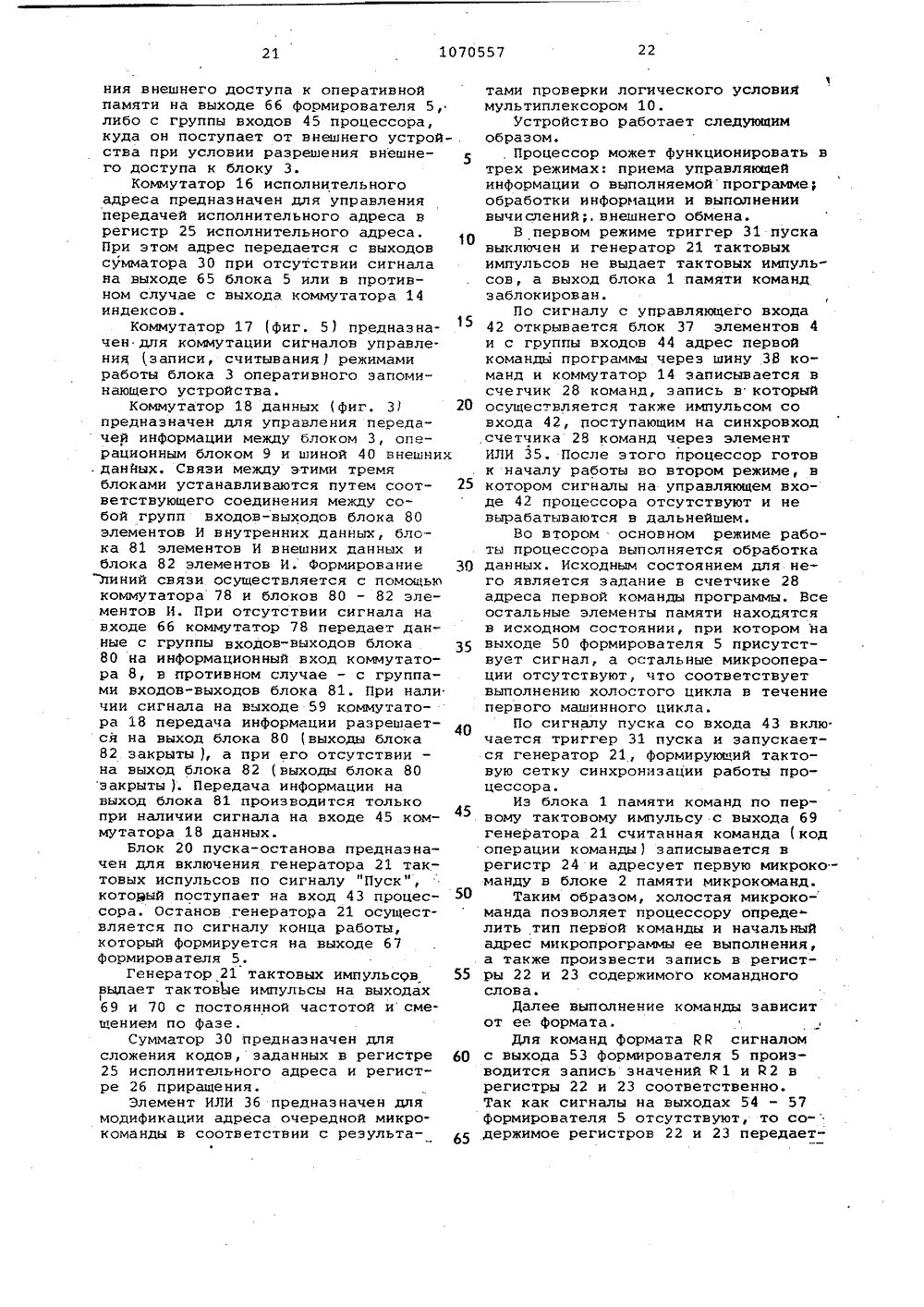

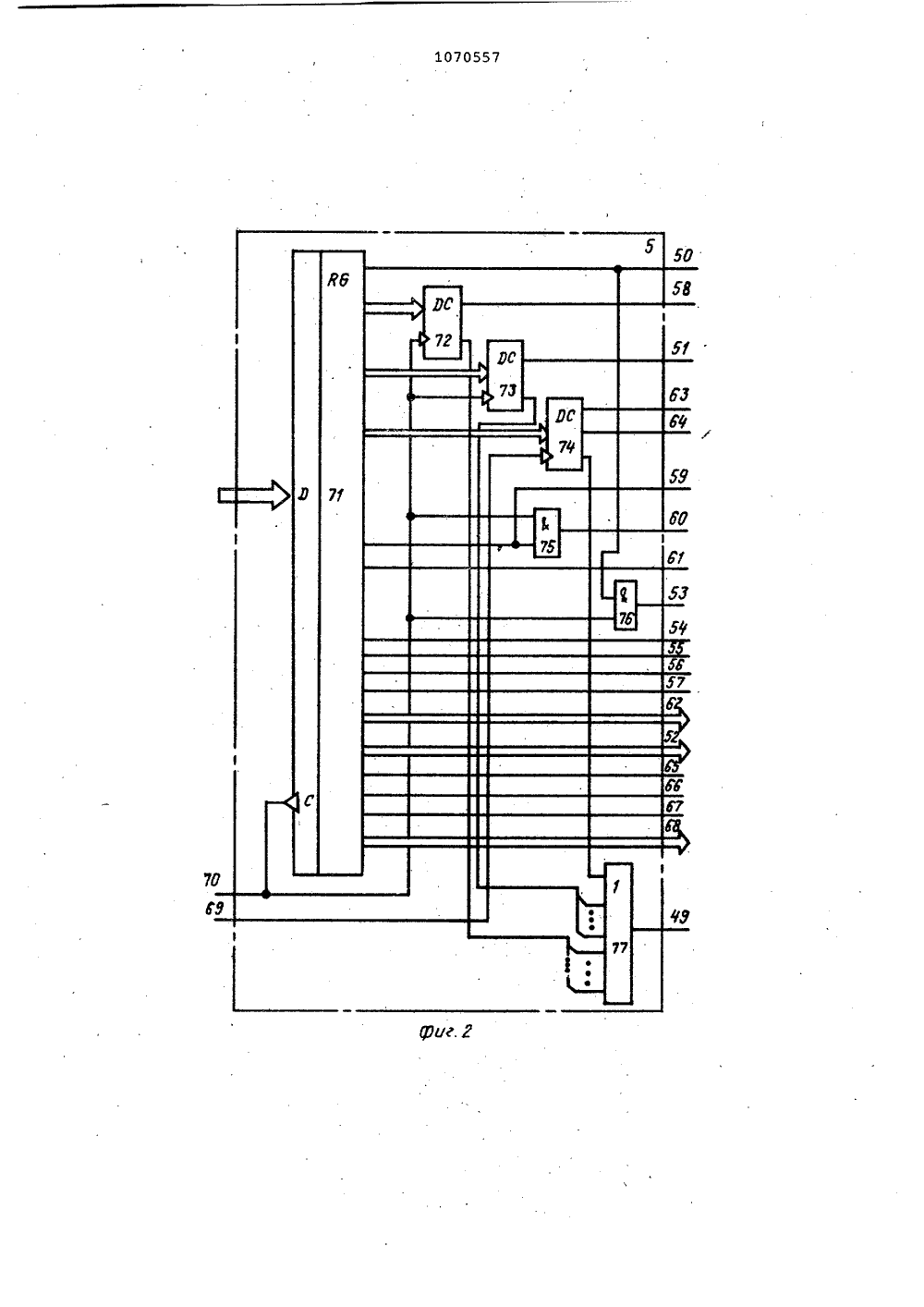

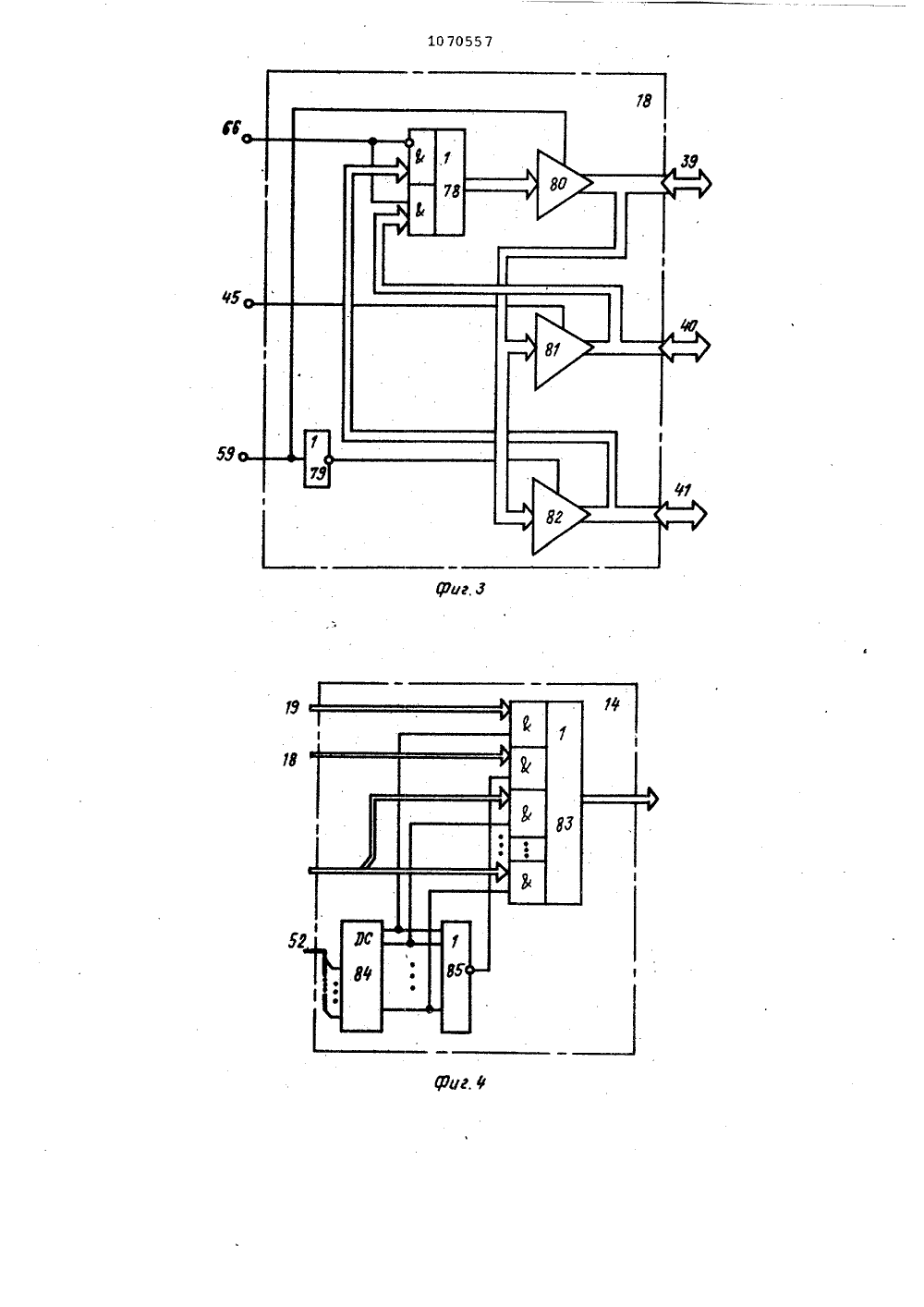

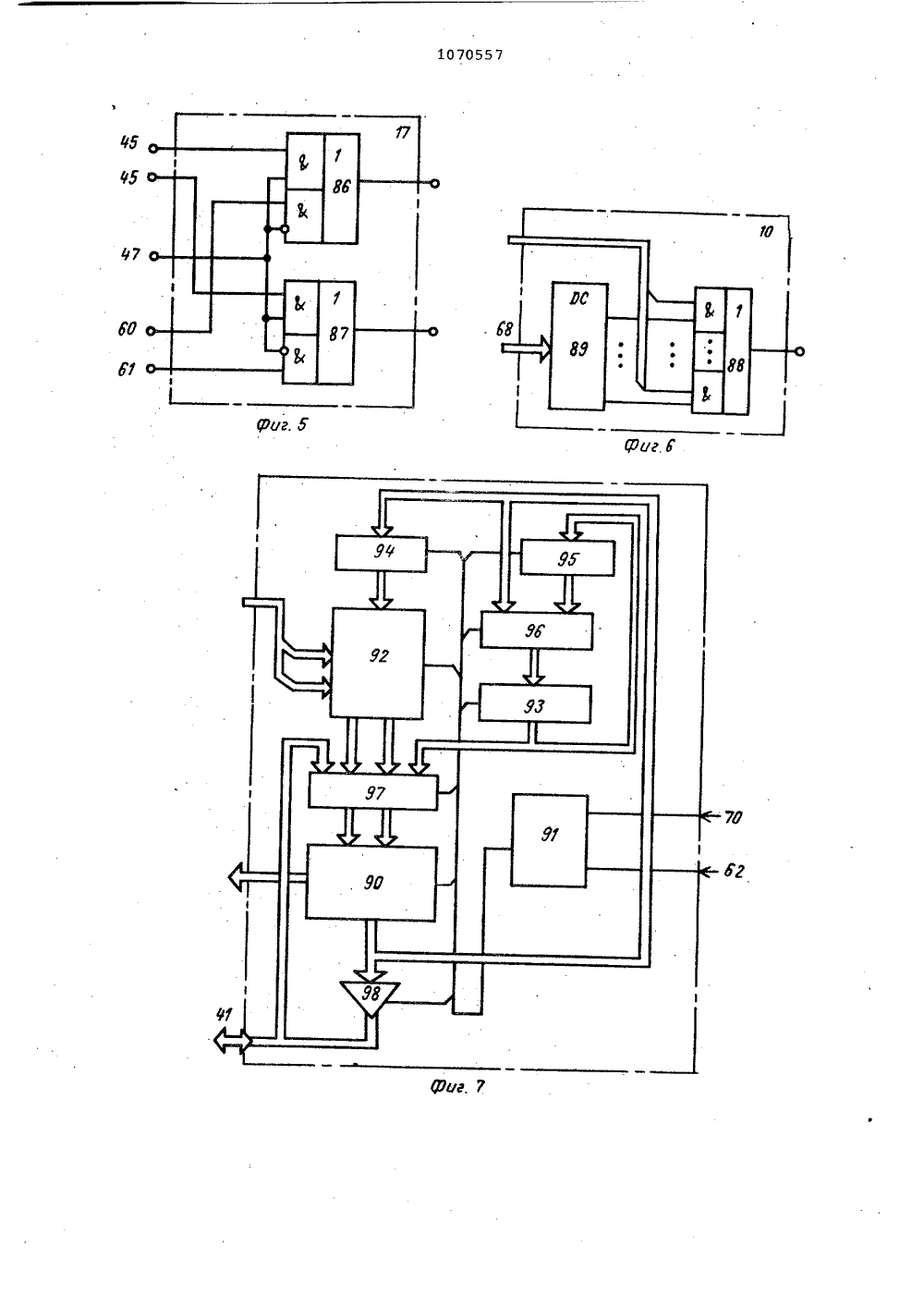

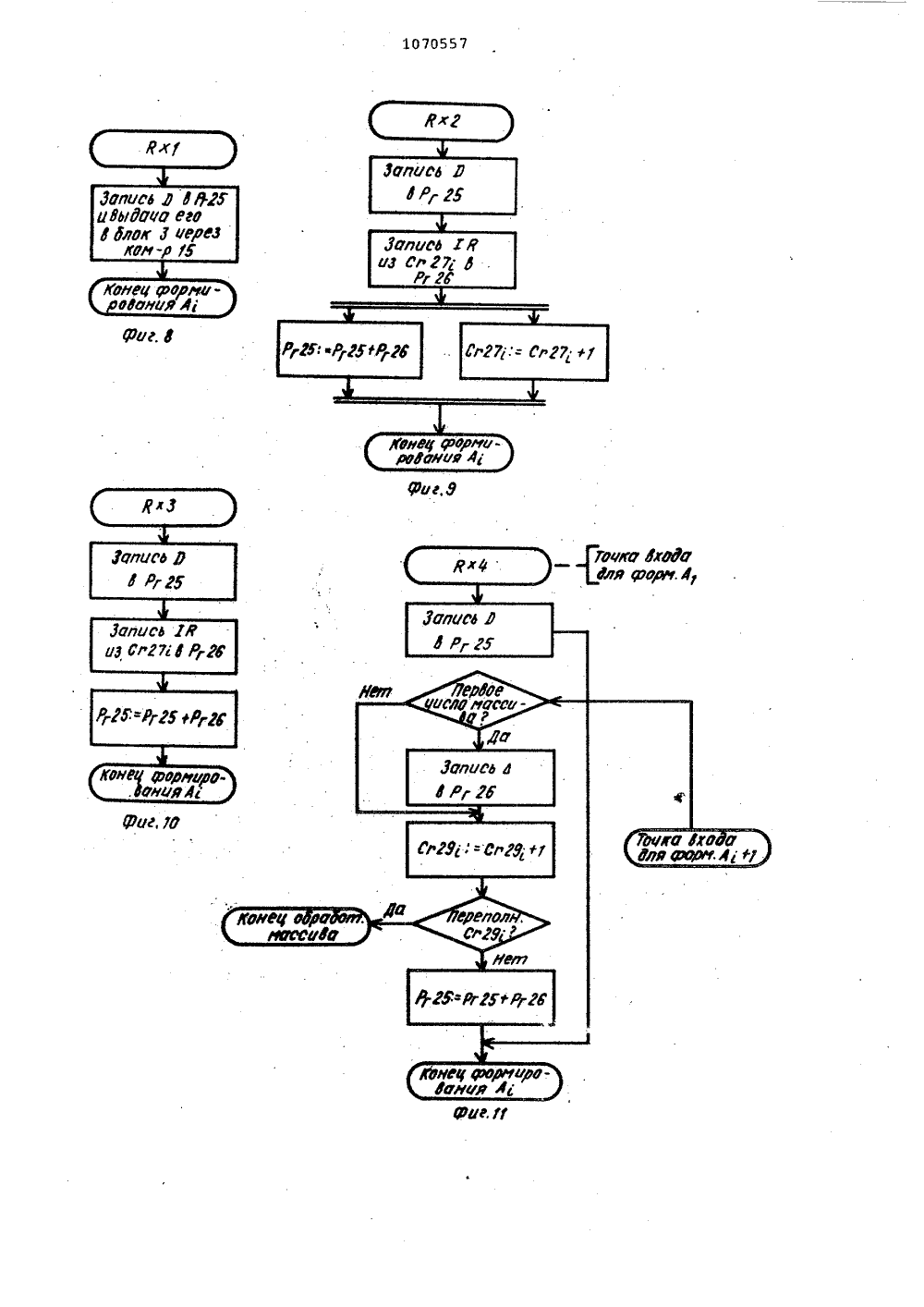

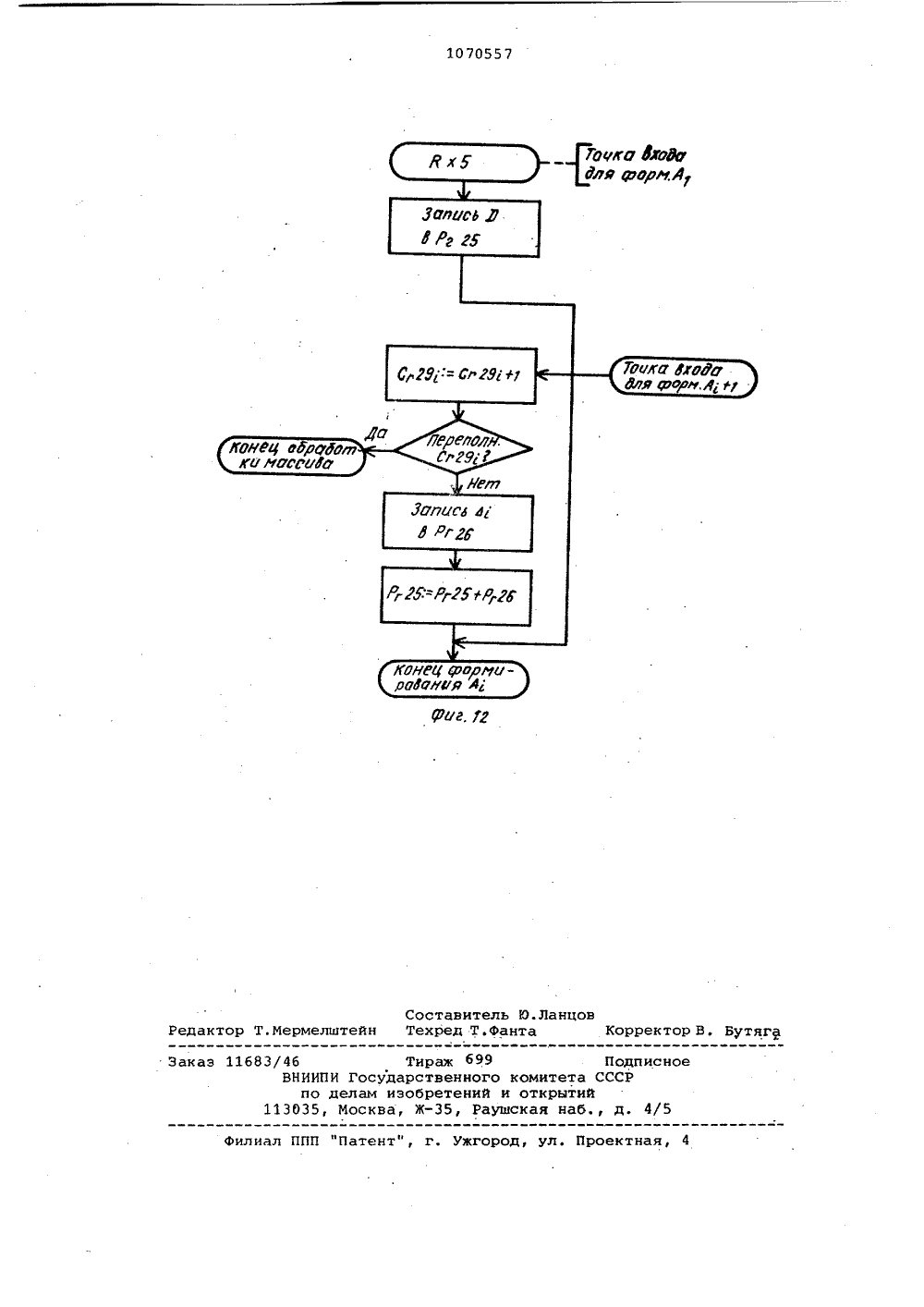

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСКИРЕСПУБЛИК 0557 19) а) 3(59 0 06 Г ЕТЕ ИЗ ИС СКОМУ СВ ЕЛЬСТВУ А 92809/18-24(21) 34 (22) 16 (46) 30 , (72) В. Л. И, Кор С. Н. Тка (53) 58 (56) 1. ов,Кривон моньки рченко обританииГ 15/00, опуб 19 2 Питании 15/00, опуб 14ик. тельство СССР15/00, 1979.тельство СССР8-24,07.80.(прото 66417 4. А зая ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ по вке М 2984194/1кл. 0 06 Р 15/00, 04.тип).(54)(57)1,МИКРОПРОГРАИИНЫЙ ПРОЦЕССОР,содержащий блок памяти команд, блокпамяти микрокоманд, блок оперативного запоминающего устройства, операционный блок, генератор тактовыхимпульсов, первый элемент ИЛИ, регистр адреса микрокоманд, счетчиккоманд, Формирователь микроопераций,выход модифицируемого разряда адреса следующей микрокоманды блока памяти микрокоманд соединен спервымвходом первого элемента ИЛИ, группавыходов кода операций Формирователямикроопераций соединена с группойвходов кода операций операционногоблока, первый выход генератора тактовых импульсов соединен с входомсинхронизации регистра адреса микрокоманд, о т л и ч а ю щ и й с ятем, что, с целью увеличения производительности за счет введения специальных режимов адресации данныхи динамического изменения форматакоманды, он содержит блок элементовИ, коммутатор адреса микрокоманд,мультиплексор логических условий,коммутатор индексов, второй элемент ИЛИ, коммутатор адреса оперативного запоминающего устройства, коммутатор управления оперативным запоминающим устройством, коммутатор данных, блок формирования исполнитель, ного адреса регистров общего назначения, состоящий из регистра адреса ции первого операнда, регистра адресации второго операнда, первого и второго коммутаторов операндов, пер. вого и второго блоков элементов И, блок формирования исполнительного адреса оперативного запоминающего устройства, состоящий из регистра исполнительного адреса, регистра с приращений, сумматора и коммутатора, блок индексных счетчиков, состоящий из группысчетчиков индексов, блок счетчиков циклов, состоящий из группы счетчиков циклов, блок пуска-останова, состоящий из элемента И и д триггера, причем управляющий вход процессора соединен с управляющими файф входами блока памяти команд, блока ВЫ элементов И и с первым входом второго элемента ИЛИ, выходы первой груп- ф пы управляющих выходов формирователя микроопераций соединены соответственно с вторым входом второго элемента ИЛИ, со счетными входами, вхо- (Я дами синхронизации счетчиков циклов и со счетным входом счетчикакоманд, вторая группа управляющих выходов формирователя микроопераций соединена со счетными входами и входами синхронизации счетчиков индексов, группа информационных входов которых соединена через шину команд с группой выходов блока памяти команд, с группой информационных выходов блока элементов И, с первой группой инФормационных входов коммутатора индексов, с группой информационных входов регистра адресации первого операнда и регистра адресации второ 15 1070557приращений, Во втором цикле исполнения данной команды производится продвижение индекса в счетчике 27 индекса и одновременно просуммированное значе. ние смещения индекса на сумматоре 30 через коммутатор 16 поступает в регистр 25 исполнительного адреса и фиксируется в нем. В третьем цикле исполнения данной команды производится выборка числа (или запись) иэ блока 3 по исполнительному адресу и подача (или прием ) его в операционный блок 9, в котором оно обрабатывается в соответствии с кодом операции, подаваемым с выхода 62 блока 5 на вход кода операции операционного блока 9, Если данная команда оказывается короткой (типа сложения), то третий цикл ее исполнения является последним, в котором производится выборка очередного ко мандного слова из блока 1 памяти команд, при этом на выходе 50 конца команды блока 5 вырабатывается сигнал, определяющий конец команды и настраивающий коммутатор 11 адреса 25 микрокоманд на прием кода операции команды в регистре 24 в качестве адреса микрокоманды. Во всех. циклах, когда сигнал конца команды отсутствует, в регистре 24 адреса микрокоман ды записывается адрес очередной микрокоманды с соответствующего выхода блока 2 памяти микрокоманд. Таким образом, короткая команда в режиме РХ 2 выполняется за три машинных цик ла, В то же время короткая команда в режиме РХ 1 выполняется за один машинный цикл (фиг. 10 и 9 ). Команды типа РХЗ реализуются аналогично командам Р Х 2, но без продвижения 40 индекса (фиг. 11).Команды типа РХ 4 и РХ 5 предназначены для обработки массивов информации,с шагом выборки чисел большим единицы, что необходимо при решении задач классификации и сортировки.Адрес первого числа задается аналогично описанному для команд формата КХ 1. Для формирования адресов второго и последующих чисел микро- программно иэ блока 1 памяти считывают значения величины шага й . Причем для режима Р Х 4 считывание выполняется один раз, а для режима РХ 5 значение шага считывается иэ блока 1 при обработке у каждого чис ла массива и очередной исполнительный адрес числа формируется суммированием значения предыдущего исполнительного адреса и значения д ( д в режиме РХ 5). Число слов, обраба тываемых в массиве чисел, задается дополнением до переполнения т-го ( 1 = 1, 2, , и) счетчика 29 циклов заранее аналогично загрузке счетчиков 27 индексов и при выполнении ин 65 струкции обработки массива чиселпроизводится проверка условия переполнения соответствующего -го счет.чика 29 циклов в мультиплексоре 10логических условий. При переполнении -го счетчика 29 циклов производится модификация адреса микрокоманды, что приводит к выходу иэ выполнения соответствующей инструкции,при этом продвижение -го счетчика29 циклов производится параллельнос выработкой А на сумматоре 30.Таким образом, предлагаемый микропрограммный процессор обладает широкими возможностями адресации смалыми затратами времени на их реализацию, особенно для обработки массивов данных, например, в режимеРХ 4, для формирования исполнительныхадресов для К чисел затрачиваетсяК + 1-й машинный цикл,Основные узлы и блоки процессораимеют следующее назначение.Блок 1 памяти команд предназначендля хранения программы вычислительного процесса, начальных адресовподпрограмм, значений индексов,риращений и смещений адресов . Выборкаиз него в режиме вычисления осуществляется по адресу, заданному в счетчике 28 команд. С выхода блока 1информация выдается в шину 38 команд.Кроме того, в режиме подготовкивычислений информация в шину 38 команд может поступать через блок 37элементов И, группы информационныхвходов 44 процессора. В этом случаесигналом с управляющего входа 42процессора блокируется блок 1 памяти, открывается блок 37 элементовИ и разрешается передача адреса команды с группы информационных вхо-дов 44 процессора в шину 38 команд и далее через коммутатор 14 индексов в счетчик 28 команд, управляемый синхросигналом записи со входа 42 черезэлемент ИЛИ 35.Блок 2 памяти микрокоманд предназначен для хранения микрокомандмикропрограмм управления выполнением команд вычислительного процесса.Блок 3 оперативного запоминающего устройства предназначен для хранения данных. Обращение к нему возможно как по адресу, задаваемому врегистре 25 исполнительного адреса,так и с группы адресных входов 45процессора в случаях разрешения внешнего доступа к оперативной памяти.Команды программы вычислений используются в форматах "регистр-регистр" и "регистр-память". Адресаоперандов 92 регистров общего назначения операционного блока 9При выполнении команд Формата "регистр-регистр" (Ю) адрес первого операнда заносится в регистр 22, второго - в регистр 23. Коммутаторы 12 и. 13 и блоки элементов И 32 и И 33 предназначены для динамического управления изменением командного слова. Структура их связей позволяет маскировать поля первого или вто. рого операндов командного слова, а также производить рокировку полей. Это дает возможность осуществлять обнуление регистров в блоке 92 регистров общего назначения (фиг. 7) ,в процессе или при завершении выполнеьия длинной команды ( деления, умножения и др.), используя только аппаратно-микропрограммные средства :без считывания из блока 1 памяти ко. манд, специально предназначенные для выполнения обнуления регистров 91, например команды вычитания с одним и тем же адресом первого и второго операндов. В данном случае обнуление выполняется соответствующей коммутацией блоком 4 регистров 22 и 23 микрокомандами микропрограм. мы выполнения длинной команды с обнулением регистров 92. Причем после соответствующей микропрограммной коммутации полей микропрограммно выполняется операцкя вычитания, после чего длинная .операция может продолжаться или завершаться. При выполнении команд формата "регнстр-память". (Р Х) в блок 9 передается только адрес, содержащийся в регистре 22, задающий адрес первого операнда Содержимое регистра 23 для операционного блока 9 безразлично.формирователь 5 микроопераций ( фиг. 2 ) предназначен для управления.и координации работы всех элементов и узлов процессора. С выхода 50 выдается сигнал микроонерации конца команды, который является разрешающим сигналом для приема кода команды в регистр 24 адреса микро- команды через коммутатор 11 с выхо-. да блока 1 памяти команд.Микрооперации, поступающие со вторСй группы управляющих выходов 51, осуществляют выдачу сигналов на синхровход илисчетный вход соответствующего счетчика 27 индекса в блоке б с целью записи в него значения индекса с выхода блока 1 памяти команд или увеличения его значения на единицу.Кодом с выхода 52 производится управление коммутатором 14 индексов ( фиг. 4). При этом в зависимости от значения сигналов микроопераций, поступающих на вход дешифратора 84, с выхода 52 формирователя 5 может осуществляться передача константы с выхода 19 (фиг. 1) в регистр 26 приращений, либо передача с выходаблока 1 кодов глубины циклов соответствующих счетчиков 29, начальныхадресов подпрограмм в счетчик 28 5команд, либо передача кодов в регистры 25,и 26, либо передача значения индексов (приращений шага индексации) в регистр 26 приращений.Микрооперации, поступаюцие с выходов третьей группы управляющих вы- (0 ходов, осуществляют следующие действия: с выхода 53 синхронизируют запись в регистры 22 и 23 адресацииоперандов по окончании выполнениятекущей команды и выборке следующей, (5 с выхода 54 (55 разрешается подстановка значения адреса второго (первого ) операнда вместо первого (второго ), с выхода 56 (57) запрещаетсяподача значения первого (второго)операнда через блок элементов И 32(33) в операционный блок 9, что соответствует адресации регистра общего назначения с нулевым адресом,позволяя использовать его в качестверабочего регистра.Микрооперации с первой группыуправляюцих выходов 58 осуществляютсинхронизацию записи информации всоответствующий счетчик 28 ( 291 блока 7, либо увеличивают значение кода счетчика 28 (291 на единицу.Микрооперации с выходов четвертойгруппы управляющих выходов осуцествляют следующие действия: с выхода59 разрешается передача информациив блок 3 оперативной памяти из операционного блока 9 через коммутатор18 данных (фиг. 3), с выхода 60 выдается сигнал разрешения внутреннейзаписи в блок 3 оперативной памяти 40 из операционного. блока 9,поступающий через коммутатор 17 в блок 3оперативной памяти, с выхода 61 разрешается внутреннее чтение информации из блока 3 памяти. С группы вы ходов 62 код реализуемой операции передается на операционный блок 9(Фкг. 7) .Микрооперации с выходов пятойгруппы управляющих выходов выполня ют сйедующие действия: с выхода63 (64) разрешается запись в регистр25 исполнительного адреса (регистр26 приращения ), с выхода 65 - передача из сумматора 30 или с выхода 55 коммутатора 14 в регистр 25 черезкоммутатор 16 в зависимости от отсутствия или наличия сигнала на выходе 65.Микрооперация с выхода 66 являет.60 ся сигналом разрешения доступа коперативной памяти извне. Этот сигнал через выход 47 выдается во внешние устройства, а также разрешает задание адреса обрацения к блоку 3 с группы адресных входов 45 процес 1070557 2030 сора, блокирует задание адреса данных с регистра 25, разрешает прохождение сигналов внешней записи и внешнего чтения через коммутатор 17 иосуществляет коммутацию шины внутренних данных с шиной внешних данных в коммутаторе 18.С группы выходов 68 в мультиплексор 10 поступает код проверяеьыхлогических условий (признаки переполнения счетчиков 29 и сигналы логических условий операционного блока 9).С выхода 49 блока 5 выдается сигнал прерываиия в случае появленияв микропрограмме незадействованныхсюоибочных ) кодов номеров счетчиковв блоках 27 и 29, а также неверномзадании номера регистра в блоке 8.Блок б счетчиков 27 индексов предназначен для задания значений индексов в режимах индексной адресацииданных. Начальные значения индексовхранятся в блоке 1 памяти к поступают в блок б через шину 38 команд.Блок 7 предназначен для задания 25адреса команды в счетчике 28, а так.же значений счетчиков циклов в счет.чиках 29, информация в которые поступают из блока 1 через коммутатор14.Блок 8 формирования исполнительного адреса оперативной памяти предназначен для аппаратно-микропрограм-.мной реализации всех режимов адресации данных в процессоре для командФорматов Рх,Операционный блок 9 (фиг. 7) предназначен для выполнения обработкиданных и может быть построен потиповой схеме, наПРимеР на микРопроцессорах 1804 ВС 1,Арифметико-логический блок 90осуществляет выполнение арифметических и логических операций. Блок 91местного, управления координируетработу всех узлов блока 9. Блок 92 45регистров содержит регистры общегоназначения, Мультиплексоры 94 . - 97предназначены для управления направлениями передачи и сдвигами информации в процессе обработки ее блоком9. Блок 98 элементов И предназначендля подключения выхода арифметикологического блока 90 к группе информационных входов-выходов данныхблока 9. 55Мультиплексор 10 логических условий фиг. б ) предназначен дляпроверки логических условий, поступающих на его вход с выходов операционного блока 9 и счетчиков 29 циклов.Номер проверяемого логическогоусловия задается кодом, поступающимс выхода 68 формирователя 5 на входдешифратора 89. 65 Алгоритм работы мультиплексораописывается выражением где- выходной сигнал мультиплексора 10;Е; - признак .)-го условия, подлежащего проверке;х; - значение 1-го условия.Коммутатор 11 адреса микрокоманд предназначен для управления приемом адреса очередной микрокоманды с выхода блока 1 памяти команд через шину 38 команд, задавая тем самым адрес первой микрокоманды микропрограммы при наличии сигнала конца предыдущей команды с выхода 50 формирователя 5, либо с выхода блока 2 памяти микропрограммы при отсутствии сигнала на выходе 50 формирователя 5.Коммутатор 14 индексов (фиг. 4) предназначен для управления передачей информации. С группы входов 19 констант на вторую группу входов коммутатора 14 поступает код константы. С выхода блока 1 памяти на первую группу входов, коммутатора 14 поступает код адреса команды для записи всчетчике 28 команд, либо код числа циклов для записи в счетчики 29 циклов, либо код значения приращения индекса для записи в регистр 26 приращения. С выхода блока счетчиков 27 индексов на третьюгруппу коммутатрра 14 поступает значение кода индекса для записи в регистр 26 приращения.Селекция информации в коммутаторе 14 осуществляется выходными сигна-, лами дешифратора 84 который управляется кодом с выхода 52 формирователя 5.При отсутствии сигналов на выходе дешифратора 84 выходным сигналом элемента ИЛИ-НЕ 85 разрешается передача информации с выхода шины 38 команд.При этом в зависимости от наличия управляющего сигнала на входе 42 процессора коммутатор может передавать либо. код адреса команды с группы информационных входов 44 процессора, когда сигнал на входе 42 присутствует, либо код адреса команды, число. циклов, значение индекса смещения или приращения в противном случае.Коммутатор 15 адреса, оперативной памяти предназначен для управления передачей адреса в блок 3 оперативного запоминающего устройства либо с регистра 25 исполнительного адреса при отсутствии сигнала разрешения внешнего доступа к оперативнойпамяти на выходе 66 формирователя 5,либо с группы входов 45 процессора,куда он поступает от внешнего устройства при условии разрешения внешнего доступа к блоку 3.Коммутатор 16 исполнительногоадреса предназначен для управленияпередачей исполнительного адреса врегистр 25 исполнительного адреса,При этом адрес передается с выходовсумматора 30 при отсутствии сигналана выходе 65 блока 5 или в противном случае с выхода. коммутатора 14индексов.Коммутатор 17 (фиг. 5) предназначен для коммутации сигналов управления (записи, считывания ) режимамиработы блока 3 оперативного запоминающего устройства.Коммутатор 18 данных (фиг. 3)предназначен для управления переда чей информации между блоком 3, операционным блоком 9 и шиной 40 внешних. данйых. Связи между этими тремяблоками устанавливаются путем соответствующего соединения между собой групп входов-выходов блока 80элементов И внутренних данных, блока 81 элементов И внешних данных иблока 82 элементов И. Формированиелиний связи осуществляется с помощьюкоммутатора 78 и блоков 80 - 82 элементов И. При отсутствии сигнала навходе 66 коммутатор 78 передает данные с группы входов-выходов блока80 на информационный вход коммутатора 8, в противном случае - с группами входов-выходов блока 81. При наличии сигнала на выходе 59 коммутатора 18 передача информации разрешается на выход блока 80 (выходы блока82 закрыты ), а при его отсутствиина выход блока 82 (выходы блока 80закрыты ). Передача информации навыход блока 81 производится толькопри наличии сигнала на входе 45 коммутатора 18 данных.Блок 20 пуска-останова предназначен для включения генератора 21 так. -товых испульсов по сигналу "Пуск",который поступает на вход 43 процессора. Останов генератора 21 осуществляется по сигналу конца работы,который формируется на выходе 67формирователя 5,Генератор 21 тактовых импульсОввыдает тактовЬе импульсы на выходах69 и 70 с постоянной частотой исмещением по фазе.Сумматор 30 предназначен длясложения кодов, заданных в регистре 625 исполнительного адреса и регистре 26 приращения.Элемент ИЛИ 36 предназначен длямодификации адреса очередной микрокоманды в соответствии с результаЧтами проверки логического условиймультиплексором 10.Устройство работает следующимобразом.. Процессор может функционировать втрех режимах: приема управляющейинформации о выполняемой программе;обработки информации и выполнениивычислений;, внешнего обмена.В первом режиме триггер 31 пускавыключен и генератор 21 тактовыхимпульсов не выдает тактовых импульсов, а выход блока 1 памяти командзаблокирован.По сигналу с управляющего входа42 открывается блок 37 элементов 4и с группы входов 44 адрес первойкоманды программы через шину ЗВ команд и коммутатор 14 записывается всчетчик 28 команд, запись в который 20 осуществляется также импульсом совхода 42, поступающим на синхровходсчетчика 28 команд через элементИЛИ 35. После этого процессор готовк началу работы во втором режиме, в 25 котором сигналы на управляющем входе 42 процессора отсутствуют и невырабатываются в дальнейшем.Во втором основном режиме работы процессора выполняется обработка 39 данных. Исходным состоянием для него является задание в счетчике 28адреса первой команды программы. Всеостальные элементы памяти находятсяв исходном состоянии, при котором навыходе 50 формирователя 5 присутствует сигнал, а остальные микрооперации отсутствуют, что соответствуетвыполнению холостого цикла в течениепервого машинного цикла.По сигналу пуска со входа 43 включается триггер 31 пуска и запускается генератор 21, формирующий тактовую сетку синхронизации работы процессора.45Иэ блока 1 памяти команд по первому тактовому импульсу с выхода 69генератора 21 считанная команда (кодоперации команды ) записывается врегистр 24 и адресует первую микрокоманду в блоке 2 памяти микрокоманд.5 О Таким образом, холостая микрокоманда позволяет процессору опреде"лить тип первой команды и начальныйадрес микропрограммы ее выполнения,а также произвести запись в регист ры 22 и 23 содержимого командногослова.Далее выполнение команды зависитот ее формата.Для команд формата РР сигналом О с выхода 53 формирователя 5 производится запись значений Р 1 и Р 2 врегистры 22 и 23 соответственно.Так как сигналы на выходах 54 - 57формирователя 5 отсутствуют, то со-держимое регистров 22 и 23 передает"ся на вход адресации регистров общего назначения фиг. 7 операционного блока 9 беэ изменения.Первая микрокоманда микропрограммы выполнения команды на группе выходов 62 Формирователя 5 задает код5реализуемой операции, который поступает в операционный блок 9В зависимости от характера выполняемзй операции в счетчики 29блока 7 может заноситься информацияо кратности реализуемых циклов, Вэтом случае по адресу, заданному всчетчике 28, считывается информацияиз блока 1 памяти, которая черезшину 38 команд и коммутатор 14 заносится в соотнетстнующий счетчик 29.Управление осуществляется микрооперациями с групп выходов 52 и 58формиронателя 5,При считывании информации из блока 1 памяти содержимое счетчика 28команд продвигается путем подачи сигналов на его счетный вход с соответ-ствующего выхода группы выходов 58формирователя 5. 25Рассмотрим режимы формированияисполнительного адреса для командФормата Р Х.В этом случае работа процессорааналогична описанному, но на вход 30операционного блока 9 передается со.держимое Р 1, хранящееся в регистре22. Содержимое регистра 23 в блоке9 не воспринимается, что определяется кодом операции, эадаваемым сгруппы выходов 62 формирователя 5.Формирование исполнительного адреса второго операнда происходитследующим образом,При выполнении команд форматаРХ 1 адрес второго операнда задаетсяв формате команды в виде смещенияД, значение которого (фиг. 9) черезкоммутаторы 14 и 16 записываетсяв регистр 25 исполнительного адреса и через коммутатор 15 выдается 45на адресный вход блока 3. Это осуществляется сигналом на выходе 63формирователя 5 (запись н регистре25) при отсутствии сигналов на выходе дешифратора 84 (фиг. 4 ) и на 50выходах 65 и 68 формирователя 5. Поэтому адресу н следующей микрокоманде осуществляют чтение или записьв блок 3 оперативного запоминающегоустройства. 55В режимах адресации с индексацией происходит запись значения смеще"ния иэ блока 1 памяти в регистр 25исполнительного адреса аналогичноописанному для режима прямой адресации, а формирование исполнительногоадреса второго операнда указано вышепри оп исании режимов Р Х.Перед реализацией режимов адресации данных с индексацией (типц РХ 2- 65 РХ 3 ) производится предварительное занесение значения индекса в один иэ счетчиков 27 индекса, а значение глубины цикла (дополнение ) - н счетчик 29. При этом адрес индекса или дополнения сетчика циклов до количества слов, обрабатываемых в массиве, в блоке 1 памяти задается счетчиком 28. По сигналам микрооперации с соответствующей группы выходов 51 разрешается запись значения индекса н нужный счетчик 27 индекса, а дополнения счетчика циклов - в счетчик 29 циклов при выполнении команд загрузки счетчиков 27 и 29. По следующим микрокомандам реализуется один из возможных режимов адресации с индексацией.В режиме РХЗ по следующей микрокоманде производится перезаписьзначения индекса из соответствующего счетчика 27 через коммутатор 14 в регистр 26 приращения. Управление осуществляется сигналами микроопераций с группы выходов 52 и с выхода 64 формирователя 5. В следующей микрокоманде по микрооперации с выхода 63 формирователя 5 осуществляется запись в регистр 25 значения исполнительного адреса, равного сумме индекса и смещения, с выхода сумматора 30 через коммутатор 16.В режиме РХ 2 адресации с индексацией и продвижением индекса необходимо осуществлять параллельно с выдачей исполнительного адреса числа увеличение значения индекса на единицу. В данном режиме Формирование исполнительного адреса числа осуществляется аналогично режиму адресации с индексацией без продвижения индекса за исключением того, что в цикле записи исполнительного адреса с выхода сумматора 30 через коммутатор 16 в регистр 25,;по микрооперации с соответствующего выхода группы выходов 51 формирователя 5 производится увеличение значения нужного счетчика 27 индексов и счетчика 29 циклов на единицу, причем на мультиплексоре 10 логических условий производится проверка счетчика 29 циклов, адрес микрокоманды модифицируется и производится выход из микропрограммы.При выполнении адресации с индексацией с постоянным шагом РХ 4 исполнительный адрес первого числа Формируется аналогично описанному для режима прямой адресации (фиг.11), Значение величины шага по адресу, заданному в счетчике 28, считывается из блока 1 памяти и записывается через коммутатор 14, управляемый сигналом с соответствующего выхода группы выходов 52 формирователя 5,н регистр 26 приращения по сигналу с выхода 64 формирователя 5.По очередной микрокоманде формируется второй исполнительный адрес массива на основе сложения содержимых регистров 25 и 26 на сумматоре 30 с последующей записью н регистр 25 исполнительного адреса.Аналогично второму формируются и последующие исполнительные адреса, при этом аналогично режимам ЙХ 2 и ДХЗ производится проверка услония переполнения )-го счетчика 29 циклов указывающего на окончание обработки массива чисел.В режиме адресации с переменным шагом(РХ 5) формирование первого и второго исполнительных. адресов осу- ществляется аналогично описанному для режима индексной адресации с постоянным шагом.Для формирования адреса третьеГо и последующих чисел осуществляется считывание по даресу, заданному н счетчике 28, из блока 1 памяти значения приращения для данного числа и запись его в регистр 26 индекса, что на фиг. 12 показано с перенесением блока загрузки Ь, в регистр 26 после блока проверки условия переполнения счетчика 29. По следующей микрокоманде происходит сложение на сумматоре 30 содержимого регистров 25 и 26 и запись сформированного таким образом исполнительного адреса в регистр 25.После сформирования исполнительного адреса второго операнда операционный блок 9 может приступить к выполнению операции.Для выполнения операции, связанных со считыванием из блока 3 оперативного запоминающего устройства содержание этого блока по адресу, заданному в регистре 25, считывается через коммутатор 18 данных на информационную шину 41. После этого операционный блок 9 выполняет соответствующую операцию, При выполнении операций, связанных с записью данных в блок памяти, содержимое регистра 25 определяет адрес, по которому производится запись данных в блок 3 оперативного запоминающего устройства.Управление внутренней передачей данных между блоком 3 и операционным блоком 9 осуществляют микрооперации50 55 Таким образом, предлагаемый микропрограммный процессор обладает широкими функциональными возможностями благодаря широкому набору режимов адресации, позволяющих обрабатывать большие массивы данных с более нысокой производительностью, чем в известном устройстве. ф с выходов 60 (внутренняя запись вблок 3), 61 (внутреннее чтение иэблока 3), 59 ( управление записью)формирователя 5 микроопераций5При выполнении некоторых опера"ций в течение нескольких тактов работа может осуществляться операционным блоком 9 без обращения к блоку3. С началом такого режима с выхода 66 формирователя 5 выдается сиг нал микрооперации, разрешающийвнешний доступ к блоку 3 оперативного запоминающего устройства, определяятретий режим работы процессора.Этот сигнал поступает на выход 15 47 процессора и передается, напримерв процессор высшего уровня управления, а также на входы коммутаторов15, 17 и 18. При этом коммутатор 15пропускает адрес обращения к блоку 3 20 с грУппы входов 45 процессора, коммутатора 17 н зависимости от сигналон (записи или чтения ) поступающих с управляющих разрядов группывходов 45 (фиг. 5 ), выдает н блок 3сигнал записи или чтения, а коммутатор 18 формирует такт снязи черезвнутренние ЗЭ и внешние 40 шины дан, ных, тем самым соединяя группу входов-выходов 46 внешних данных процессора через шину 39 внутреннихданных с группой входов-выходов блока 3.По окончании такого режима естест.венного ожидания процессора сигналс выхода бб формирователя 5 снимается и процессор продолжает работатьаналогично описанному.В последней микрокоманде команды,выполняемой процессором программы,с выхода 67 формирователя 5 выдается 40 сигнал микрооперации окончания работы, который с выхода 48 процессорапередается, например, в процессорвысшего уровня управления и черезэлемент И 34 устанавливает триггер 45 31 в нулевое состояние, что приводитк отключению генератора 21 и прекращению работы процессора в целом.го операнда и с первой группой информационных входов коммутатора адресамикрокоманды, вторая группа информационных входов которого соединена свыходом первого элемента ИЛИ и сгруппой выходов немодифицируемой части адреса следующей микрокомандыблока памяти микрокоманд, вход адреса которого соединен с информационным выходом регистра адреса микрокоманд, информационный вход которогосоединен с выходом коммутатора адреса микрокоманды, управляющий входкоторого соединен с выходом концакоманды формирователя микроопераций,группа выходов управления коммутатором индексов которого соединена сгруппой управляющих входов коммутатора индексов, вторая группа информационных входов которого соединена сгруппой входов констант устройства,группа информационных выходов грунпы счетчиков индексов соединена стретьей группой информационных входов коммутатора индексов, группа инФормационных выходов которого соеди.нена с группами информационных входов счетчика команд группы счетчиков циклов, регистра приращений и спервой группой информационных входовкоммутатора блока Формирования исполнительного адреса оперативногозапоминающего устройства, группа информационных выходов которого соединена с группой информационных входоврегистра исполнительного айреса,группа информационных выходов которого соединена с первой группой входов сумматора и первой группой информационных входов коммутатора адре.са оперативного запоминающего устройства, группа информационных выходов которого соединена с группой адресных входов блока оперативного запоминающего устройства, управляющиевходы которого соединены с выходамикоммутатора управления оперативнымзапоминающим устройством, первыйуправляющий вход которого соединенс управляющим входом коммутатораадреса оперативного запоминающегоустройства, с первым управляющимвходом коммутатора данных и выходомразрешения внешнего доступа к блокуоперативного запоминающего .устройства процессора и формирователя микро.операций, выход конца работы процессора которого соединен с первымвходом элемента И блока пуска-останова, второй вход которого соединенсо вторым выходом генератора такто"вых импульсов, с входом синхронизации операционного блока и с первымуправляющим входом формирователямикроопераций, второй управляющийвход которого соединен с первымвыходом генератора тактовых импульсов, управляющий вход которого соединен с выходом триггера блока пуска-останова, вход установки в ноль которого соединен с выходом элемента И блока пуска-останова, вход установки в единицу триггера блока пуска-останова соединен с входом пуска процессора, группа выходов по.ля кода логических условий Формирователя микроопераций соединена с группой управляющих входов мультиплексора логических условий, группа информационных входов которогосоединена с группой информационныхвыходов группы счетчиков циклов игруппой информационных выходов операционного блока, группа адресныхвходов которого соединена с группами выходов первого, второго блоковэлементов И и блока формирования исполнительного адреса регистровобщего назначения, выход кода микро.операций блока памяти микрокомандсоединен с информационным входомформирователя микроопераций, первый второй, третий, четвертый и пятый выходы третьей группы управляющих выходов которого соединены соответственно с входами синхронизации регистра адресации первого операнда,регистра адресации второго операнда, с управлякщим входом первого коммутатора операндов, с управляющим вхо.дом второго коммутатора операндов,с управляющим входом первого блока элементов И и с управляющим входом второго блока элементов И, первый, второй и третий выходы четвертой группы управляющих выходов Формирователя микроопераций соединены соответственно с вторым управляющим входом коммутатора данных, с вторым управляющим входом коммутатора управления оперативным запоминающим устройством и с третьим управляющим входом коммутатора управления оперативным запоминающим устройством, первый, второй и третий выходы пя- той группы управляющих выходов Формирователя микроопераций соединены соответственно с входом синхронизации:регистра исполнительного адреса, с входом синхронизации регистра приращений и с управляющим входом коммутатора, блока формирования исполнительного адреса оперативного запоминающего устройства, втораягруппа информационных входов которого соединена с группой выходов сумматора, вторая группа входов которого соединена с группой информационных выходов регистра приращений, группа информационных выходов регистра адресации первого операнда и группа информационных выходов регистра адресации второго операнда соединены соответственно с первыми и1070557 Составитель Ю.Ланцовактор Т.Мермелштейн Техред Т.фанта Корректор В, Бутя илиал ППП "Патент", г. Ужгород, ул. Проектная,каз 11683/46 ВНИИП по 113035, Тираж 699 Государственног лам изобретений осква, Ж, Ра Подписномитета СССРоткрытийкая наб., д. 4/51070557 вторыми группами информационных входов первого и второго коммутаторов операндов, группы информационных выходов которых соединены соответственно с группой входов первого и второго блоков элементов И, группа адресных входов процессора соединена с второй группой информационных входов коммутатора адреса оперативного запоминающего устройства, один из входов группы адресных входов процессора соединен с четвертым управляющим входом коммутатора управления оперативным запоминающим устройством, а другой соединен с пятым управляющим входом коммутатора управления оперативным запоминающим устройством и с третьим управляющим входом коммутатора данных, первая, вторая и третья группы информационных входов-выходов которого соединены соответственно с группой информационных входов-выходов внешних данных процессора, оперативного запоминающего устройства и операционного блока, группа информационных выходов счетчика команд соединена с группой адресных Входов блока памяти команд, выход мультиплексора логических условий соединен с вторым входом первого элемента ИЛИ, группа информационных входов процессора соединена с группой информационных входов блока элементов И, выход прерывания формирователя микроопераций образует выход прерывания процессора, а выход второго элемента ИЛИ соединен с входом синхронизации счетчика команд,2. Процессор по п, 1, о т л и ч а ю щ и й с я тем, что формирователь микроопераций содержит регистр, первый, второй и третий дешифраторы, первый и второй элементы И, элемент ИЛИ, первый вход которого соединен .с первым выходом первого дешифратора, группа информационных входов которого соединена с первой группой выхода регистра, вторая группа выходов которого соединена с группой информационных входов второго дешифратора, управляющий вход которого соединен с управляющим входом третьего дешифратора, с первыми входами первого и второго элементов И, с входом синхронизации регистра и с первым управляющим входом ФормироватеИзобретение относится к автоматике и вычислительной технике н может быть использовано при построении ля, третья группа выходов регистрасоединена с информационным входомтретьего дешифратора, первая группавыходов которого соединена с первойгруппой входов элемента ИЛИ, втораягруппа входов которого соединена спервой группой выходов второго дешифратора, управляющий вход первого дешифратора соединен с вторым управляющим входом формирователя, первыйвыход регистра соединен с вторымвходом второго элемента И и с выходом конца команды формирователя,первая и вторая группы управляющихвыходов формирователя соединены соответственно с второй группой выходов второго дешифратора, и с второй группой выходов третьего дешифратора, первый, второй, третий, четвертый и пятый выходы третьей группыуправляющих выходов Формирователя соединены соответственно с выходом.второго элемента И, с вторым, треть. им, четвертый и пятым выходами регистра, шестой выход регистра соеди. нен с вторым входом первого элемента И и с первым выходом четвертой группы управляющих выходов формиро- , вателя, второй и третий выходы четвертой группы управляющих выходов которого соединены соответственно с .выходом первого элемента И и с седьмым выходом регистра, первый, второй и третий выходы пятой группы управляющих выходов Формирователя соединены соответственно с вторым выходом первого дешифратора, с третьим выходом первого дешифратора и с восьмым выходом регистра, четвертая, пятая и шестая группы выходов которого соединены соответственно с груп" пой выходов кода операций Формирователя, с группой выходов управления коммутатором индексов формирователя и с группой выходов поля кодов логических условий формирователя, девятый и десятый выходы регистра и вы. ход элемента ИЛИ соединены соответственно с выходом разрешения внешнего доступа к оперативному запоминающему устройству формирователя, с выходом конца работы процессора формирователя и выходом прерывания формирователя, информационный вход регист ра соединен с информационным входом- формирователя,ЭВМ и вычислительных систем с м 0 крспрограммным управлением и высокимбыстродействием.Известны микропрограммные процес" сори, содержащие память команд, память микрокоманд, регистр адреса микрокоманд, оперативную память, операционный блок и счетчик команд 1, (.2 3 ГЗ,)Йедостатками таких устройств являются узкая область применения и низкое быстродействие.Наиболее близким к предлагаемому по технической сущности и достигае- мому положительному эффекту является микропрограммный процессор, содержащий операционный блок, оперативное запоминающее устройство, счетчик команд, блок микропрограммного управления, постоянное запоминаю" щее устройство, триггер режима, пять элементов И, дешифратор идентификации, триггер прерываний, два элемента ИЛИ, элемент ИЛИ-НЕ, группу элементов И, причем первые выходы блока микропрограммного управления соединены спервыми входами операционного блока, первые выходы которого соединены через оперативное запоминающее устройство с вторыми входами операционного блока, вторые выходы соединены с входами счетчика команд, выходы которого соединены с третьими входами операционного блока и первыми входами группы элементов И, вторые входы которой соединены с третьим выходом операционного блока, а управляющие входы подключены к первому выходу триггера, режима, первый вход которого соеди-, нен с четвертым выходом операционно- го блока, а второй вход соединен С пятым выходом операционного блока, выходы группы элементов И соединены с входами постоянного запоминающего устройства команд операционной системы, выходы которого подключены к четвертым входам операционного блока, шестые выходы которого .соединейй с первыми входами блока микропрограммного управления, а пятый вход соединен с первым выходом триггера прерываний, второй выход которого подключен к второму входу блока микропрограммного управления, второй вход соединен с входом устройства, а первый вход соединен с выходом первого элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, второй вход соединен с выходом второго элемента И, третий вход соединен с выходом третьего элемента И четвертый вход соединен с выходом четвертого элемента И, а пятый вход подключен к выходу пятого элемента И, первый вход которого соединен с первым выходом триггера режима, а второй вход соединен с первым выходом постоянного запоминающего .устройства микрокоманд, первым4 О д,.:ж э, м=м+, е ,),где й - мощность множества исполнительных адресов;с постоянным шагом Ь(Ь1) приращения индекса, когда исполнительный адрес А, формируется на основе значения А;и шага д по формулеА =Д(4 е 1;)Ч ) приращения ийдексада исполнительный адрес А; Формиется на основе значения А)и55 шагапо ФормулеМ:Д ог.УЬ 1.,е 2 Д-д,анные режимы формирования рактерны при решении зада ки больших массивов данны м масштабе времени. Отсут аратно-микропрограммных реализации этих режимов О Указреса ха обработ реально вие апп 5. средств ривходом элемента ИЛИ-НЕ и первым входом второго элемента ИЛИ, выход которого подключен к первому входупервого элемента И, второй вход которого соединен с первым выходомдешифратора идентификации, второй выход которого соединен с первым входом второго элемента И, второй входкоторого соединен с выходом элемента ИЛИ-НЕ и первым входом третьегоэлемента И, второй вход которого,соединен с третьим выходом дешифратора идентификации, вход которогосоединен с вторыми выходами блокамикропрограммного управления, третьи 15 выходы которого подключены к входупостоянного запоминающего устройствамикрокоманд, вторые выходы которогосоединены с третьими входами блокамикропрограммного управления, а тре- ;Я тий выход соединен с вторым входомвторого элемента ИЛИ, вторым входомэлемента ИЛИ-НЕ и первым входом четвертого элемента И, второй вход которого подключен к второму выходу 25 трйггера режима (.43Недостатками известного устройства являются узкая область применения и низкая производительность.Узкая область применения обуслов- ЗО лена недостаточной номенклатуройдисциплин формирования исполнительного адреса. Например, в данномустройстве не реализованы специальные режимы индексной адресации;с продвижением индекса, когдаисполнительный адрес А; формируетсяна основе значения индекса ЭР изначения смещения Д в соответствиис соотношениемгь фг 4 60 6т =Е Ф, (6) водит к существенному сужению области применения известного устройства.Низкая производительность устройства обусловлена тем, что реализация специальных режимов адресации данных требует обращения к подпрограммам Формирования исполнительных адресов для этих режимов, что требует значительных затрат времени на обращения к ОЗУ ЭВМ.Формирование исполнительного адреса в режиме индексной адресации с продвижением индекса требует вре- мени Т которое оценивается по Формуле где 11 - время выборки значения индекса иэ ОЗУ;1 г - время выполнения сложения7 Р иЗ;1 з - время увеличения значенияиндекса на 1;1 - время выдачи Авремя запоминайия в ОЗУпродвинутого индекса;время обращения к подпрограмме формирования исполни. 30тельного адреса в данномрежиме.На Формирование исполнительного адреса в режиме индексной адресации с постоянным шагом приращения 35 индекса требуется время Тг, оцениваемое по формуле время считывания из ОЗУ зна чения А; ;время считывания из ОЗУ зна. чения шага двремя сложения А;и Д время записи в ОЗУ значения Авремя выдачи А 50) фвремя обращения к подпрограмме формирования исполнительного адреса в данном режиме. При использовании режима индексной адресации с переменным шагом приращения индекса время формирования исполнительного адреса Т оце 3 нивается по формуле где , - время записи в ОЗУ значения Авремя Формирования адресашага Ьвремя считывания из ОЗУзначения А,.время сложения А;, и Ьвремя выдачи Авремя обращения к подпрог 36рамме Формирования исполнительного адреса в данномрежиме.Анализ выражений (4 ) - (6) показывает, что доминирующими величинами в них являются слагаемые, связанные с частыми операциями обращения к ОЗУ, что приводит к существенному снижению производительности процессора. Это особенно ощутимо при резком возрастании интенсивности использования указанных режимов адресации при обработке больших массивов данных, приводящем к снижению системной производительности эа счет частых обращений к ОЗУ.Таким образом, низкая производительность известного устройства обусловлена высокой чувствительностью к изменению рабочей нагрузки при переходе к выполнению обработки больших массивов данных, доля которой превышает 50 объема алгоритмов решения таких задач.Поскольку в известном устройстве отсутствуют элементы и связи для аппаратно-микропрограммной реализации указанных режимов адресации, повышение производительности в нем невозможно.Цель изобретения в .расширение области применения путем введения специальных режимов адресации данных и динамического изменения формата команды и повышение производительности микропрограммного процессора.Поставленная цель достигается тем, что в микропрограммный процессор, содержащий блок памяти команд, блок памяти микрокоманд, блок оперативного запоминающего устройства, операционный блок, генератор тактовых импульсов, первый элемент ИЛИ, регистр адреса микрокоманд, счетчик команд, формирователь микроопераций, причем выход модифицируемого разряда адреса следующей микрокоманды блока памяти микрокоманд соединен с первым входом первого элемента ИЛИ, группа выходов кода операций формирователя микроопераций соединена с группой входов кода операций операционного блока, первый выход генератора тактовых импульсов соединен с входом синхронизации регистра адреса микрокоманд, введены блок элементов И, коммутатор адреса микрокоманд мультиплексор логических условий,1070557 51015 20 25 30 коммутатор индексов, второй элемент ИЛИ, коммутатор адреса оператинного запоминающего устройства, коммутатор управления оперативным запоминающим устройством, коммутаторданных, блок формирования исполнительного адреса регистров общего назначения, состоящий из регистра адресации первого операнда, регистра адресации второго операнда, первого и второго коммутаторов операндов,первого и второго блоков элементовИ, блок формирования исполнительного адреса оперативного запоминающего устройства, состоящий из регистра исполнительного адреса, регистра приращений, сумматора и коммутатора,блок индексных счетчиков, состоящий из группы счетчиков индексов, блоксчетчиков циклов, состоящий из группы счетчиков циклов, блок пуска-останона, состоящий из элемента И итриггера, причем управляющий входпроцессора соединен с управляющимивходами блока памяти команд, блокаэлементов И и с первым входом второго элемента ИЛИ, выходы первойгруппы управляющих выходов формирователя микроопераций соединены соответственно с вторым входом второго элемента ИЛИ, со счетными входами,входами синхронизации счетчиков циклов и со счетным входом счетчикакоманд, вторая группа управляющих выходов формирователя микроопераций соединена со счетными входами и входами синхронизации счетчиков индексов, группа информационных входов 35 40 45 50 55 60 65 которых соединена через шину команд с группой выходов блока памяти команд, с группой информационных выходов блока элементов И, с первойгруппой информационных нходон коммутатора индексов, с группой информационных входов регистра адресациипервого операнда и регистра адресации второго операнда и с первойгруппой информационных входов коммутатора адреса микрокоманды, втораягруппа информационных входов которого соединена с выходом первого элемента ИЛИ и с группой выходов немодифицируемой части адреса следующеймикрокоманды блока памяти микрокоманд, вход адреса которого соединенс информационным выходом регистраадреса микрокоманд, информационныйвход которого соединен с выходом коммутатора адреса микрокоманды, управляющий вход которого соединен свыходом конца команды формирователя микроопераций, группа выходон управления коммутатором индексов которого соединена с группой управляющих входов коммутатора индексов, втораягруппа информационных входов которого соедииена с группой входов конс тант устройства, группа информационных выходов группы счетчиков индексон соединена с третьей группой информационных нходон коммутатора индексон, группа информационных выходов которого соединена с группамиинформационных входов счетчика команд группы счетчиков циклов, регист.ра приращений и с первой группой информационных входов коммутатора блока формирования исполнительного адреса оперативного запоминающего устройства, группа информационных выходов которого соединена с группой информационных входов регистра исполнительного адреса, группа информационных выходов которого соединена сгервой группой входов сумматора и первой группой информационных входов коммутатора адреса. опера ти нного з апоминающего устройства, группа информационных выходов которого соединена сгруппой адресных входов блока оператинного запоминающего устройства, управляющие входы которого соединеныс выходами коммутатора управления.оперативным запоминающим устройством, первый управляющий вход которого соединен с управляющим входомкоммутатора адреса оперативного запоминающего устройства, с первымуправляющим входом коммутатора данных и с выходом разрешения внешнего доступа к блоку оперативного запоминающего устройства процессора иформирователя микроопераций, выходконца работы процессора которого соединен с первым входом элемента Иблока пуска-останова, второй входкоторого соединен со вторым выходомгенератора тактовых импульсов, свходом синхронизации операционногоблока и с первым управляющим входомформирователя микроопераций, второйуправляющий вход которого соединенс первым выходом генератора тактовых импульсов, управляющий вход которого соединен с выходом триггераблока пуска-останова, вход установки в ноль которого соединен с выходом элемента И блока пуска-останова, вход установки в единицу триггера блока пуска-останова соединенс нходом пуска процессора, группа выходов поля кода логический условийформирователя микроопераций соединена с группой упранляющих входов мультиплексора логических условий, группа информационных входов которогосоединена с группой информационныхвыходов групы счетчиков циклов игруппой информационных выходов операционного блока; группа адресныхвходов которого соединена с группами выходов первого и второго блоковэлементов И блока формирования исполнительного адреса регистров общего назначения, выход кода микроопераций блока памяти микрокоманд соединен с информационным входом формирователя микроопераций, первый, второй, третий, четвертый и пятый выходы третьей группы управляющих выхдов которого соединены соответственно с входами синхронизации регистраадресации первого операнде, регистра адресации второго операнда, суправляющим входом первого коммутатора операндов, с управляющим входом первого блока элементов И и суправляющим входом второго блокаэлементов И, первый, второй и третивыходы четвертой группы управляющихвыходов формирователя микрооперацийсоединены соответственно с вторымуправляющим входом коммутатора данных с вторым управляющим входом коммутатора управления оперативным запоминающим устройством и с третьимуправляющим входом коммутатора управления оперативным запоминающимустройством, первый, второй и третий выходы пятой группы управляющихвыходов. формирователя микрооперацийсоединены соответственно с входом,синхронизации регистра исполнительного гдреса, с входом синхройизации регистра приращений и с управляющим входом коммутатора, блокаформирования исполнительного адресаоперативного запоминающего устройства, вторая группа информационныхвходов которого соединена с группойвыходов сумматора, вторая группа.входов которого соединена с группойинформационных выходов регистра приращений, группа информационных выходов регистра адресации первого операнда и группа информационных выходов регистра адресации второго операнда соединены соответственно спервыми и вторыми группами информационных входов первого и второгокоммутаторов операндов, группы информационных выходов которых соединенысоответственно с группой входов первого и второго блоков элементов И,группа адресных входов процессорасоединена с второй группой информационных входов коммутатора адресаоперативного запоминающего устройства, один из входов группы адресныхвходов процессора соединен с четвертым управляющим входом коммутаторауправления оперативным запоминающимустройством, а другой соединен с пятым управляющим входом коммутаторауправления оперативным запоминающимустройством и с третьим управляющимвходом коммутатора данных, первая,вторая, и третья группы информационных входов-выходов которого соединены соответственно с группой информа"ционных входов-выходов внешних данных процессора, оперативного запоминающего устройства и операционногоблока, группа информуционных выхо- .дов счетчика команд соединена с груп.пой адресных входов блока памяти коо- манд, выход мультиплексора логических условий соединен с вторым входомпервого элемента ИЛИ, группа информационных входов процессора соедине"на с группой информационных входовблока элементов И, выход прерыванияформирователя микроопераций образуетвыход прерывания процессора, а выходвторого Элемента ИЛИ соединен с вхой 5 дом синхронизации счетчика команд.Кроме того, формирователь микроопераций содержит регистр, первый,второй и третий дешифраторы, первыйи второй элементы И, элемент ИЛИ,первый вход которого соединен с пер 20 вым выходом первого дешифратора,группа информационных входов которого соединена с первой группой выходов регистра, вторая группа выходовкоторого соединена с группой инфор 25 мационных входов второго дешифратора, управляющий вход которого соединен с управляющим входом третьегодешифратора, с первыми входами первого и второго элементов И, с входом30 синхронизации регистра и с первым. управляющим входом формирователя,третья группа выходов регистра соединена с информационным входомтретьего дешифратора, первая группа35 выходов которого соединена с первойгруппой входов элемента ИЛИ, вторая .группа входов которого соединена спервой группой выходов второго дешифратора, управляющий вход первого40 дешифратора соединен с вторым управляющим входом формирователя, первыйвыход регистра соединен с вторымвходом второго элемента И и с выходом конца команды формирователя,первая и вторая группы управляющихвыходов формирователя соединены соответственно с второй группой выходов второго дешифратора и с второйгруппой выходов третьего дешифратора, первый, второй, третий, четвер 50 тый и пятый выходы третьей группыуправляющих выходов формирователясоединены соответственно с выходомвторого элемента И, с вторым, третьим, четвертым и пятым выходами ре 55 гистра, шестой выход регистра соеди.нен с вторым входом первого элемента И и с первым выходом четвертойгруппы управляющих выходов формирователя, второй и третий выходы чет 60 вертой группы управляющих выходовкоторого соединены соответственно свыходом первого элемента И и сседьмым выходом регистра, первый,второй и третий выходы пятой группы управляющих выходов формировате 1070557 12ля соединены соответственно с вторым выходом первого дешифратора, с третьим выходом первого дешифратора и с восьмым выходом регистра, четвертая, пятая и шестая группы выходов которого соединены соответственно с группой выходов кода операций формирователя, с группой выходовуправления коммутатором индексовформирователя и с группой выходовполя кодов логических условий формирователя, девятый и десятый выходы регистра и выход элемента ИЛИ соединены соответственно с выходом разрешения внешнего доступа к оперативному запоминаюцему устройству формирователя, с выходом конца работы процессора и выходом прерывания формирователя, информационный вход регистра соединен с информационным входом. формирователя,На фиг. 1 приведена функциональная схема предлагаемого микропрограммного процессора; на фиг. 2 - тоже, формирователя микроопераций; нафиг. 3 - то же, коммутатора данных; на фиг. 4 - то же, коммутатора индексов; на фиг. 5 - то же, коммутатора управления оперативным запоминающим устройством; на фиг. б - то же, мультиплексора логических условий; на Фиг. 7 - то же, операционного блока; на фиг. 8 - 12 - схемы алгоритмов формирования исполнительного адреса второго операнда для команд форматов к Х 1 - РХ 5 соответственно.Микропрограммный процессор содержит блок 1 памяти команд, блок 2 памяти микрокоманд, блок 3 оперативного запоминаюцего устройства,блок 4 Формирования исполнительного адреса регистров общего назначения, формирователь 5 микроопераций, блок б индексных счетчиков, блок 7 счет,чиков циклов, блок 8 формирования исполнительного адреса оперативной памяти операционный блок 9, мультиплексор 10 логических условий, коммутатор 11 адреса микрокоманд, первый коммутатор 12 операнда, второй коммутатор 13 операнда, коммутатор 14 индексов, коммутатор 15 адреса оперативной памяти, коммутатор 16 блока формирования исполнительногоадреса, коммутатор 17 управления оперативным запоминаюцим устройством, коммутатор 18 данных, группу входов 19 константы процессора, блок 20 пуска-останова, генератор 21 тактовых импульсов, регистр 22 адресации первого операнда, регист 23 адресации второго операнда, регистр 24 адреса микрокоманд, регистр 25 исполнительного адреса, регистр 26 приращений, счетчики 27 индексов, счетчик,28 команд, счетчики 29 циклов, сумматор 30, триггер 31 блока пуска-останова, первый блок. элементов И 32 ивторой блок элементов И 33 блокаформирования исполнительного адресарегистров общего назначения, элементИ 34 блока пуска-останова, второйэлемент ИЛИ 35, первый элементИЛИ 36, блок 37 элементов И, шину38 команд, внутреннюю шину 39 данных, внешнюю шину 40 данных, информационную шину 41, управляющий вход42 процессора, вход 43 пуска, группу информационных входов 44 процессора, группу адресных входов 45 процессора, группу информационных входов-выходов 46 внешних данных, выход 47 разрешения внешнего доступак оперативному запоминающему устройству, выход 48 конца работы процессора и выход 49 прерывания.20 Выходами формирователя 5 микроопераций Фиг. 2/ являются выход 50конца команды, вторая группа управляющих выходов 51, выход 52 управления коммутатором индексов 52, пер 25 вый 53, второй 54, третий 55, четвертый 56 и пятый 57 выходы третьейгруппы управляющих выходов, перваягруппа управляющих выходов 58, первый59, второй 60, третий 61 выходы чет 30 вертой группы управляющих выходов,группа выходов 62 кода операций,первый 63, второй 64 и третий 65 выходы пятой группы управляющих выходов, выход бб разрешения внешнегоЗ 5 доступа к оперативному запоминаюцему устройству, выход 67 конца работы процессора, группа выходов 68 логических условий, второй 69 и первый70 управляюцие выходы.40 формирователь 5 микрооперацийсодержит регистр 71, третий 72,второй 73 и первый 74 дешифраторы,первый 75 и второй 76 элементы И,элемент ИЛИ 77.Коммутатор 18 данных (фиг. 3)включает коммутатор 78, элементНЕ 79, первый 80, второй 81 и третий82 блоки элементов И.Коммутатор 14 индексов (фиг. 4)содержит коммутатор 83, дешифратор84 и элемент ИЛИ-НЕ 85,Коммутатор 17 управления оперативным запоминаюцим устройствомПроцессор предназначен для вы" полнения команд форматов "регистр- регистр" (РР ) и "регистр - память" (ЙХ). Формат команды РР содержит по.- ля: код операции, адрес первого операнда (Р 1), адрес второго операнда (Р 2), а команды РХ - код операции, адрес первого операнда (Й 1) и сме, щение (О) .В обоих форматах адрес первого операнда Р 1 задает номер регистра общего назначения в блоке 92 регистров общего назначейия операционного блока 9 (фиг. 7). Смещение 3 задает адрес первого числа в режимах прямой адресации (адресации с индексацией).Данные, обрабатываемые процессо-ром, храняться в блоке 3 оперативной памяти, а программа смещения, исполнительные адреса, индексы, начальные адреса подпрограмм и дополнения счетчиков циклов (до записи их в соответствующие счетчики) - в блоке 1 памяти команд.Команды формата РХ могут быть пяти типов, зависящих от режимов адресации данных в памяти.В предлагаемом процессоре предусмотрено пять режимов адресации данных для РХ-команд:прямая адресация, когда исполнительный адрес данных А; формируется на основе информации о смещении 2;, считываемой из блока 1 памяти команд по формулеА,= Э., (е 1 нгце И - мощность множества исполнительных .адресов;индексная адресация с продвижением индекса, когда исполнительный адрес формируется на основе значения индекса 7 Р и смещения в соответ. ствии с ФормулойА =ЗРР, 7 Р=7 Р+/;индексная адресация без продвижения индекса, когда исполнительный адрес формируется на основе соотношенияА,:ЗРЭ;и ндексная адресация с постоянным шагом приращения д ( д ) 1 ) индекса, когда исполнительный адрес формируется в соответствии с формулойА.Я,. Ч, Е 2, й; А. =А. д, д=сопЮ;индексная адресация с переменнымшагом д = д; ); (1 е ),и ) приращения индекса, когда исполнительный адрес формируется по формулеА=О, А,=) м,. е 2, к: А.=А, +д, д, =д (1) Указанным режимам. адресации соответствуют команды типов Р Х 1 - 1 Х 5Общая характеристика адресации впроцессоре.состоит в следующем.При выполнении команд ФорматаРР адреса первого (Р 1) и второго(Р 2) операндов поступают через блок4 формирования исполнительного адреса для регистров общего назначенияна группу адресных входов операционного блока 9. Кодом операции командыопределяется начальный адрес микропрограммы выполнения данной команды,при этом код операции команды с выхода блока 1 через шину 38 команд и 15 коммутатор 11 адреса микрокоманд записывается в регистр 24 адреса микрокоманд, по которому микрокоманда выбирается из блока 2 и записываетсяблок 520 При выполнении команд формата РХадрес первого операнда Р 1 через блок4 подается на соответствующие разряды группы адресных входов операционного блока 9. Формирование адреса второго операнда осуществляетсясложнее и существенно зависит от типа команды.При выполнении команды типа Р Х 1( фиг. 9 ) исполнительный адрес второго 3(1 операнда задается смешением Р вФормате команды. Этот адрес передается через коммутаторы 14 и 16 в регистр 25 исполнительного адреса, покоторому осуществляется адресацияблока 3 оперативного запоминающегоустройства.В блоке 3 по адресу, заданному врегистре 25, может производиться за;пись или считывание в соответствиис исполнительной командой и опреде О ляемые сигналами на выходах 60 и 61формирователя 5 микрооперацийКоманды типа Р Х 2 предназначены дляорганизации так называемой "магаэиннойф обработки данных, когда адрес следующего числа на единицу. больший предыдущего. РХ 2 - командыпозволяют обрабатывать массивы данных. При этом загрузка индексов всчетчики 27 индексов производится 50 заранее соответствующими командамииз блока 1 памяти команд, в полекоторых указывается загружаемый кодв счетчике 27 индексаИсполнительный адрес очередного 55. числа массива данных в этом случаеФормируется следующим образом.Смещение Э во время выборки командного слова в последнем циклевыполнения предыдущей команды через 60 коммутаторы 14 и 16 с выхода блока1 записывается в регистр 25. В следукщем цикле первом цикле исполнения данной команды )индекс с выходсчетчика 27 индекса через коммутатор 14 записывается в регистр 26

СмотретьЗаявка

3492809, 16.09.1982

ПРЕДПРИЯТИЕ ПЯ А-7160

СУПРУН ВАСИЛИЙ ПЕТРОВИЧ, КРИВОНОСОВ АНАТОЛИЙ ИВАНОВИЧ, КОРНИЕНКО ИВАН ИОСИФОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропрограммный, процессор

Опубликовано: 30.01.1984

Код ссылки

<a href="https://patents.su/21-1070557-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор</a>

Предыдущий патент: Устройство для контроля последовательности импульсов

Следующий патент: Узел резистивной сеточной модели

Случайный патент: Аналоговое запоминающее устройство