Устройство для синхронизации и декодирования фазокодированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 664191

Авторы: Григорьев, Серебряков, Сухарев, Телегов, Ушаков

Текст

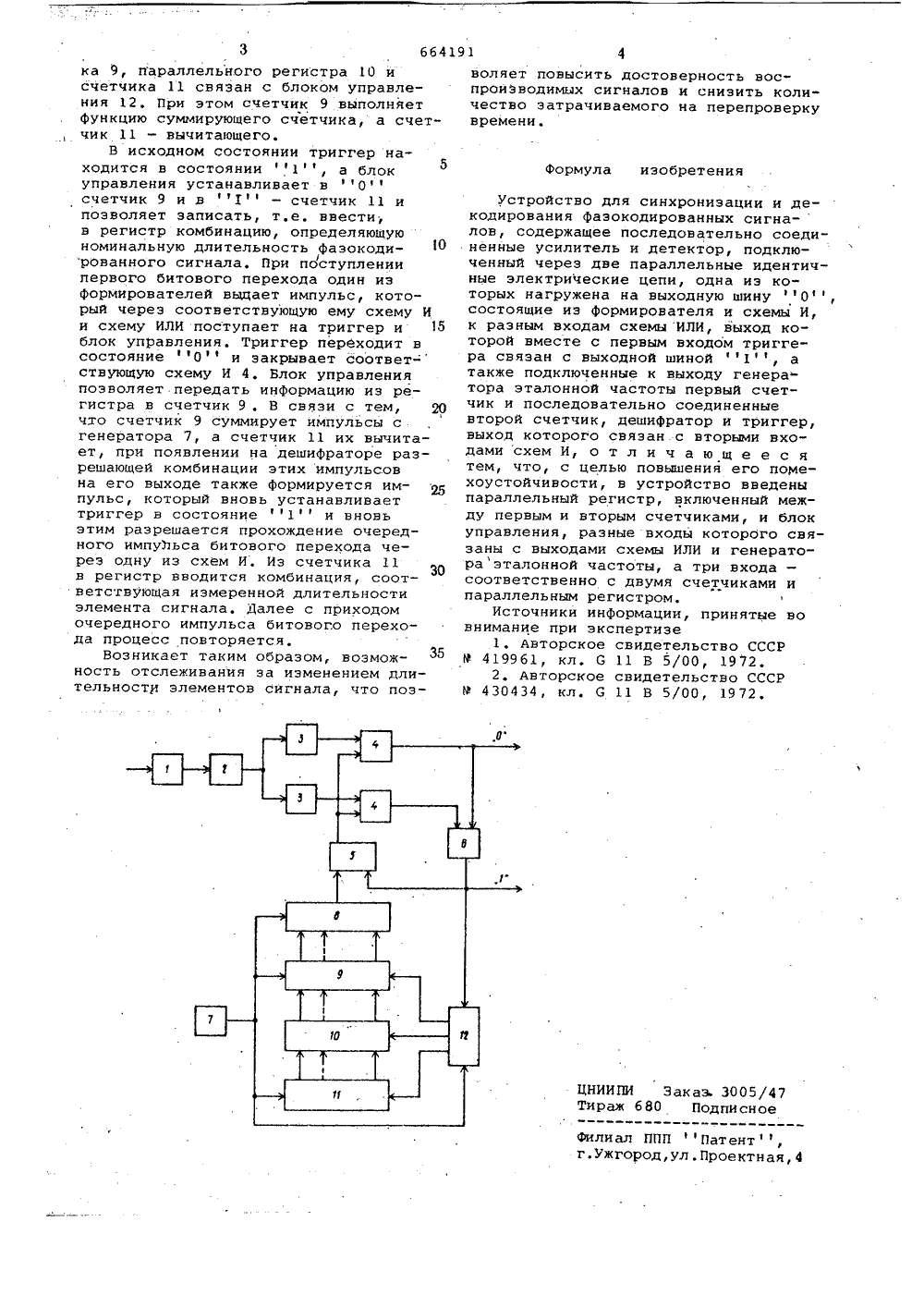

(54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ И ДЕКОДИРОВАНИЯ фАЗОКОДИРОВАННЫХ СИГНАЛОВ Изобретение относится к приборостроительной промышленности и может .быть использовано в аппаратуре магнитной записи,5 Известно устройство, предназначенное для синхронизации и декодирования,используемое в аппаратуре магнитнойзаписи, выполненное с блоком формиро-вания импульсов, усилителем и рядомлогических схем, включенных в разныеканалы 11).При наличии флуктуаций границ элементов фазокодированного сигналаустройство оказывается недостаточнонадежным в работе,Наиболее близким по техническому решению к предлагаемому является устройство для синхронизации и декодирования фазокодированных сигналов, содержащее последовательно соединенные усилитель и детектор, подключенный через две параллельные идентичные электрические цепи, одна иэ которых нагружена на выходную шину О состоящие из формИрователя и схемы И, к разным входам схемы ИЛИ, выход которой вместе с первым входом триггера связан с выходной шиной 1 , а ЗО также содержащее подключенные к выходу генератора эталонной частоты первый счетчик и последовательно соединенные второй счетчик, дешифратор и триггер, выход которого связан с вторыми входами схем И 2.Недостатком этого устройства является относительно невысокая помехоустойчивость.Цель изобретения - повышение помехоустойчивости устройства для синхронизации и декодирования фазокодированных сигналов.Поставленная цель достигается тем, что в устройство введены параллельный регистр, включенный между первым и вторым счетчиками, и блок управления, разные входыкоторого связаны с выходами схемы ИЛИ и генератора эталонной частоты, а три входа - соответственно с двумя счетчиками .и параллельным регистром.На чертеже представлена структурная схема предлагаемого устройства,Усилитель 1, соединенный с детектором 2, через формирователи 3 и схемы И 4, вторые входы которых связаны с триггером 5, подключен к схеме ИЛИ ь, а генератор эталонной частоты 7 с помощью дешифратора 8 счетчи664191 лиал ППППатентУжгород,ул. Проектна ка 9, параллельного регистра 10 исчетчика 11 связан с блоком управления 12. При этом счетчик 9 выполняетфункцию суммирующего счетчика, а счетчик 11 - вычитающего,В исходном состоянии триггер находится в состоянии 1, а блокуправления устанавливает в 0счетчик 9 и в 1 - счетчик 11 ипозволяет записать, т,е. ввести,в регистр комбинацию, определяющуюноминальную длительность фазокоди- фрованного сигнала. При поступлении/первого битового перехода один изформирователей выдает импульс, который через соответствующую ему схему Ии схему ИЛИ поступает на триггер и 15блок управления. Триггер переходит всостояние 0 и закрывает соответ-ствующую схему И 4. Блок управленияпозволяет передать информацию иэ регистра в счетчик 9 . В связи с тем, 20что счетчик 9 суммирует импульсы сгенератора 7, а счетчик 11 их вычитает, при появлении на дешифраторе разрешающей комбинации этих импульсовна его выходе также формируется импульс, который вновь устанавливаеттриггер в состояние 1 и вновьэтим разрешается прохождение очередного импульса битового перехода через одну из схем И. Из счетчика 11в регистр вводится комбинация, соответствующая измеренной длительностиэлемента сигнала, Далее с приходомочередного импульса битового перехода процесс повторяется,Возникает таким образом, возможность отслеживания за изменением длительности элементов сигнала, что позволяет повысить достоверность воспроизводимых сигналов и снизить количество затрачиваемого на перепроверкувремени. Формула изобретения Устройство для синхронизации и декодирования фаэокодированных сигналов, содержащее последовательно соединенные усилитель и детектор, подключенный через две параллельные идентичные электрические цепи, одна иэ которых нагружена на выходную шину 0, состоящие из формирователя и схемы И, к разным входам схемы ИЛИ, выход которой вместе с первым входом триггера связан с выходной шиной 1, а также подключенные к выходу генера тора эталонной частоты первый счетчик и последовательно соединенные второй счетчик, дешифратор и триггер, выход которого связан с вторыми входами схем И, о т л и ч а ю щ е е с я тем, что, с целью повышения его поМехоустойчивости, в устройство введены параллельный регистр, включенный между первым и вторым счетчиками, и блок управления, разные входы которого связаны с выходами схемы ИЛИ и генератора эталонной частоты, а три входа - соответственно с двумя счетчиками и параллельным регистром.Источники информации, принятые во внимание при экспертизе1, Авторское свидетельство СССР М 419961, кл. С 11 В 5/00, 1972,2. Авторское свидетельство СССР Р 430434, кл, С 11 В 5/00, 1972,ЦНИИПИ Заказ 3005/4 Тираж 680 Подписное

СмотретьЗаявка

2514297, 01.08.1977

ВОЕННАЯ ОРДЕНА ЛЕНИНА КРАСНОЗНАМЕННАЯ АКАДЕМИЯ СВЯЗИ ИМ. С. М. БУДЕННОГО, ПРЕДПРИЯТИЕ ПЯ А-1116

ГРИГОРЬЕВ ВЯЧЕСЛАВ АЛЕКСАНДРОВИЧ, СЕРЕБРЯКОВ СЕРГЕЙ АРТЕМОВИЧ, СУХАРЕВ СЕРГЕЙ ЛЕОНИДОВИЧ, УШАКОВ ЛЕВ ВЛАДИМИРОВИЧ, ТЕЛЕГОВ ЮРИЙ ФЕДОРОВИЧ

МПК / Метки

МПК: G11B 5/06

Метки: декодирования, сигналов, синхронизации, фазокодированных

Опубликовано: 25.05.1979

Код ссылки

<a href="https://patents.su/2-664191-ustrojjstvo-dlya-sinkhronizacii-i-dekodirovaniya-fazokodirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для синхронизации и декодирования фазокодированных сигналов</a>

Предыдущий патент: Устройство для записи и воспроизведения цифровой информации

Следующий патент: Устройство для воспроизведения сигналов с магнитного носителя

Случайный патент: Стереоскопическая насадка к однообъективнойкамере