Устройство для синхронизации контрольного и эталонного цифровых сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 668081

Автор: Курилов

Текст

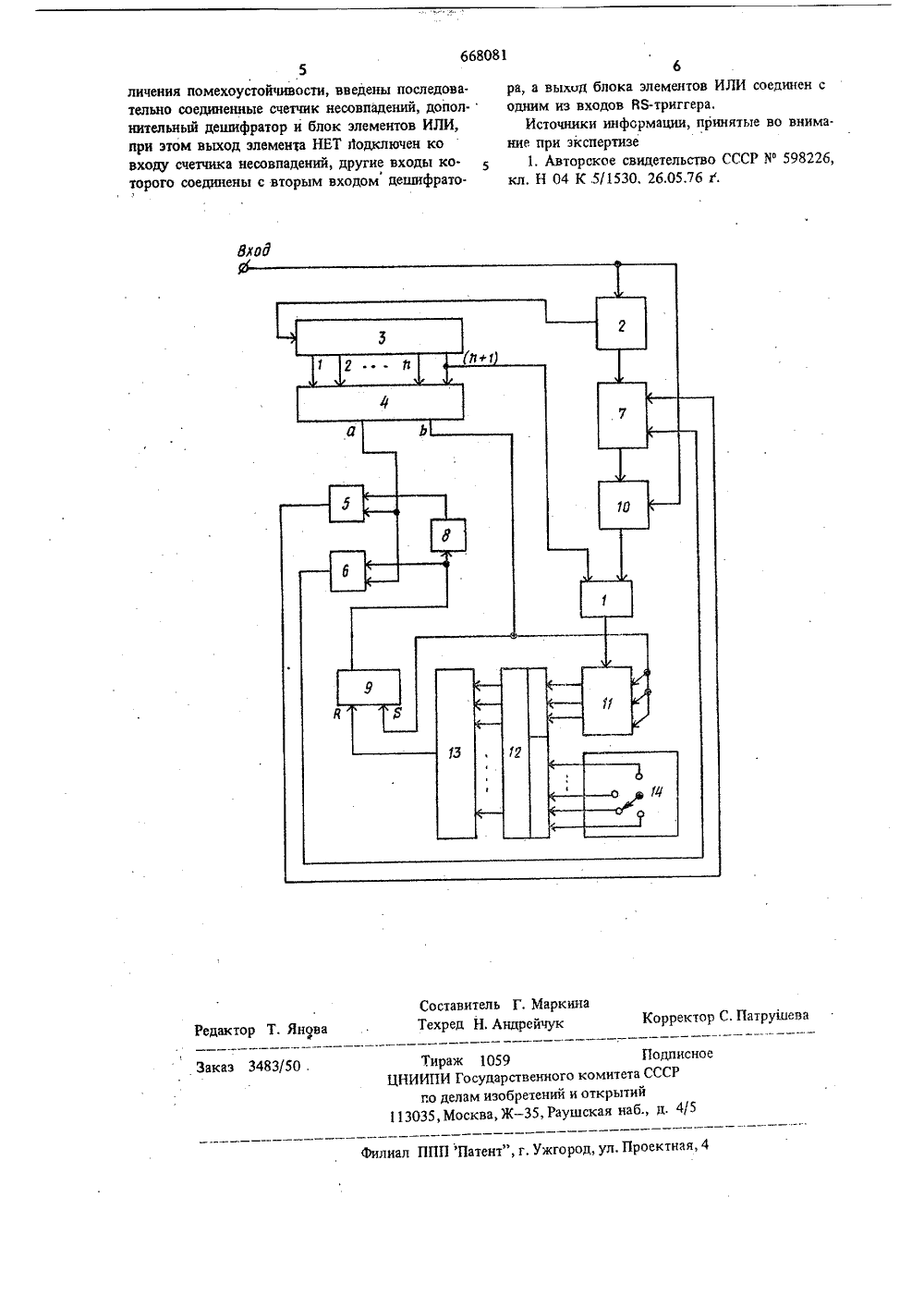

с бои."1 ыАР 1и,О П И С А Н И Е (1668081ИЗОБРЕТЕН ИЯ Союз Советеимн Соцналистическин Республик(61) Дополнительн (22) ЗаявлЕно 17.10 вт, свиа-ву Мо 59822621) 25 34129/18-09 М.Н 0 К 5/1531 7/02 присоединением заявкиовудврвтввнный номптвт СССР но двяам изобрвтвннй н открытий(53) УДК621 316 729 621 .394.662 (088,8) Дата опубликован исання 15,0 2) Автор изобретения, Курило Заявитель 4) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ КОНТРОЛЬНОГО И ЭТАЛОННОГО ЦИФРОВЫХ СИГНАЛОВотносится к технике связи и моься при создании контрольно.иэаратуры для систем цифровой Изобретение жет использов мерительной а м второго элемента лемент НЕ - с вто. ра соединен с вторым вхо И непосредственно и чере стно уст.о пэта-е элемент,вход косигнала,й частоов, вы- ючены тройств инхр нто изации си н зло в ния так. ен к шине ольного и эталонного цифровых ащее элемент НЕТ, блок выделе частоты, вход которого подклю ольного сигнала, первый выход б я тактовой частоты соединен с в ер т алов,оду б одержоной ока вы одомэлем конт ыход ков, выходы которого через дечены к первым входам первосчетчика импульсо шифратор подклю го и второго элем мента И соединен эталонных сигнало ключен к выходу ентак последход эчсВЯ-триг. торо му .трип с. ентов И, выход второго эл с первым входом генерато в, второи вход которого подблока выделения тактовой связи.По основному авт. св, У 598226 изве ройстно для синхронизации контрольног лонного цифровых сигналов, содержаше НЕТ, блок выделения тактовой частоты торого подключен к шине контрольного первый выход блока выделения тактово ты соединен с входом счетчика импульс ходы которого через дешифратор подкл к первым входам первого и второго эл И, выход второго элемента И соединен вым входом генератора эталонных сигн второй вход которого подключен к вых ка выделения тактовой частоты, а такж НЕ, ВЯ.триггер и блок несовпадении, в торого соединен с первым входом элем НЕТ, второй вход которого полключен нему разряду счетчиа импульсов, а вь мента НЕТ соединен с одним иэ входи гера, а его другой вход подключен к в выходу деитифратора, причем выход ВВ рым входом первого элемента И, выход которого подключен к третьему входу генератора эта.лонных сигналов, выход последнего соединен с первым входом блока несивход этого блока подключеного сигнала 1.Однако данное устройство имеет невысокуюпомехоустойчивость.Цель изобретения - увеличение помехоусточивости,Для этого в ус о для с он668081 ЕЩд 3частоты а также элемент НЕ, ЯЗ-триггер и блокнесовпадений, выход которого соединен с первымвходом элемента НЕТ, второйвход которого лодключен к последнему разряду счетчика импульсов, а выход элемента НЕТ соединен с одним из5входов ЙЗ-триггера, другой вход которого под.ключен ко второму выходу дешифратора, причемвыход ЯЗ-триггера соединен со вторым входомвторого элемента И непосредственно и черезэлемент НЕ со вторым входом первого элемента 10И, выход которого подключен к третьему входугенератора эталонных сигналов, выход которогосоединен с первым входом блока несовпаде.ний, второй вход которого подключен к шинеконтрольного сигнала, введены последовательно 15.соединенные счетчик несовпадений, дополнитель.ный дешифратор и блок элементов ИЛИ, приэтом выход элемента НЕТ подключен ко входу сче 1 чика несовпадений, другие входы кото.рого соединены с вторым входом дешифратора, а выход блока элементов ИЛИ соединен содним из входов ЙЗ.триггера.На чертеже изображена структурная электрическая схема предложенного устройства,Устройство для синхронизации контрольного 25и эталонного цифровых сигналов содержит эле.мент НЕТ 1, блок вьщеления 2 тактовой частоты, счетчик 3 импульсов, дешифратор 4, элементы И 5 и 6, генератор 7 эталонных сигналов,элемент НЕ 8, ЯЗ-триггер 9, блок несовпадений 3010, счетчик 11 несовпадений, дополнительныйдешифратор 12, блок элементов ИЛИ 13 и переключатель 14.Предложенное устройство работает следующимобразом. 35Контрольный сигнал поступает на блок выделения 2 и в блок несовпадений, 10, где он срав.нивается с эталонным сигналом той же структуры, вырабатываемым генератором 7, Выявленные несовпадения подсчитываются счетчиком 11 40в течение щи тактов, пока состояние последнего (п+1)-го разряда счетчика 3 разрешает про.хождение несовпадений через элемент НЕТ 1.Переключатель 14 обеспечивает считываниесостояния счетчика 11, соответствующего вы 45бранной кратности ошибки, Когда количествонесовпадений, подсчитываемых счетчиком 11,достигает выбранного значения, на соответствующем выходе дополнительного дешифратора 12появляется импульс, который, пройдя через 50блок элементов ИЛИ 13, переворачивает ВЗ-триг.гер 9 в положение, символизующее несовпаде.ние контрольного и эталонного сигналов по фаэе. Соответственно при количестве несовпадений на щи тактов меньше выбранного значения 55ВЗ.триггер 9 остается в исходном "нулевом"состоянии, символизирующем совпадение пофазе контрольного и эталонного сигналов, т.е.окончание синхронизации. 4При состоянии (и + 1) го разряда счетчика3, запрещающего подсчет несовпадений счетчиком 11, осуществляются следующие операции.Считывание состояний ЯЗ-триггера 9 черезэлементы И 5 и 6 импульсом с выхода деши.фратора 4. Последующее обнуление ВЗ-триггера9 и счетчика 11 для последующего цикла син.хронизации. Обнуление осуществляется подачейс выхода дешифратора 4 импульса йа входВЗ-триггера 9 и вход "установки нуля" счет.ика 11, Импульс "обнуления" подается с такойзадержкой относительно импульса "считывания",что считывание состояний ЯЗ-триггера 9 являет.ся устойчивым,При считывании состояния ВЗ.триггера 9,символизирующего несовпадение по фазе конт.рольного и эталонного сигналов, на выходеэлемента И 5 формируется импульс, поступле.ние которого в генератор 7 обеспечивает сдвигэталонной последовательности относительно контрольной на такт, после чего производится повторное сравнение последовательностей.Поэлементный сдвиг осуществляется по достижении совпадения по фазе контрольного иэталонного сигналов. В том случае, если коли.чество ошибок, поразивших контрольную по.следовательность в сравниваемых щи тактах, непревысит заранее выбранного, то ВЗтриггер 9остается в "нулевом" состоянии, при считыва.нии которого импульс формируется на выходеэлемента И б. Этот импульс поступает в генератор 7, обеспечивай отключение устройствасинхронизации до подачи новой команды отоператора. Емкость счетчика 3 выбирается таким обра. зом, что минимальное кодовое расстояние (ь) между фрагментами измерительных носледова. тельностей щи является дЬстаточным для исправления ошибки выбранной кратности (д), при чем Для псевдослучайных последовательностей ти.па М, где М = щк.1, емкость счетчика 3 можноопределитьдля кольцевого счетчикаи) К+щддля двоичного счетчикаи ) 1 оцг (К + щд)При использовании предложенного устройет.ва увеличивается помехоустойчивость,Формула изобретения Устройство для синхронизации контрольного и эталонного цифровых сигналов по авт.св.МО 598226,о т л и ч а ю щ е е с я тем, что, с целью уве.66808 ВхРд Составитель Г, МаркинТехред Н. Андрейчук едактор Т. Янов Корректор С. Патрушева Заказ 3483/50 . Подписноениого комитета СССРтений и открытий5, Раушская наб., д, 4/5 Тираж 1059 НИИПИ Государстго делам изобр 13035, Москва, Жлиал ППП Патент", г, Ужгород, ул. Проектная, 4 5личения помехоустойчивости, введены последовательно соединенные счетчик несовпадений, допол-нительный дешифратор и блок элементов ИЛИ, при этом выход элемента НЕТ Подключен ко входу счетчика несовпадений, другие входы которого соединены с вторым входом дешифрато 16ра, а вьиод блока элементов ИЛИ соединен содним из входов ВБ-триггера.Источники информации, принятые во внима.ние при экспертизе1. Авторское свидетельство СССР У 598226,кл. Н 04 К 5/1530. 26.05.76 г.

СмотретьЗаявка

2534129, 17.10.1977

ПРЕДПРИЯТИЕ ПЯ Р-6609

КУРИЛОВ АНДРЕЙ ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: H03K 5/153

Метки: контрольного, сигналов, синхронизации, цифровых, эталонного

Опубликовано: 15.06.1979

Код ссылки

<a href="https://patents.su/3-668081-ustrojjstvo-dlya-sinkhronizacii-kontrolnogo-i-ehtalonnogo-cifrovykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для синхронизации контрольного и эталонного цифровых сигналов</a>

Предыдущий патент: Устройство для трансформации длительности импульса

Следующий патент: Способ частотной селекции импульсов

Случайный патент: Способ настройки фрез при планетарном фрезеровании